嵌入式平臺(tái)NVMe驅(qū)動(dòng)設(shè)計(jì)與應(yīng)用

馮軍波

(中航工業(yè)西安航空計(jì)算技術(shù)研究所,陜西西安,710068)

0 引言

NVMe(Non-Volatile Memory express,非易失存儲(chǔ)器協(xié)議)是一種面向PCIe固態(tài)硬盤(SDD)的接口協(xié)議。最早于在2011年3月推出,由NVMe規(guī)范組織成員公司(如Intel、戴爾、三星、鎂光等)合作開(kāi)發(fā),用于主控軟件通過(guò)PCIe 鏈路與SSD進(jìn)行高速數(shù)據(jù)傳輸。在最新的1.3版本中又增加了設(shè)備自檢、引導(dǎo)分區(qū)、虛擬化、主機(jī)操控散熱管理等新特點(diǎn),改進(jìn)了SSD的性能。在NVMe推出之前,傳統(tǒng)的SATA硬盤大都使用AHCI協(xié)議,讀寫(xiě)速度在500M/s以下。AHCI協(xié)議具有較強(qiáng)的兼容性,可支持SATA總線與PCIe總線,但是當(dāng)硬盤通過(guò)PCIe總線與處理器連接時(shí),AHCI協(xié)議無(wú)法為PCIe SDD提供最佳的性能。而NVMe的規(guī)劃充分利用了PCIe SSD的低延遲與并行性,兼顧處理器平臺(tái)架構(gòu),最大程度的發(fā)揮了SDD的高性能,讀寫(xiě)速度可超過(guò)1GB/s。本文描述了一種嵌入式飛騰4核CPU平臺(tái)下的NVMe固態(tài)硬盤驅(qū)動(dòng)設(shè)計(jì)和固態(tài)硬盤硬件實(shí)現(xiàn)。實(shí)驗(yàn)表明,該設(shè)計(jì)相較于之前的SATA固態(tài)硬盤極大的提高了數(shù)據(jù)的讀寫(xiě)速度,增強(qiáng)了存儲(chǔ)系統(tǒng)的性能。

1 系統(tǒng)組成

本系統(tǒng)的硬件環(huán)境主要包含兩部分,一個(gè)處理器模塊加一塊SSD,硬件設(shè)計(jì)的示意如圖1所示。其中的處理器模塊采用飛騰公司的FT2000-4,該處理器集成4個(gè)64位高性能核,最高主頻3.0GHz,設(shè)計(jì)中的工作主頻為1.0GHz,處理能力為16GIPS/Core@1GHz。

圖1 存儲(chǔ)系統(tǒng)邏輯結(jié)構(gòu)示意圖

該系統(tǒng)中的SSD是一種典型的SOC(System on Chip)單機(jī)系統(tǒng),模塊之間通過(guò)AXI高速和APB低速總線互聯(lián)互通,完成信息和數(shù)據(jù)的通信。SSD中還有固件(Firmware),用于調(diào)度各個(gè)硬件模塊,完成SSD產(chǎn)品所需要的功能,也包括數(shù)據(jù)從主機(jī)端到閃存端的寫(xiě)入和讀取。SSD內(nèi)部由PCIe GS9203主控制器芯片和Nand Flash陣列組成。PCIe主控芯片為28nm工藝,主控CPU具有兩個(gè) ARM Cortex R4 CP內(nèi)核,支持PCIe Gen3 x4和NVMe 1.3c協(xié)議標(biāo)準(zhǔn),有8個(gè)Flash通道, Flash芯片采用國(guó)產(chǎn)長(zhǎng)江存儲(chǔ)科技有限責(zé)任公司的TLC X1-9050 NAND FLASH,是中國(guó)首款64層3D NAND閃存。

2 NVMe驅(qū)動(dòng)設(shè)計(jì)

NVMe驅(qū)動(dòng)依據(jù)功能的不同,可劃分為驅(qū)動(dòng)接口模塊,初始化模塊和命令執(zhí)行模塊。其中命令執(zhí)行模塊為核心,設(shè)備初始化模塊涉及控制器初始化、數(shù)據(jù)存儲(chǔ)鏈表創(chuàng)建、命令隊(duì)列的設(shè)置,驅(qū)動(dòng)接口模塊用于處理上層文件系統(tǒng)對(duì)設(shè)備的訪問(wèn)。驅(qū)動(dòng)的架構(gòu)如圖2所示。

圖2 NVMe驅(qū)動(dòng)架構(gòu)圖

本系統(tǒng)中,主機(jī)端在上電后首先運(yùn)行天脈3嵌入式實(shí)時(shí)操作系統(tǒng),運(yùn)行過(guò)程中調(diào)用NVMe驅(qū)動(dòng)的初始化模塊,完成硬件和軟件的準(zhǔn)備工作。隨后在啟動(dòng)文件系統(tǒng)時(shí)將驅(qū)動(dòng)接口注冊(cè)到文件系統(tǒng)的IO函數(shù)中,最后應(yīng)用軟件調(diào)用文件操作函數(shù)時(shí)會(huì)調(diào)用到驅(qū)動(dòng)讀寫(xiě)接口。

■ 2.1 控制器初始化

NVMe控制器初始化的主要內(nèi)容是找到控制器,通過(guò)配置其內(nèi)部的寄存器使其就緒,并在主機(jī)端的內(nèi)存上創(chuàng)建命令隊(duì)列,創(chuàng)建數(shù)據(jù)緩沖鏈表,并完成MSI中斷的初始化和注冊(cè)。

2.1.1 NVMe寄存器配置

NVMe作為一種寄存器級(jí)別的接口連接到PCIe接口上,其寄存器配置包括PCIe寄存器配置和NVMe控制器寄存器配置。

PCIe寄存器配置主要是PCI header、和PCI Capabilities的配置。PCI header類型分為兩種,type0表示設(shè)備,type1表示橋。NVMe控制器屬于設(shè)備則定義為type0類型。當(dāng)系統(tǒng)完成PCIe的初始化且設(shè)備被掛到總線上時(shí),PCI header中的設(shè)備ID與廠商ID會(huì)有固定的值,該值是設(shè)備的唯一標(biāo)識(shí)。基地址寄存器會(huì)寫(xiě)有地址值,該值作為訪問(wèn)設(shè)備其他寄存器的基址。設(shè)備各項(xiàng)功能的設(shè)置是通過(guò)功能指針寄存器來(lái)完成的。功能指針寄存器所指向的是位置是配置寄存器組鏈表的第一個(gè)條目[1]。常用的能力設(shè)置包括對(duì)NVMe控制器的電源管理、中斷管理(包括MSI、MSI-X)的設(shè)置,設(shè)置完之后再配置命令寄存器使能設(shè)備。

NVMe控制器寄存器的設(shè)置主要是對(duì)表1中所列舉的寄存器進(jìn)行賦值,寄存器描述見(jiàn)表1。

表1 NVMe控制器寄存器功能描述表

2.1.2 NVMe隊(duì)列創(chuàng)建

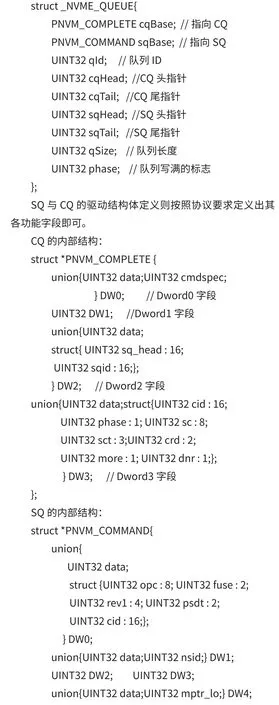

NVMe命令隊(duì)列按照類型可以分為Admin命令隊(duì)列與I/O命令隊(duì)列,讀寫(xiě)電子盤通常使用IO隊(duì)列。NVMe協(xié)議針支持多達(dá)65535個(gè)IO命令隊(duì)列,每一個(gè)隊(duì)列可容納64K 條命令。IO命令隊(duì)列按照用途不同可分為命令提交隊(duì)列SQ和命令完成隊(duì)列CQ。SQ隊(duì)列中一條命令的內(nèi)容包括操作碼、ID、要操作盤的起始?jí)K號(hào)、塊數(shù)量、數(shù)據(jù)所在的緩沖等。CQ隊(duì)列中的一條命令包括下一條命令位置、下一條命令I(lǐng)D當(dāng)前命令I(lǐng)D、當(dāng)前命令狀態(tài)等。一個(gè)隊(duì)列即是主機(jī)端內(nèi)存上的一段連續(xù)的環(huán)形緩沖,在初始化NVMe時(shí)向系統(tǒng)申請(qǐng)內(nèi)存空間,然后將空間的基地址控制器的ASQ寄存器與ACQ寄存器。每一個(gè)隊(duì)列都有對(duì)應(yīng)QID、虛擬地址、物理地址、長(zhǎng)度、頭指針、尾指針和相應(yīng)的門鈴寄存器。本驅(qū)動(dòng)定義了隊(duì)列信息結(jié)構(gòu)如下:

命令隊(duì)列在多核處理器上可采用兩種設(shè)計(jì)方法,一種是一個(gè)核上安排一個(gè)SQ與一個(gè)CQ。另一種為一個(gè)核上安排一個(gè)CQ多個(gè)SQ。本驅(qū)動(dòng)運(yùn)行在一個(gè)核上,采用第一種方式。隊(duì)列通過(guò)對(duì)應(yīng)的門鈴寄存器,在host與控制器間傳遞消息。

2.1.3 創(chuàng)建數(shù)據(jù)緩沖表

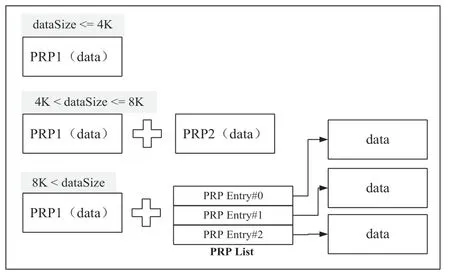

NVMe的數(shù)據(jù)尋址方式包括物理頁(yè)表(PRP)和分散聚合表(SGL),本驅(qū)動(dòng)設(shè)計(jì)采用PRP方式。PRP表中的每一項(xiàng)是一個(gè)64位指針,格式為頁(yè)地址+頁(yè)內(nèi)偏移,每一項(xiàng)指向一個(gè)內(nèi)存頁(yè),頁(yè)的大小在CC寄存器中定義,通常一頁(yè)的大小為4KB,因此在進(jìn)行數(shù)據(jù)傳輸時(shí),有時(shí)會(huì)要求數(shù)據(jù)緩沖的起始地址須4KB對(duì)齊。

命令的Dword6~Dword9定義了PRP1、PRP2兩個(gè)指針,通過(guò)PRP2可以指向PRP List。PRP算法根據(jù)數(shù)據(jù)的長(zhǎng)度有三種模式,如圖3所示。

圖3 數(shù)據(jù)緩沖PRP示意圖

當(dāng)數(shù)據(jù)小于等于4KB時(shí)只需將PRP1指向數(shù)據(jù)所在的地址即可;若數(shù)據(jù)大于4KB小于等于8KB則須將PRP1指向數(shù)據(jù)所在的地址,PRP2指向數(shù)據(jù)所在地址加上4K位置;若數(shù)據(jù)大于8K,則需將PRP1指向數(shù)據(jù)所在地址,PRP2指向PRP List。

■ 2.2 命令執(zhí)行過(guò)程

NVMe命令按照類型可以分為Admin命令與I/O命令。Admin命令主要負(fù)責(zé)管理NVMe控制器,IO命令負(fù)責(zé)操作固態(tài)硬盤,常用的Admin命令包括identify、創(chuàng)建SQCQ、刪除SQCQ。常用的IO命令包括Read 、Write、Flush。

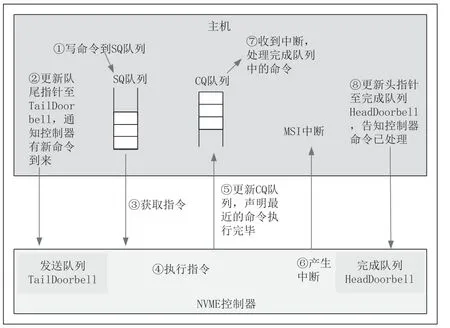

圖4為NVMe 命令執(zhí)行過(guò)程。主機(jī)寫(xiě)命令道SQ隊(duì)列,通過(guò)TailDoorbell通知NVMe控制器,控制器獲得命令并執(zhí)行,將命令寫(xiě)入CQ隊(duì)列(無(wú)論命令是否執(zhí)行成功),產(chǎn)生中斷提醒主機(jī)命令已完成。主機(jī)處理CQ中的命令信息,最后更新HeadDoorbell告知控制器命令已處理。

圖4 NVMe命令執(zhí)行過(guò)程示意圖[3]

為解決多任務(wù)對(duì)共享資源的互斥訪問(wèn),在寫(xiě)命令到SQ后,提交命令的任務(wù)應(yīng)先等待資源可用的信號(hào)量,待控制器執(zhí)行完一條命令后會(huì)向主機(jī)發(fā)出MSI中斷,主機(jī)在MSI中斷服務(wù)函數(shù)中處理完成隊(duì)列,最終釋放資源信號(hào)量。

3 NVMe驅(qū)動(dòng)應(yīng)用

本驅(qū)動(dòng)應(yīng)用于某軍用飛機(jī)的數(shù)據(jù)共享系統(tǒng),為其中的數(shù)據(jù)庫(kù)管理軟件提供存儲(chǔ)服務(wù)。操作系統(tǒng)為國(guó)產(chǎn)自主可控的天脈3多分區(qū)RTOS,使用場(chǎng)景如圖5所示。

圖5 NVMe驅(qū)動(dòng)應(yīng)用場(chǎng)景示意圖

在天脈3核心OS啟動(dòng)過(guò)程中完成NVMe控制器的初始化、命令隊(duì)列以及數(shù)據(jù)緩沖PRP表的創(chuàng)建工作,隨后將驅(qū)動(dòng)接口注冊(cè)到文件系統(tǒng)中。當(dāng)分區(qū)應(yīng)用數(shù)據(jù)庫(kù)管理軟件中的任務(wù)使用標(biāo)準(zhǔn)IO進(jìn)行文件操作時(shí),由文件系統(tǒng)調(diào)用驅(qū)動(dòng)的接口模塊實(shí)現(xiàn)對(duì)NVMe電子盤的讀寫(xiě)訪問(wèn)。本設(shè)計(jì)中NVMe驅(qū)動(dòng)最大支持單次DMA傳輸512KB數(shù)據(jù),當(dāng)數(shù)據(jù)大于512KB時(shí),驅(qū)動(dòng)會(huì)將數(shù)據(jù)以512KB為單位分割,進(jìn)行多次傳輸。在PCIe3.0接口4x下進(jìn)行讀寫(xiě)速度測(cè)試,測(cè)量數(shù)據(jù)如圖6所示。

圖6 NVMe驅(qū)動(dòng)讀寫(xiě)電子速度圖

從實(shí)驗(yàn)結(jié)果可知,當(dāng)數(shù)據(jù)量很小時(shí),讀寫(xiě)速度也較慢,在數(shù)據(jù)量接近或大于設(shè)備支持的單次最大處理的字節(jié)數(shù)512KB時(shí),讀寫(xiě)速度穩(wěn)定在1000MB/s上下,驅(qū)動(dòng)表現(xiàn)出良好的性能。

4 結(jié)束語(yǔ)

NVMe協(xié)議定義了基于PCIe的SSD的寄存器接口、命令集合與功能集合,通過(guò)PCIe接口將I/O命令和響應(yīng)映射到主機(jī)中的共享內(nèi)存。相較于SATA或AHCI協(xié)議,NVMe接口支持與多核處理器的并行I/O,實(shí)現(xiàn)高吞吐量,緩解了CPU瓶頸。NVMe電子盤帶來(lái)高速的讀寫(xiě)能力時(shí),相比SAS和SATA電子盤在價(jià)格上就更昂貴一些,而且消耗的功率可能也會(huì)增加,同時(shí)在容量方面不及普通硬盤最大只有4TB,不過(guò)在很多高性能領(lǐng)成為好的選擇。本文實(shí)現(xiàn)的國(guó)產(chǎn)嵌入式實(shí)時(shí)操作系統(tǒng)天脈3下的NVMe驅(qū)動(dòng),提升了航空裝備在存儲(chǔ)系統(tǒng)中的性能,對(duì)于嵌入式機(jī)載領(lǐng)域的數(shù)據(jù)存儲(chǔ)有著很高的應(yīng)用價(jià)值。