高性能雙通道稀疏采樣虛擬示波器研制

姜 斌, 唐 禹, 包建榮, 唐向宏, 朱 芳

(杭州電子科技大學 通信工程學院,杭州 310018)

0 引 言

通常示波器在發展中可分為模擬和數字示波器。后者因強大的數據處理和波形分析等功能成為主流[1]。數字示波器測量信號準確度高,因成本高和不易攜帶,主要應用于高校及研究所,不適用于緊急通信線路搶修場景。為此,出現了針對具體應用場景,開發小巧易攜帶示波器產品,缺點是可擴展性差[2]。因高準確度模數轉換器(Analog to Digital Converter,A/DC)售價一直較高[3],導致基于該核心器件的高端實驗儀器成本高。

為消除高速A/DC對我國信號處理事業發展的影響,我國學者研發了多種等效A/DC采樣技術。時間交替并行采樣技術[4]為主流,該技術以較低成本實現周期及重復信號的高準確度采樣,但因多片A/DC并行工作,能耗高、同步定時困難造成所需抽樣樣本數目多。示波器采樣信號具有周期性,故頻譜具有顯著稀疏性。壓縮采樣基于信號稀疏特性,利用有限采樣即可準確重構信號,可有效提升A/DC采樣效率且降低能耗[5-6]。

常用壓縮采樣信號恢復算法主要有正交匹配追蹤(Orthogonal Matching Pursuit,OMP)[5]及root-MUSIC[6],上述方法僅利用單一支撐集,易陷于局部最優,造成信號恢復不理想。多路徑匹配追蹤(Multiple Matching Pursuit, MMP),生成多個候選集并選擇最優,有效提高信號準確度。因示波器信號采樣無法預知信號稀疏度,故改進了MMP算法,獲得稀疏度自適應-MMP(Sparse adaptive-MMP, SA-MMP)方法,并應用至該虛擬儀器,實現高穩定、高準確度的信號恢復,保證了帶寬100 MHz、采樣速率200 MS/s的雙通道虛擬示波器的穩定性能。為方便現場故障排查,還擴展了信號生成,可生成5~10 MHz的常用波形。基于計算機的計算算力及硬件資源,增加了頻譜儀、掃頻儀以及記錄儀的功能,增強實用性。研發的虛擬儀器具有功耗低,配置靈活、信號測試帶寬大及擴展性強等諸多優勢。

1 系統總體結構

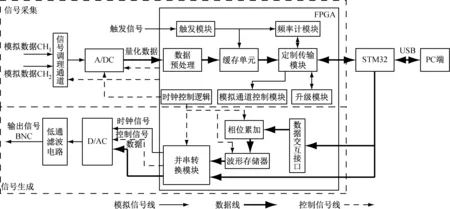

依據虛擬儀器設計思想,示波器分為硬件電路和PC端軟件這兩大部分。硬件采集并量化外部輸入信號,依據PC指令設置生成信號波形參數,輸出信號,完成信號顯示及生成的功能。雙通道虛擬示波器系統總體框架如圖1所示。

圖1 虛擬示波器總體框架圖

通過功能的分類,硬件電路可分為以下幾個模塊:模擬信號通道、數據采集、微控制器(MCU)、個人電腦(PC)端數據處理和信號生成等模塊。其中,信號采集主要由A/DC、現場可編程門列陣(FPGA)及時鐘邏輯控制器等組成,基于FPGA平臺壓縮采樣信號,可極大降低采樣信號所需的能耗。PC端采用了采樣離散信號,用信號重構算法恢復原始信號。重構算法的選擇應遵循盡量少的采樣次數實現高質量信號恢復。

2 硬件電路設計

硬件系統主要由“STM32+FPGA”構成。STM32模塊以STM32F103C8T6芯片為主控制器,負責與上位機的通信及調控。FPGA選用EP1C3T100,分別控制A/DC和D/AC實現信號采集及生成功能。A/DC和D/AC分別選用ADS830E和AD5721。

2.1 信號采集電路設計

信號采集電路主要由模擬信號預處理、觸發脈沖控制、信號采樣通道控制、模數轉換和FPGA緩存組成[8]。根據采樣定理,若要準確重構信號,則A/DC工作頻率不低于信號最高頻率2倍,但會造成高能耗。為此,隨機等效采樣利用非均勻采樣,依據觸發脈沖與采樣時鐘間時間間隔存儲采樣值,多次采樣完成波形信號重構,實現低奈奎斯特采樣頻率。

設采樣信號時間間隔為(0,Ts],觸發時刻與觸發后的第1個采樣時刻的上升沿的時間間隔Δtm,m為隨機采樣次數。觸發采樣脈沖理想且不重復的情況下,需要采樣次數有N=Ts/Δtm。但在實際中,脈沖隨機生成。故Δtm在(0,Ts]區間為非均勻分布,實際采樣次數要多于N次。針對采樣樣本數少導致信號重構失敗的問題,引入壓縮采樣技術。

為保證壓縮采樣信號準確還原,采樣矩陣需便于硬件實現。在此,利用Whittaker-Shannon構建采樣矩陣[5]。故采樣信號y與原始信號x有下式:

(1)

式中:n為信號級數展開項的序號;m為隨機采樣次數,不大于準確重構原始信號最低采樣次數,且m≤M;Te為等效時間采樣周期。將式(1)改寫為矩陣形式,則有:

y=Φx

(2)

y=Φx=ΦΨα

(3)

式中:α為稀疏度為K的稀疏信號,有效降低A/DC芯片工作負荷。

2.2 信號生成電路設計

信號生成電路利用直接數字信號合成(DDS)中的數字頻率合成技術[9]。該模塊主要包括主控芯片STM32、FPGA和D/AC。信號生成主要步驟如下:

步驟1PC端設置生成信號參數,依據協議編碼指令,并由USB轉發至STM32;

步驟2STM32解析指令,初始化D/AC,并生成指令發送至FPGA;

步驟3FPGA讀取STM32指令并利用查表方式讀取ROM固有波形信息,并完成相位累加、RAM讀寫和并串轉換的時序邏輯控制,并生成指令下發至D/AC;

步驟4D/AC在時鐘邏輯控制下輸出對應波形。D/AC為AD5721芯片,可生成信號頻率范圍為:5 Hz~10 MHz。

3 軟件電路設計

軟件模塊主要包括通信、采樣、恢復及儀器驅動程序等。

3.1 通信電路設計

STM32作為一種集成多功能及成熟開發庫的芯片,具有穩定、快速的特點,選用STM32連接硬件電路與PC通信。利用高速USB保證PC端信號穩定傳輸至STM32,STM32基于指令譯碼,并下發至FPGA及周邊電路,FPGA與STM32通信流程如圖2所示。

圖2 STM32通信工作流程圖

PC端給STM32發送初始化指令,STM32讀取Flash中固有數據,初始化并設置時鐘。STM32連接FPGA,采集信號并儲存數據至FIFO中,將一定量的數據發送至PC端,完成信號采集。STM32作為主控模塊,依據指令要求,選擇生成或采樣信號,基于異步通信協議激活信號采樣和生成功能。

3.2 壓縮采樣信號恢復電路設計

壓縮感知可利用有限采樣樣本,準確重構原始信號。但因接收端未知信號稀疏度K,故需利用窮盡方式選擇性重構信號,每次采樣都會造成能耗,時間及存儲成本增加。信號重構需以盡量少的次數完成。

為滿足上述要求,本文提出的SA-MMP算法的目標是在未知K條件下恢復原始稀疏信號。基本思想為:

(1) 估計方法估計信號稀疏度K;

(2) 基于估計得到的稀疏度K,構建深度為K的二叉搜索樹模型;

(3) 利用深度搜索方式,尋求滿足閾值的最優解。

按深度優先搜索的路徑按次序生成,可有效避免路徑重復遍歷,降低存儲負擔。

3.2.1 稀疏度估計

利用匹配測試得到原子集合,即真實稀疏度K0略小于K。假設第m次采樣能夠有效地恢復信號,接收信號y的真實支撐集為Ω,用|>·|表示勢,有|>Ω|=K。令f=Φ*y,設f的第i個元素為fi,且f為壓縮感知的中間投影矩陣變量,“*”為預設值。取|>fi|前K0(1≤K0≤N)最大值索引得集合為Ω0,則|>Ω0|=K0。因Φ滿足有限等距離性質(Restricted Isometry Property,RIP)性質,故若K0≥K,且δk是預設偏差量,有:

(4)

3.2.2 稀疏多徑匹配信號估計

MMP算法在OMP算法估得的索引基礎上擴增候選索引集,并基于索引集擴增多個候選集,形成多個路徑,類似于二叉樹樹形結構。將每一個候選集視作葉子節點,將殘差最小候選集轉化為樹搜索問題。

MMP算法主要由稀疏度K及路徑數S控制。每次迭代過程中,對當前候選集先通過計算內積,選出殘差最為匹配的S個原子,在將該原子依據路徑數分為S組,并將其加入到當前索引集,生成下一級迭代的S個索引集。經迭代,將產生多個索引集,并逐路徑選擇最優支撐集,實現數據重建。該算法通過增加候選集數目,提升選擇正確索引的概率。但基于層序遍歷的樹最優解搜索,路徑存在重合,需存儲候選集,計算負擔較大。因此,引入深度遍歷搜索算法。有效避免從頂層開始計算多條路徑候選集,降低計算量,提升信號重構準確度。

3.2.3 采樣判決停止步驟

故采樣信號采樣判決停止步驟如下

圖3 信號恢復流程圖

3.3 儀器驅動程序模塊設計

驅動程序模塊主要由儀器關閉和啟動、通道控制、水平控制、觸發控制、數據采集、自動設置和波形生成等模塊組成[9]。用戶使用UI界面設置各模塊參數。其功能組成框架如圖4所示。

圖4 儀器驅動模塊組成框架圖

PC端啟動上位機示波器軟件,發送指令初始化硬件電路,建立硬件電路與PC端的通信連接。儀器軟件關閉,PC斷開與硬件電路連接,釋放PC端及硬件緩存。

通道控制模塊主要控制信號采樣通道。水平控制模塊主要設置采樣方式和時基擋位。

觸發控制模塊主要控制硬件電路觸發脈沖,確保精準的時基定位,使波形穩定顯示。模塊主要包括2個設置,即觸發方式及參數設置。觸發參數因成本和硬件資源限制,主要調控是觸發極性和電平。自動設置模塊在系統啟動時,默認設置時基和波形靈敏度。波形生成模塊存儲各標準生成信號,在選定某波形后,將該波形信息傳輸至信號生成電路,得到特定頻率及幅度波形[11]。

4 虛擬示波器樣機的實驗測試

4.1 信號恢復性能測試

圖5 不同稀疏度兩種算法重構概率

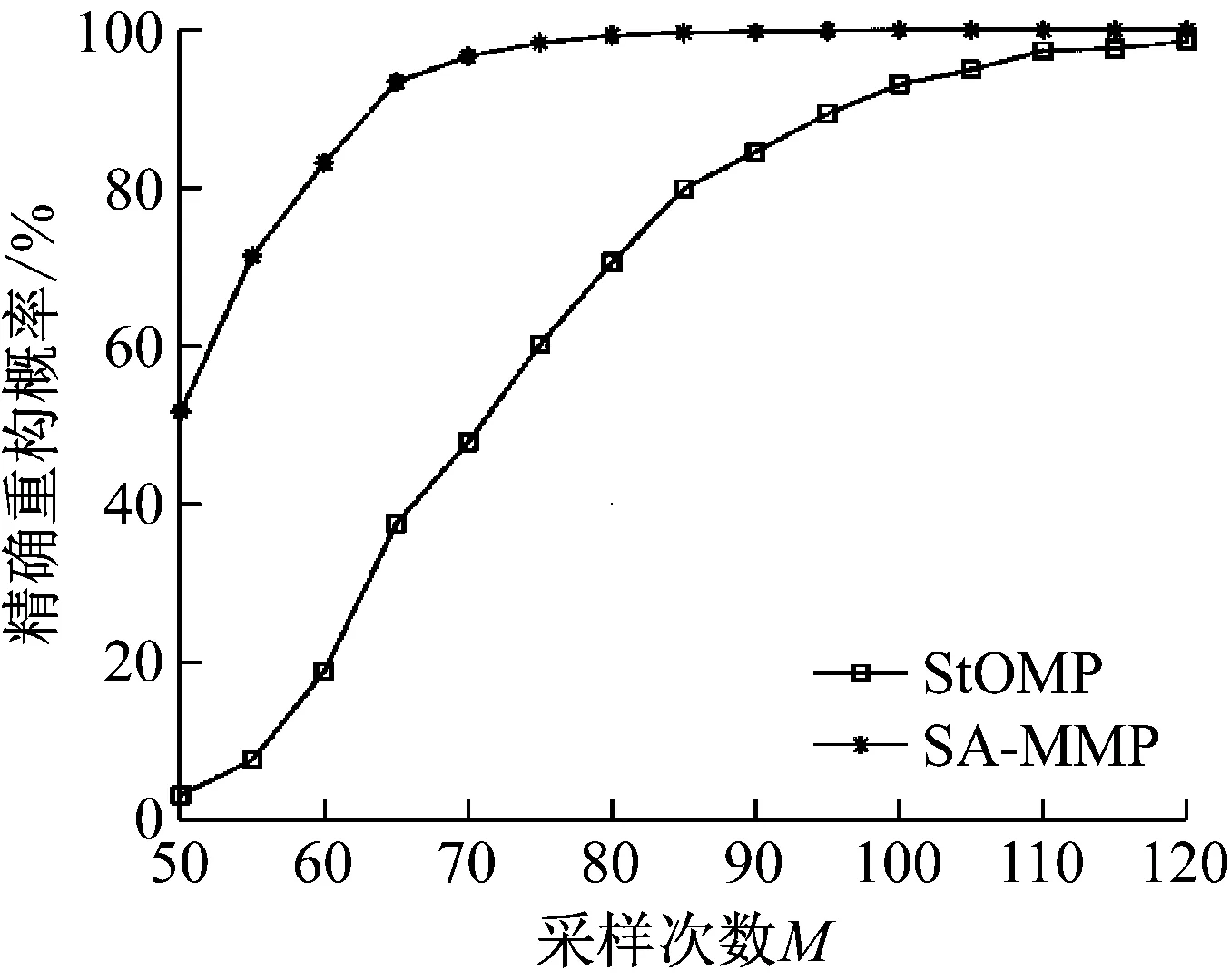

圖6 不同采樣數兩種算法重構概率

如圖5所示信號長度為256,采樣矩陣為Whittaker-Shannon矩陣,采樣128次,不同稀疏度對信號重構的影響。此處,稀疏度設置為[30,70],SA-MMP搜索樹的寬度為4。由圖6可見,本文所提SA-MMP算法要明顯優于傳統的OMP算法,當稀疏度K為40時,OMP算法的重構概率低于90%,之后性能將急劇下降。SA-MMP算法仍能保持100%信號重構。當稀疏度為55時,OMP算法無法重構信號,但SA-MMP仍能保持87%左右的重構概率。SA-MMP引入了多路徑候選集,因此SA-MMP在較大稀疏度K仍保持良好性能。圖6為稀疏度為30時,采樣次數對信號重構的影響。由圖6可見,當OMP實現90%以上重構成功率,則需采樣95次左右。而所提算法僅需64次即可。故SA-MMP需要的采樣樣本數更低,并極大降低了對A/DC的準確度要求。各個壓縮恢復算法的運行時間,見表1。SA-MMP因稀疏度估計原因,運行時長略高于OMP,僅相差0.41 ms,結合SA-MMP所需信號采樣樣本數更少,SA-MMP可實現更快信號重構。

表1 不同恢復算法CPU執行時間

4.2 虛擬示波器效果測試

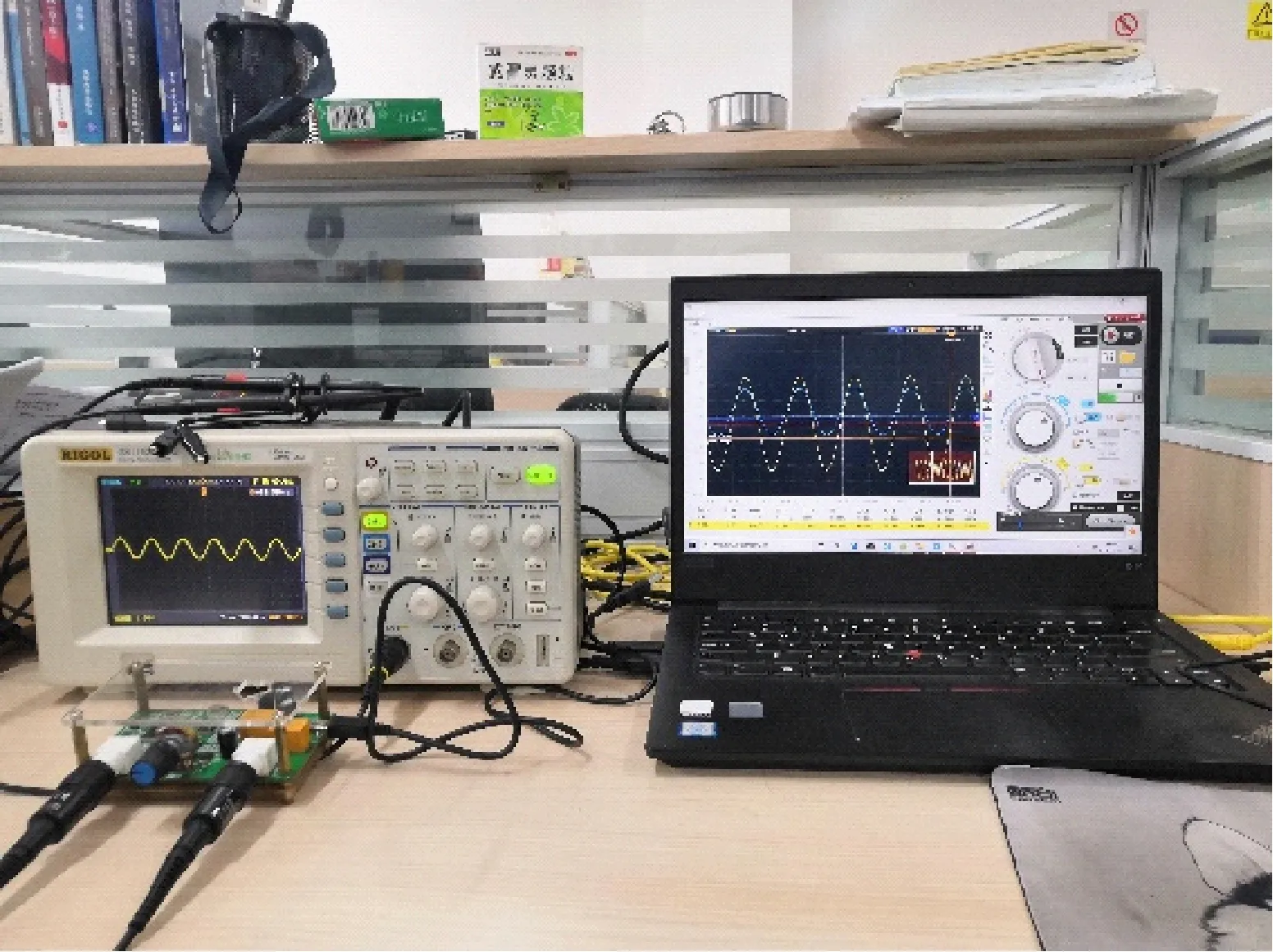

根據上述方案研制的虛擬示波器樣機,同時具備示波器以及信號發生器功能。將PC端通過USB與硬件電路相連接,啟動軟件,點擊“Start Device”啟動示波器功能,點擊右側的“高級”設置信號發生輸出信號參數。

圖7所示為示波器系統測試圖。分別連接信號發生端至數字示波器DS1152E及虛擬示波器,輸出頻率為1 kHz的不同波形。收集不同情形虛擬示波器與數字示波器測量結果,結果見表2。由表2可見,虛擬示波器能夠準確測定信號頻率,幅值測量尚存在一定誤差。但信號誤差波動也僅在1%~3%,基本滿足日常實驗教學所需。

圖7 系統工作效果測試

表2 虛擬數字示波器測量結果對比

除實現示波器及信號發生器功能外,還可進一步擴展軟件功能。基于硬件電路信號采集功能,對采樣插值后的數據做離散傅里葉變換(Discrete Fourier Transform,DFT),可得到信號頻域數據,將數據在PC端顯示得到頻譜分析儀的功能,如圖8所示。利用PC端可控制生成信號頻率,設置步進頻率,可輸出掃頻信號,實現掃頻儀功能,如圖9所示。

圖8 頻譜分析儀功能界面

圖9 信號發生器和掃頻儀功能界面

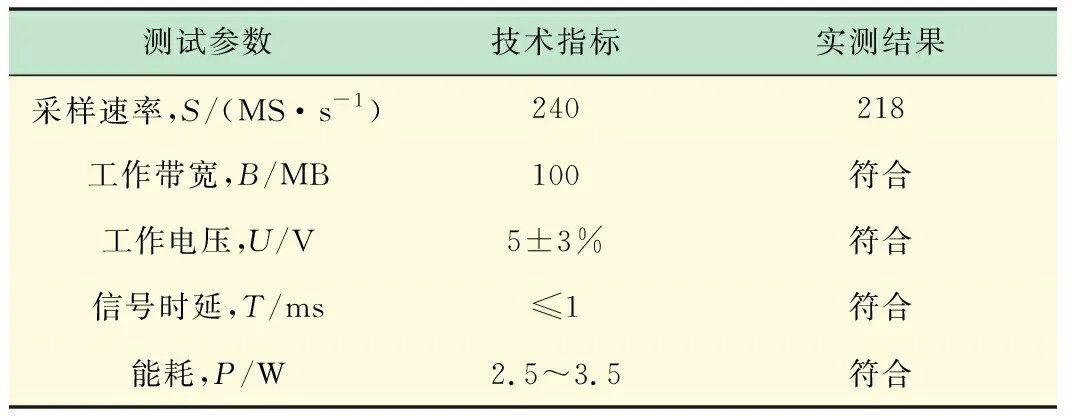

此外,為方便工程師回顧歷史數據波形,增加了無紙記錄儀的功能。點擊REC 按鈕即可對當前的波形進行記錄,以星號*.osc文件名保存,記錄容量大小受限于計算機存儲容量。實現上述功能后,進一步測試示波器硬件電路的各項指標,由表3可得到結論:各項參數基本符合項目目標要求。

表3 虛擬示波器硬件電路模塊各項參數

5 結 語

本文主要論述了基于稀疏采樣的高性能雙通道虛擬示波器的研制。該虛擬示波器采用STM32F103作為主控芯片,利用EP1C3T100和其他外圍電路實現了示波器、信號發生器功能。為提升信號采樣效率,利用FPGA芯片豐富的存儲計算資源,基于非均勻采樣采樣信號,利用SA-MMP恢復信號,實現信號高質量測量、恢復。為充分利用硬件資源,進一步擴展頻譜儀,信號發生器的軟件功能[15]。該示波器具有體積小、易攜帶和多功能等特點,具有廣闊應用市場,可為同類產品設計提供借鑒思路。