高精度Sigma-Delta ADC芯片設計研究

劉慶一 孫艷杰 孫文海 劉瑞華 趙義強

1.大唐半導體科技有限公司 山東省青島市 266100 2.齊魯工業大學(山東省科學院)山東省科學院自動化研究所 山東省濟南市 250014

1 引言

近年來,隨著傳感器技術的發展,各類傳感器廣泛應用于工業及汽車電子產品等領域。模數轉換器(ADC)作為傳感器信號數字化的重要電路單元,對其精度及速度要求較高。Sigma-Delta ADC 利用過采樣和噪聲整形技術,可以提高信號的信噪比,提升轉換精度。

本文專注于高精度模數轉換器芯片的設計,研究面向車規級傳感器信號采集應用的16-bit高精度、低噪聲微弱電信號采集和模數轉換電路的架構設計技術,以及低噪聲設計技術、失調消除技術、高性能信號緩沖器軌到軌輸入級設計技術。設計高精度、數據率可調Sigma-delta調制器,低通帶紋波降采樣濾波器設計技術,低噪聲參考電壓產生技術、電源和共模干擾抑制技術,實現高可靠高精度Sigma-Delta型模數轉換器芯片。

2 總體方案

總體架構如圖1所示,由多位Sigma Delta調制器、重建濾波器、可編程抽取濾波器、FIR濾波器以及輸入緩沖器、控制邏輯等構成。片內集成基準電壓驅動緩沖器以及用于輸入信號緩沖、電平轉換的差分放大器,形成高度集成的緊湊型數據采集器件,消除復雜模擬前端信號處理電路設計需求,簡化ADC使用。

圖1 Delta sigma ADC系統架構示意圖

3 電路實現

3.1 Delta sigma調制器

Delta sigma調制器結構如圖2所示,為滿足高精度高速性能需求,將采用帶有雙采樣積分器的3階5-bit多比特量化高階調制器結構。調制器電路基于離散時間的開關電容電路實現,包括三個開關電容積分器、一個5-bit異步時序逐次逼近量化器、動態元件匹配電路、32級的開關電容DAC等。

圖2 基于3階5-bit多比特量化的調制器結構示意圖

在5-bit量化器中,第一級、第三級的采樣電容和反饋電容均分成31個單元,用來完成32級數模轉換(DAC),并通過對第一、第二、第三級的單位電容進行優化設計降低開關KT/C噪聲。

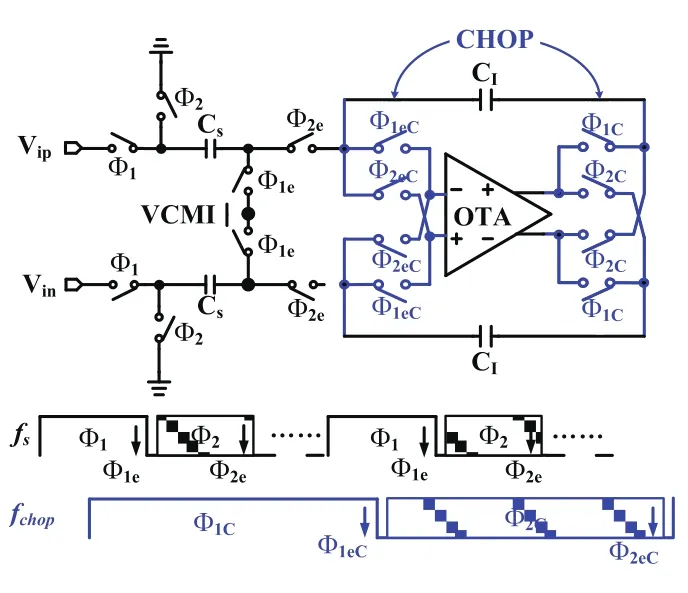

差分輸入由調制器以最高40MSPS的采樣速率進行采樣,可在64倍過采樣率下實現最高625kSPS的轉換速率。所有的控制信號由雙向不交疊時鐘產生,避免電荷注入帶來的誤差。第一級積分器的輸入采樣開關采用自舉開關,消除采樣開關的非線性導通電阻帶來的失真;內部采樣和反饋開關,由于傳輸電平幅度變化較大,為保證良好的導通性使用互補CMOS開關。圖3為雙采樣積分器與時序示意圖。

圖3 雙采樣積分器與時序示意圖

在第一級積分器內部跨導放大器(OTA)的輸入和輸出端使用斬波技術來消除OTA的1/f噪聲和失調,圖4為積分器中斬波技術示意圖。通過選擇斬波動作與時鐘相的關系,減小對時序的要求。通過優化斬波頻率,降低過快的時鐘翻轉帶來的額外開關噪聲和功耗。

圖4 積分器中斬波技術示意圖

量化器前擬采用一種新型的模擬加法器結構,消除傳統的模擬加法器帶來的幅度衰減,避免補償運放或者降低參考電壓帶來的消耗,減小功耗,降低電路實現難度。

調制器采用一種5-bit異步時序的逐次逼近的量化器,相比基于傳統的Flash結構的5-bit量化器,有明顯的面積和功耗優勢。采用異步時序邏輯,相比同步時序,不需要高速的外部時鐘,減小功耗代價。和前級積分器采用同一時鐘,簡化電路實現。

量化器通過一個溫度計譯碼器,轉換成溫度計碼。然后通過動態元件匹配(DEM)模塊,轉換成DAC的控制信號,完成DAC反饋。DEM采用一種基于數據加權平均(DWA)算法的方式實現,具有實現簡單、硬件代價較低的優點。

3.2 運算放大器設計

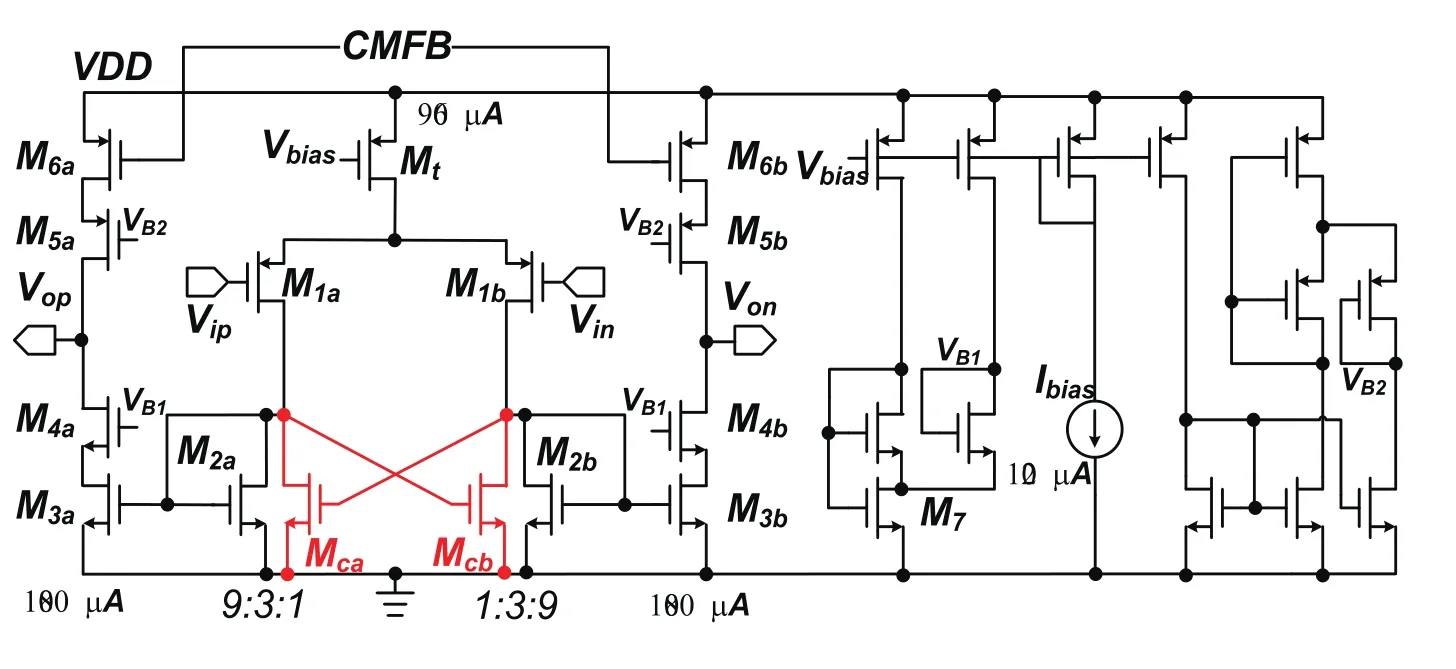

由于采用多階積分器結構,后級引入的噪聲會被環路抑制。第一積分器內部OTA必須被仔細設計,才能避免OTA引入的噪聲和非理想因素嚴重惡化調制器性能。OTA的有限增益會對積分器引入增益誤差和NTF的極點誤差,造成量化噪聲泄漏,此外OTA的非線性增益也將造成量化噪聲混疊,從而增加帶內噪聲能量。第一級積分器內部OTA原理圖如圖5所示。

由于采用前饋結構和多比特量化,積分器的輸出擺幅有很顯著的縮減,因此增益非線性的影響被弱化很多,如圖5所示,第一級積分器將采用電流鏡運放結構。輸入管采用PMOS輸入,用來減小OTA貢獻的1/f噪聲,此外PMOS獨立的N阱也可以屏蔽數字電路到模擬電路的耦合噪聲串擾,輸出級采用cascade結構用來提高增益。電流鏡運放結構的優點是主級點和非主極點相距甚遠,OTA的相位裕度接近90度,接近為一個單級運放,當閉環工作時,穩定性非常強。同時,電路采用電流消去技術,將非主極點的從高頻往低頻處推,進而可以使OTA的相位裕度下降到60度附近,此時積分器建立特性最為理想。

圖5 第一級積分器內部OTA原理圖

3.3 5-bit SAR量化器設計

采用的5-Bit異步時序控制SAR量化器的結構、時序以及控制邏輯如圖6(a)所示。整個SAR量化器共包括三大模塊:開關電容陣列、比較器和異步時序邏輯。開關電容陣列采用二進制的方式分布,開關電容陣列所有的電容在積分相為第三級積分器的負載,因此對電容值進行優化設計,保證第三級積分器完全建立的同時降低工藝引起的電容失配影響。比較器采用一種動態比較器實現。圖6(b)為SAR量化器的工作時序。

圖6 (a)5-Bit異步時序SAR量化器結構 (b)工作時序

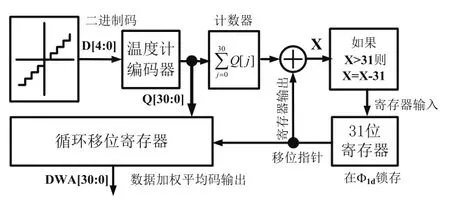

3.4 動態匹配邏輯設計

將采用基于數據加權品均算法(DWA)的動態匹配(DEM)技術來消除多比特DAC引入的非線性失真,該算法DWA具有實現簡單,消除DAC非線性效果好的優點。圖7給出基于DWA算法的DEM實現框圖。SAR量化器在Φ相時,對輸入信號進行量化、然后將輸出的二進制碼輸入溫度計編碼器,產生溫度器編碼。溫度計編碼放入一個循環移位寄存器,等待31位寄存器的移位指針的控制信號,來進行輸出。溫度計編碼輸出進入計數器,進行一個求和,后級處理保證和不能大于31,然后將這個數送入寄存器。最終產生移位指針給循環移位寄存器產生DWA的31位輸出。數據加權平均碼由Φ控制,用來產生調制器中的開關,實現DAC反饋。

圖7 動態元件匹配邏輯結構示意圖

3.5 Bandgap和參考電壓產生電路

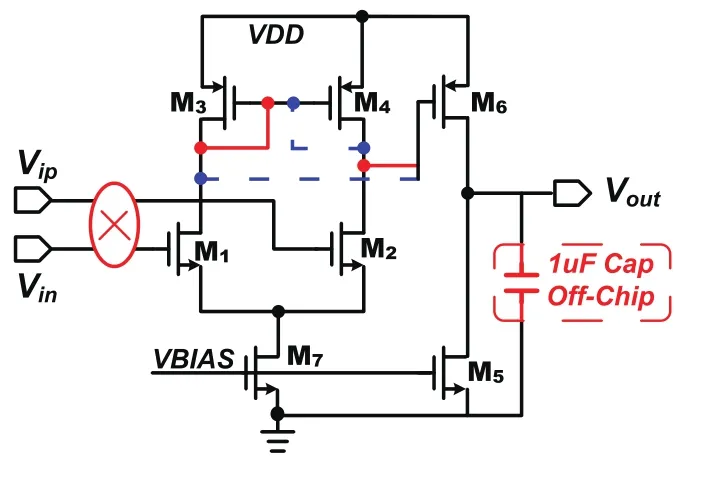

Bandgap和參考電壓產生電路對高精度ADC設計至關重要,設計中將片內集成參考電壓緩沖級,由于為柵極高阻輸入,因此電阻串分壓即可完成參考。如圖8所示的兩級放大器為片內參考電壓緩沖級,第一級采用五管差轉單電路,后接一級共源放大器輸出。由于參考緩沖級引入的噪聲不能被調制器環路抑制,將直接疊加到輸入信號上,需對參考電路進行低噪聲設計與優化。

圖8 電壓參考緩沖級

除了熱噪聲的影響,低頻1/f噪聲也必須被抑制到足夠低的水平。運放采用簡潔結構,盡量減少噪聲來源。電路將采用斬波技術,用來消除低頻失調和1/f噪聲。

3.6 濾波器設計

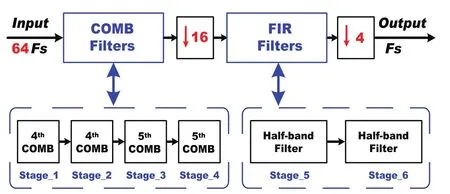

采用的降采樣濾波器結構如圖9所示,將采用六級級聯結構減小濾波器設計難度。濾波器的前四級由于過渡帶較寬,對性能要求相對較低,因此采用容易實現的組合(Comb)濾波器,前兩級和第三第四級分別為四階和五階Comb濾波器。后兩級由于過渡帶非常窄,而且對整個降采樣濾波器的性能起著決定性作用,因此采用2個高階FIR結構的半帶濾波器實現。每一級濾波器對信號完成2倍的降采樣,因此整個半帶濾波器完成64倍降采樣。

圖9 降采樣濾波器的系統結構

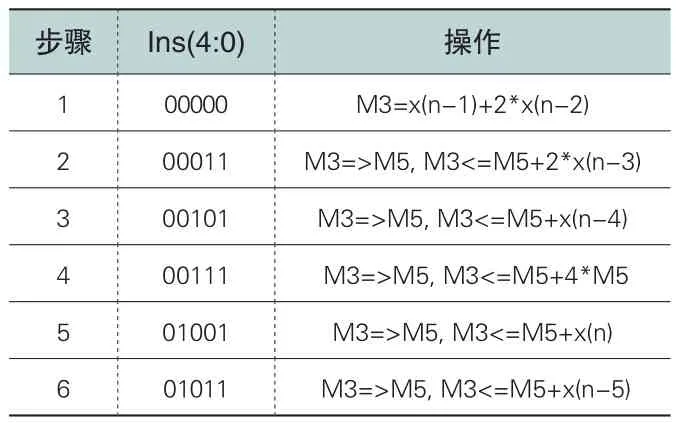

前四級組合(Comb)濾波器采用級聯積分梳狀(Cascaded Integrator Comb,CIC)濾波器,屬于線形相位FIR濾波器,由工作在高抽樣率的級聯理想積分器和低抽樣率的級聯微分器組成。CIC濾波器的主要特點是:實現簡單且速度高,僅利用加法器、寄存器以及多路選通器就可以實現,因此實現代價小。第一、二級采用四階結構,而第三、四級采用五階結構。前四級Comb濾波器的實現方法比較相似,圖10給出第四級5階Comb濾波器結構示意圖,其工作在1/16芯片主時鐘頻率,可以采用時分復用的方式來減小硬件代價。通過采用時分復用,本級濾波器只需一個多位加法器即可實現。表1為第四級Comb濾波器工作時序示意。

表1 第四級Comb濾波器工作時序示意

圖10 第四級Comb濾波器結構

整個降采樣濾波器最后兩級將采用線性相位的FIR半帶濾波器實現,其決定著整個降采樣濾波器的性能。為了達到24-Bit的精度,高頻噪聲必須要被衰減到足夠低的程度,加上此時濾波器過渡帶十分窄,因此半帶濾波器阻帶衰減至少要大于100dB,此外還需要盡量窄的過渡帶。由于采用FIR結構,要求高階數濾波器。傳統方式實現,高階濾波器將占據十分大的芯片面積和功耗。擬采用一種高效的110階級聯子濾波器結構的FIR半帶濾波器,同時采用時分復用和濾波器系數CSD編碼的實現方法,從而達到低功耗、低面積消耗的高階濾波器實現。兩級半帶濾波器將采用同樣的結構實現,如圖11所示,圖中F2為級聯的子濾波器,子濾波器F2結構如圖12所示。

圖11 半帶濾波器結構

圖12 子濾波器F2結構

4 結束語

本文基于正向設計和反向參考,采用中芯國際0.13um CMOS工藝,離散時間sigma-delta架構,模擬前端著重改善噪聲性能,優化差分匹配和通道匹配,增強通道隔離;在數字域使用數字濾波,濾除50/60Hz工頻噪聲,提高了信噪比。