一種基于EDA 的乒乓球游戲機的設計

錢虹凌

(山西大同大學教學實驗與實訓中心,山西 大同 037003)

EDA 為常見的FPGA 開發工具,基于此開發設計的一款乒乓球游戲機,可以滿足用戶的使用要求。

1 乒乓球游戲機可實現的功能

乒乓球游戲機可實現的功能如下:能進行正常的計局、計分功能;能實現對球臺和乒乓球的物理模擬實現功能;用發光二極管來替代乒乓球,每個乒乓球由10個發光二極管來構成;能實現自動判球計分;能進行得勝顯示。

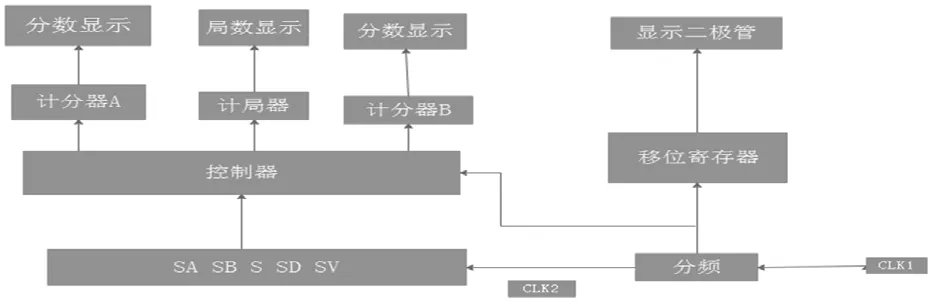

設計思路:乒乓球游戲機原理框圖如圖1 所示。

圖1 乒乓球游戲機原理框圖

2 模塊電路功能(采用自頂向下方法設計)

(1)總電路由計分器、計局器、移位寄存器和控制器來組成。其中,A、B 雙方計分顯示和計局器顯示分別由六個數碼管來完成。

(2)控制器模塊由時序機來實現,能夠完成對計分器、計局器和移位寄存器的控制,其系統流程圖如圖2所示。

圖2 系統流程圖

(3)CLK1 輸出的時鐘信號經分頻后得到的信號來作為移位寄存器和控制器的時鐘控制信號。

(4)CLK2 輸出的時鐘信號用于消除按鍵抖動。

(5)SA、SB、S、SD、SV 模塊為D 觸發器,其時鐘信號由CLK2 來進行提供。

3 部分軟件及說明

該游戲機的計局器和計分器可由四位二進制計數器來實現,具體實現的VHDL 部分程序及說明如下:

Entity count is

根據 Ari(2005)[12]將智力資本劃分為人力資本和結構資本,本文將人力資本和結構資本劃分為以下幾個維度。

Port(clk: in std_logic;---------輸入、輸出端口信號定義

Q:out std_logic_vecter(3 downto 0));

End count;

Architecture behave of count is

Signal qq: std_logic_vecter(3 downto 0);

Begin

Process(clk)------進程由敏感時鐘信號CLK 觸發。

Begin

If clk’event and clk=’1’then

Qq<=qq+1;

End if;

End process;

Q<=qq;

End behave;

EDA 軟件QuartusII 操作界面如圖3 所示。

圖3 QuartusII 設計軟件操作設置界面

4 結語

該乒乓球游戲機可實現正常的計局、計分功能,采用VHDL 語言獨特的自頂向下的設計方法進行設計,可以達到預期的開發效果。