紅外地球敏感器光電組件測試系統設計

潘 攀,佟亞珍,宋佳赟,李晶晶,王培超

(北京東方計量測試研究所, 北京 100086)

0 引言

圓錐掃描式紅外地球敏感器是中低軌道航天器姿態測量的關鍵部件,其中,光電組件的性能參數直接影響衛星姿態角的測量精度。衛星控制系統對光電組件測試系統提出的要求為:信號幅值采集精度優于50 mV/20 V,信號頻率測試精度優于1 Hz/100 kHz。鑒于國內對相關電信號測量的研究不多,設計了一種紅外地球敏感器光電組件測試系統,精確測量了光電組件的光柵信號和基準信號的幅度、頻率等參數,對實現衛星姿態的精準定位,有效提高衛星在軌的自主性具有參考意義。

1 系統硬件電路

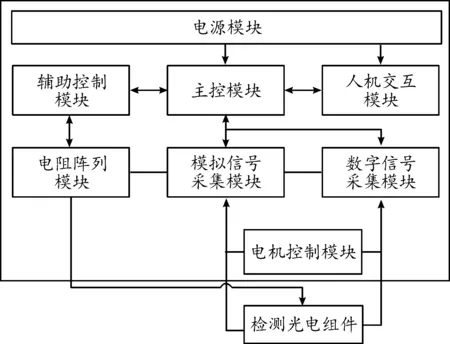

紅外地球敏感器光電組件測試系統的硬件電路構成主要包括模擬信號采集模塊、數字信號采集模塊、電阻陣列模塊、電機控制模塊、輔助控制模塊、主控模塊和電源,測試系統組成如圖1所示。

圖1 紅外地球敏感器光電組件測試系統框圖

主控模塊為核心控制器模塊,它一方面將軟件界面設置的電機轉速等參數傳輸給電機控制模塊以驅動電機并提取轉速等信號,另一方面完成測試過程的動作實施,通過反饋的相關信號進行計算并存儲;模擬信號采集模塊為電機電流遙測信號及被測光電組件模擬信號采集硬件電路;數字信號采集模塊為電機轉速及被測光電組件信號頻率采集硬件電路。

1.1 主控模塊

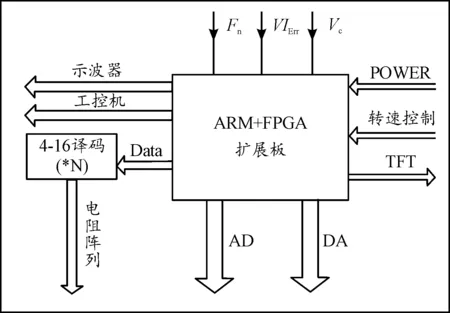

主控模塊采用ARM+FPGA方案,設計原理如圖2所示。ARM在控制方面性能優異,能夠很好地完成分配調度任務和運算工作,且在驅動TFT、通信等方面非常穩定。對于信號采集,采用FPGA+高精度AD實現。雙核ARM Cortex-A9提供最大667 MHz的頻率,極大增強了控制單元的控制和處理能力,并包含豐富的存儲功能,提供HDMI、VGA等多種接口形式滿足設備各種通信需求。

圖2 主控模塊設計原理框圖

1.2 模擬信號采集模塊

由于系統需要進行A/D轉換的信號較多,精度要求高,故采用TI的ADS8568作為A/D采集芯片,設置成8通道同步采樣,保證基準信號、光柵信號可獨立通斷使用,也可以并行使用。

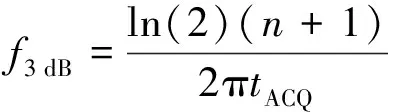

ADS8656為SAR類型ADC,對輸入信號要求較高,輸入電流由實際采樣率、輸入電壓、源阻抗決定。ADC工作時需要信號將內部的充電電容充滿直到轉換周期開始,設轉換周期為tACQ,則其 -3 dB帶寬為:

(1)

式中:n為ADC的有效位數。以最小轉換時間280 ns為例,此時需要的前置ADC帶寬約6.7 MHz,如果小于該值,引起的增益誤差將不能被修正。

SAR ADC對信號源輸出阻抗也有較高要求,信號源的輸出阻抗比滿足:

(2)

式中:n為ADC有效位數;Cs為充電電容(4Vref時為10 pf);RSER為200 Ω輸入電阻值;RSW為內部開關電阻值。以最小轉換時間280 ns時為例,此時源阻抗必須小于2 kΩ,而在很多電壓測量環節,要求源阻抗小于2 kΩ幾乎不可能,所以在ADC之前需要增加一個高帶寬的ADC驅動器,要求其帶寬足夠大,輸出阻抗盡可能小。

1.3 數字信號采集模塊

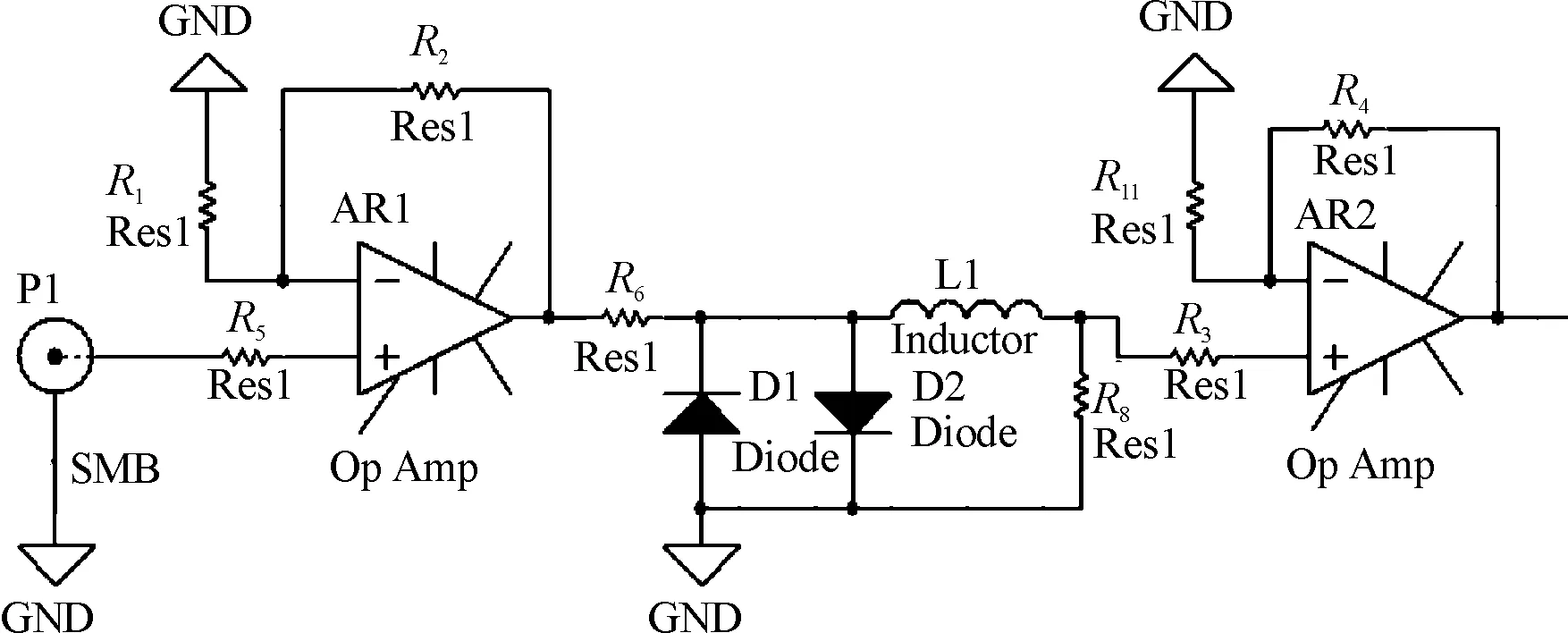

數字采集模塊實質上是FPGA對IO口TTL波形的計數。而基準輸出信號、光柵輸出信號為正弦波信號,信號的幅值為0.1~12 V,不符合TTL信號電平要求,需要一個前端電路將其調理成TTL電平。該頻率測量前端電路如圖3所示。

圖3 頻率測量前端電路圖

圖3中被測信號通過P1輸入,R5為限流電阻,AR1為放大電路,使得0.1~12 V的電壓信號能放大到后級限幅電路的限制范圍。D1、D2將輸入信號限幅到0.7 V左右,再通過AR2放大到近似TTL電平的幅值范圍。AR2的輸出接到施密特芯片74HC14,轉換成標準的TTL信號,再輸入FPGA的IO做等精度頻率測量。

FPGA內部時鐘頻率需要做出廠標定,通過內部程序將100 MHz系統時鐘10分頻輸出,由片上系統內部的選擇器將信號輸出到后面板,校準時使用外接頻率計即可。

1.4 電阻陣列模塊

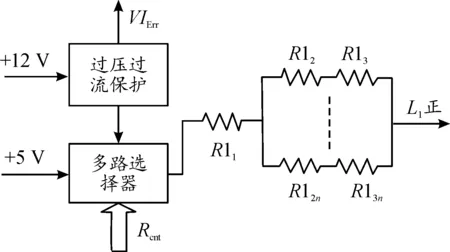

光柵信號、基準信號通過調節電阻的阻值調節發光二極管強度。電阻陣列模塊原理如圖4所示。

圖4 電阻陣列模塊原理圖

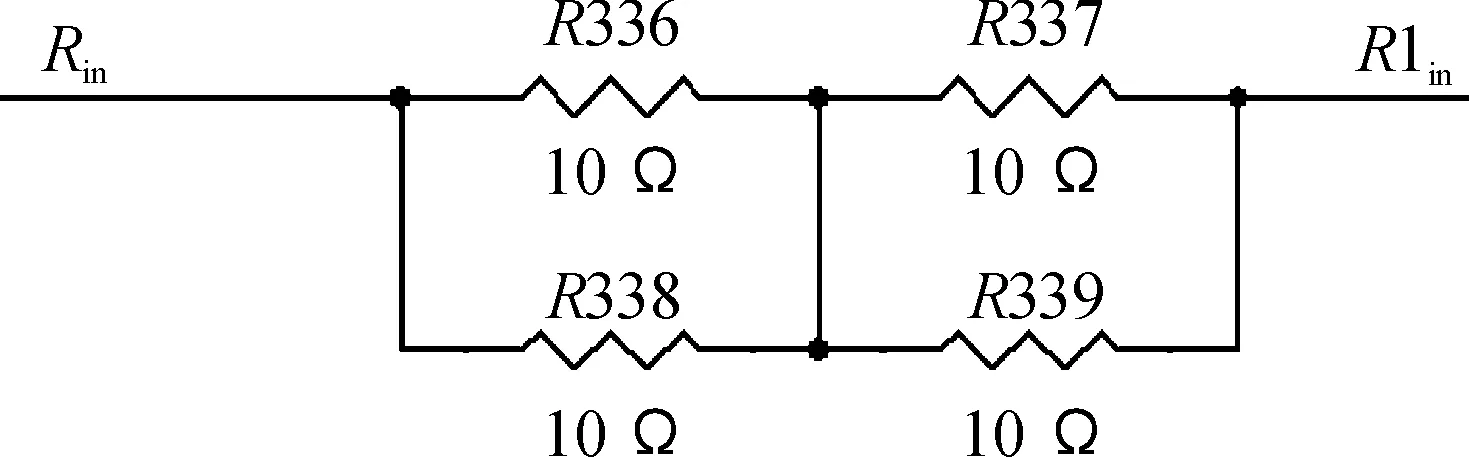

12 V電源通過過壓過流保護進入電子開關。電子模擬開關輸入經過R11采樣電阻進入電阻陣列R12~R12n,電阻陣列的輸出連接發光二極管L1的正極。L1通過的電流約為幾十毫安,所以采樣電阻選擇718廠RMK(1206)型有失效率等級的片式薄膜系列貼片電阻,阻值為10 Ω。電阻溫度系數為±10×10-6/K,阻值偏差±0.05%,極限電壓為100 V,滿足此處的電流采樣要求。同時,選用4只10 Ω(70°額定功率0.25 W)電阻串并聯組成10 Ω(圖5),此時采樣電阻上的額定功率增加到1 W,系統正常工作時采樣電阻上的最大功率為:

(3)

額定功率遠大于該采樣電阻上正常工作時的最大功率,滿足系統穩定性要求。

圖5 10 Ω采樣電阻電路圖

2 系統軟件設計

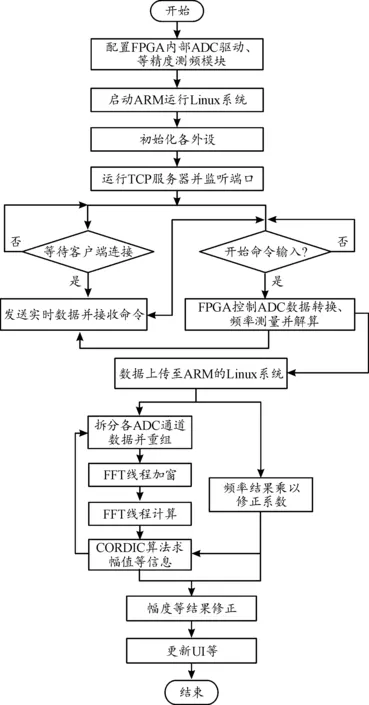

系統軟件運行在Linux 系統中,總體設計流程如圖6所示。系統上電啟動應用程序,應用程序開始后配置FPGA內部ADC驅動、頻率測量模塊驅動,初始化各外設,運行TCP服務器并監聽設定端口;ADC、頻率測量模塊得到的數據傳輸到ARM Linux中進行處理,ADC數據經過濾波、加窗、FFT、幅值恢復及顯示等處理,頻率結果直接修正顯示。

圖6 系統總體設計流程框圖

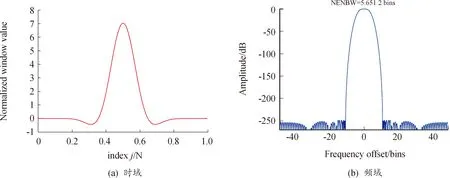

光電組件光柵信號和基準信號的幅值采用傅里葉變換將時域連續的信號轉換到頻域內,通過適當的探測算法得到想要的幅度譜數據。為了提高幅值的精度,通常采用加窗、頻譜修正等技術,加窗的目的是壓低旁瓣、減小頻譜的泄露。連續信號經過加窗截斷后的數據再通過FFT計算可得到信號的頻譜,頻譜經過相關計算即可得到信號的幅度譜。FFT計算過程中包含各種窗函數,不同的窗函數得到的幅度譜精度不同,Flat Top窗函數可以較精確地恢復各個不在分辨率上的信號幅度。本文采用目前應用較廣的Flat Top窗函數進行幅度譜分析計算,該窗函數的形式為:

(4)

其中:ck為關于k的常數;N為FFT計算點數。

不同維度的Flat Top窗能得到不同的精度,HFT248D是Flat top窗中誤差最小的算法,也最復雜,其公式為:

ωj=1-1.985 844 164 102cos(z)+

1.711 764 385 06cos(2z)-

1.282 075 284 005cos(3z)+

0.667 777 530 266cos(4z)+

0.240 160 796 576cos(5z)+

0.056 656 381 764cos(6z)-

0.008 134 974 479cos(7z)+

0.000 624 544 650cos(8z)-

0.000 019 808 998cos(9z)+

0.000 000 132 974cos(10z)

時域、頻域的波形如圖7所示。

假設原始信號為

(5)

式中:Adc為直流分量幅值;f1為被測信號頻率;P1為初始相位;fn為干擾信號頻率。

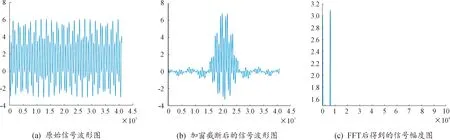

假定Adc=1.5,A1=3.1,A2=1.5,f1=6 274.25,f2=2 000.5,P1=-30,P2=90,其時域波形如圖8(a)所示,加窗后時域波形如圖8(b)所示,FFT結果如圖8(c)所示。

圖7 時域、頻域波形

圖8 信號FFTW前后波形

FFTW庫是美國麻省理工學院計算機科學實驗室超級計算組開發的目前世界上公認運算較快、使用廣泛的串行C程序自適應軟件包。FFTW庫能自適應系統硬件,可移植性強,可用于計算任意維數的實、復數類型的離散傅里葉變換。FFTW庫主要通過靈活運用運行時性能分析和相關的搜索技術來選擇離散傅里葉變換的最優分解路徑,可適應于不同的計算機體系結構。FFTW庫主要由底層的代碼生成器和上層的運行框架兩部分組成,FFTW底層基本實現了所有的快速傅里葉變換算法。在FFTW庫自動化配置時會記下每一個算法的執行時間和對于任意問題規模的快速傅里葉變換。

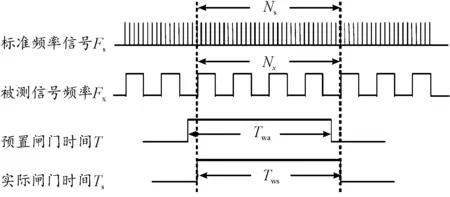

光電組件光柵信號和基準信號的頻率為0~44 kHz,測試精度不大于5″。采用等精度測量方法。等精度頻率測量法是在直接測頻方法基礎上發展而來,其實際閘門時間不固定,是被測信號周期的整數倍,與被測信號同步,因此又稱為多周期同步法。此方法利用閘門與被測信號同步消除對被測信號計數時產生的±1個周期誤差,測量精度大為提高,實現了在整個測量期間的等精度測量。頻率測量原理及波形如圖9所示。

圖9 等精度頻率測量原理及波形

在測量過程中,有2個計數器分別對標準頻率信號Fs及被測頻率信號Fx同時計數。首先給出預置閘門上升沿開啟信號,此時2個計數器并不開始計數,而是等到被測頻率信號的上升沿到來時才真正開始計數。當預置閘門下降沿關閉信號到來時,2個計數器并不立即停止計數,而是等到被測頻率信號的上升沿到來時才停止計數,完成一次測量過程。

設標準信號的頻率為Fs,被測信號的頻率為Fx,在測量時間段Tws內被測頻率信號的計數值為Nx,標準頻率信號的計數值為Ns,則式(6)成立。

(6)

設被測信號的頻率準確值為Fx0。在一次測量過程中,由于被測信號Fx計數的起停時間是由該信號的上升沿控制的,因此在測量時間段Tws內對Fx的計數Nx無誤差。在此時間段內對Fs的計數Ns最多相差1個脈沖,即|ΔNs|≤1,則下列等式成立:

(7)

根據相對誤差公式:

(8)

則被測信號Fx的相對誤差

(9)

由式(9)可知:被測信號頻率的相對誤差與被測信號的頻率無關,增大測量時間段Tws或提高Fs可以增大Ns,從而減小相對誤差,提高測量精度。測量精度與實際閘門時間和標準信號頻率Fs有關,與被測信號頻率無關,因此能獲得較高的精度。

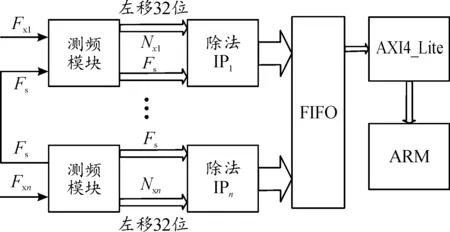

等精度測量過程中會產生2個量:Nx和Ns,位寬都是32 bit,而AXI4_Lite位寬為8 bit,兩接口的對接使用到雙口RAM,且N通道的頻率測量模塊結果將達到N*32 bit,無法直接連接到只有8bit的AXI4_Lite接口,中間還需要一級FIFO轉換,利用這種方法可實現數據傳輸。但由于在ARM中實時讀取設備文件時保證Nx和Ns數據對齊異常困難,很容易出現錯誤,因此設計了一種新型頻率采樣方案。該方案能夠有效解決同步傳輸易出錯和CPU占用率高的問題,其計算流程見圖10。

圖10 測量結果計算流程框圖

如圖10所示,左移32位是為了減少ARM中處理FPGA產生的復雜小數帶來的運算,Nx擴大了232倍,小數結果保存到整數部分的64位數據中,在FIFO寫入數據過程中可保證不會丟失任何一個通道的數據,也不存在Nx和Ns不同步的情況。結果傳輸到ARM中只需右移32 bit,再乘以修正晶振頻率即可得到精確結果,該算法帶來的誤差為2-32,對于測量來說可忽略不計。同時,控制器的結果計算只需要32移位操作,極大降低了CPU使用率。

3 系統測試

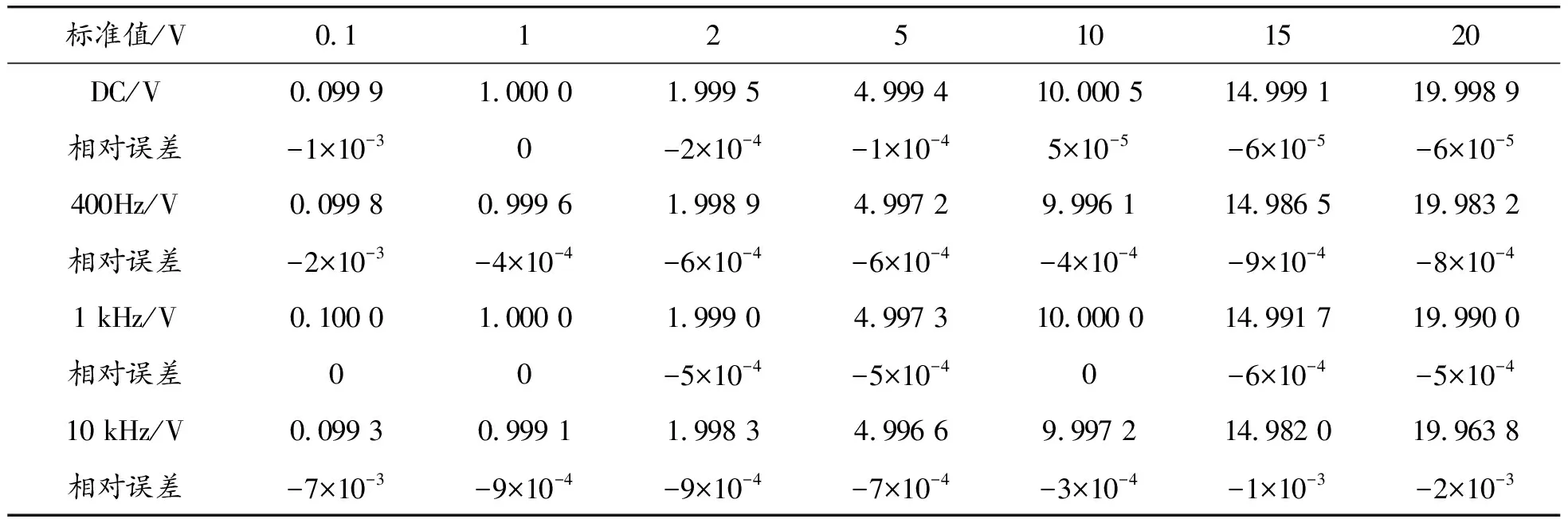

3.1 幅度測試

采用紅外地球敏感器光電組件測試系統對幅值范圍為0.1~20 V,頻率范圍為DC~10 kHz的被測信號進行測試,測試結果如表1所示。

測試結果表明,設計的光電組件測試系統信號幅值采集精度優于0.2%(47 mV/20 V,10 kHz),能夠滿足設計要求。

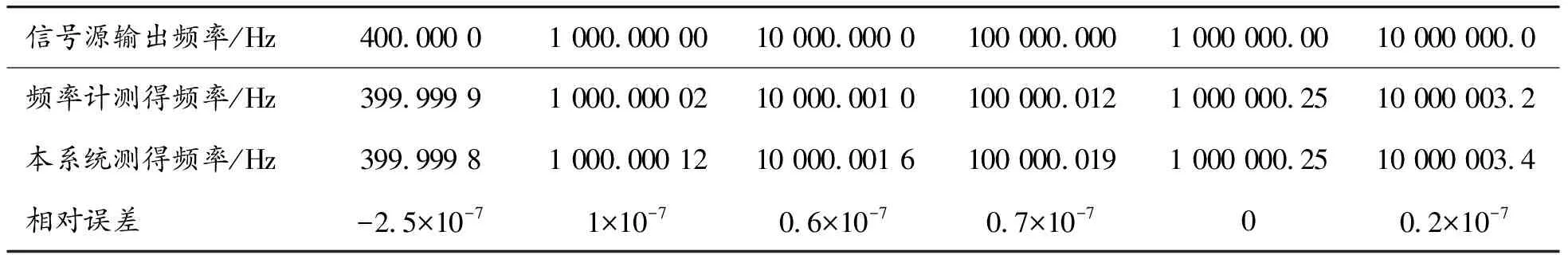

3.2 頻率測試

采用設計的紅外地球敏感器光電組件測試系統和頻率計分別對400 Hz~10 MHz的被測頻率進行測試,測試結果如表2所示。測試結果表明,設計的光電組件測試系統信號頻率測試精度優于1×10-7(0.01 Hz/100 kHz),能滿足設計要求。

表1 幅度測試結果

表2 頻率測試結果

4 結論

1) 設計的紅外地球敏感器光電組件測試系統能夠滿足光電組件測試系統的設計要求,能夠實現光電組件的光柵信號和基準信號的幅度、頻率的精確測量。

2) 該系統在達到較高集成度的同時保證了較強的性能和較好的計量特性。