星載天海中繼通信載荷信號處理單元實現

劉 冕,胡一皓,王晉陽,劉才瑞,梁顯鋒

(1.中國科學院國家空間科學中心,北京 100190;2.中國科學院大學 電子電氣與通信工程學院,北京 100190)

0 引言

低軌互聯網衛星網絡能夠實現廣域無縫覆蓋,是未來海陸空一體化網絡的重要組成部分[1]。目前在海洋研究領域,通信衛星網絡能為深遠海的海洋觀測浮標與岸基站/船基站之間提供實時數據通信。美國銥星系統(Iridium Satellite)、法國Argos系統等低軌通信衛星網絡最大能實現128 kb/s的雙向數據傳輸[2];我國天通一號通信衛星網絡能夠實現384 kb/s速率的數據通信[3],但是數據速率均未超過1 Mb/s[4]。隨著海洋水下載荷獲取數據量的不斷增加,水面通信浮標到船基或岸基數據中心間需要實現高數據傳輸速率鏈路。

最近,某單位研制了一臺天海中繼通信載荷,搭載在低軌衛星上,用于驗證海面到船端間高速率中繼通信鏈路試驗,實現水面到數據中心間8 Mb/s速率的數據通信鏈路。天海中繼通信載荷主要包括射頻單元和數字基帶單元。本文完成了天海中繼通信載荷中L波段數字基帶單元的設計和功能實現。基帶單元主要實現通信鏈路編碼調制一體化的技術方案。在FPGA為主的平臺上不僅實現里德所羅門卷積級聯(Reed-Solomon Convolution Concatenated,RS-CC)編碼以及低密度奇偶校驗碼(Low Density Parity Check Code,LDPC)編碼功能,且可自動切換前向鏈路的2種編碼調制方式;反向鏈路接收方案采用零中頻解調將來自水面浮標端的載荷數據進行解調并使用反饋環路校正了鏈路多普勒頻移的影響。文中也敘述了載荷的調試和測試工作。

1 技術分析

1.1 特性分析

天海中繼通信載荷主要功能是實現海面浮標經低軌衛星中繼,與跨距500 n mile外的船端或陸地數據中心之間的高速率數據通信試驗。載荷通信頻段為低軌互聯網段的L波段,通信鏈路如圖1所示。

圖1 通信鏈路示意Fig.1 Diagram of the communication link

衛星到海面浮標端的通信鏈路定義為前向鏈路,初始低碼率模式下傳星歷數據,用于浮標端天線快速跟蹤衛星;高碼率模式為衛星天海中繼通信載荷收到海上浮標端發送的8 Mb/s數據,直接轉發下行到跨距500 n mile的船端或岸基端。海面浮標到衛星的固定8 Mb/s高碼率通信鏈路定義為反向鏈路。

衛星軌道高度500 km,根據鏈路計算式(1)分別完成了反向鏈路和前向鏈路特性計算,結果如表1所示。

表1 海面到衛星鏈路預算結果Tab.1 Results of sea level to satellite link budget

(1)

式中,C/N0為接收端的載噪比;EIRP為衛星等效全向輻射功率;G/T為接收品質因數;L為鏈路損耗;k為波爾茲曼常量,k= 228.6 BJ/K。

如前所述,前向鏈路初始速率為512 kb/s,依據CCSDS132.0-B-2藍皮書[5]的建議和要求,采用(255,233)RS-CC編碼、差分正交相移鍵控(Differential Quadrature Reference Phase Shift Keying,DQPSK)調制體制。高碼率前向鏈路和反向鏈路速率為8 Mb/s時,依據CCSDS 732.0-B-2[6]的建議和要求,數據采用 (8 160,7 136)LDPC編碼、DQPSK調制體制。由表1所示的鏈路預算結果可知,鏈路余量滿足通信鏈路大于最低3 dB的要求[7],且反向鏈路余量較大,能夠確保通信鏈路的可靠建立。

1.2 技術方案

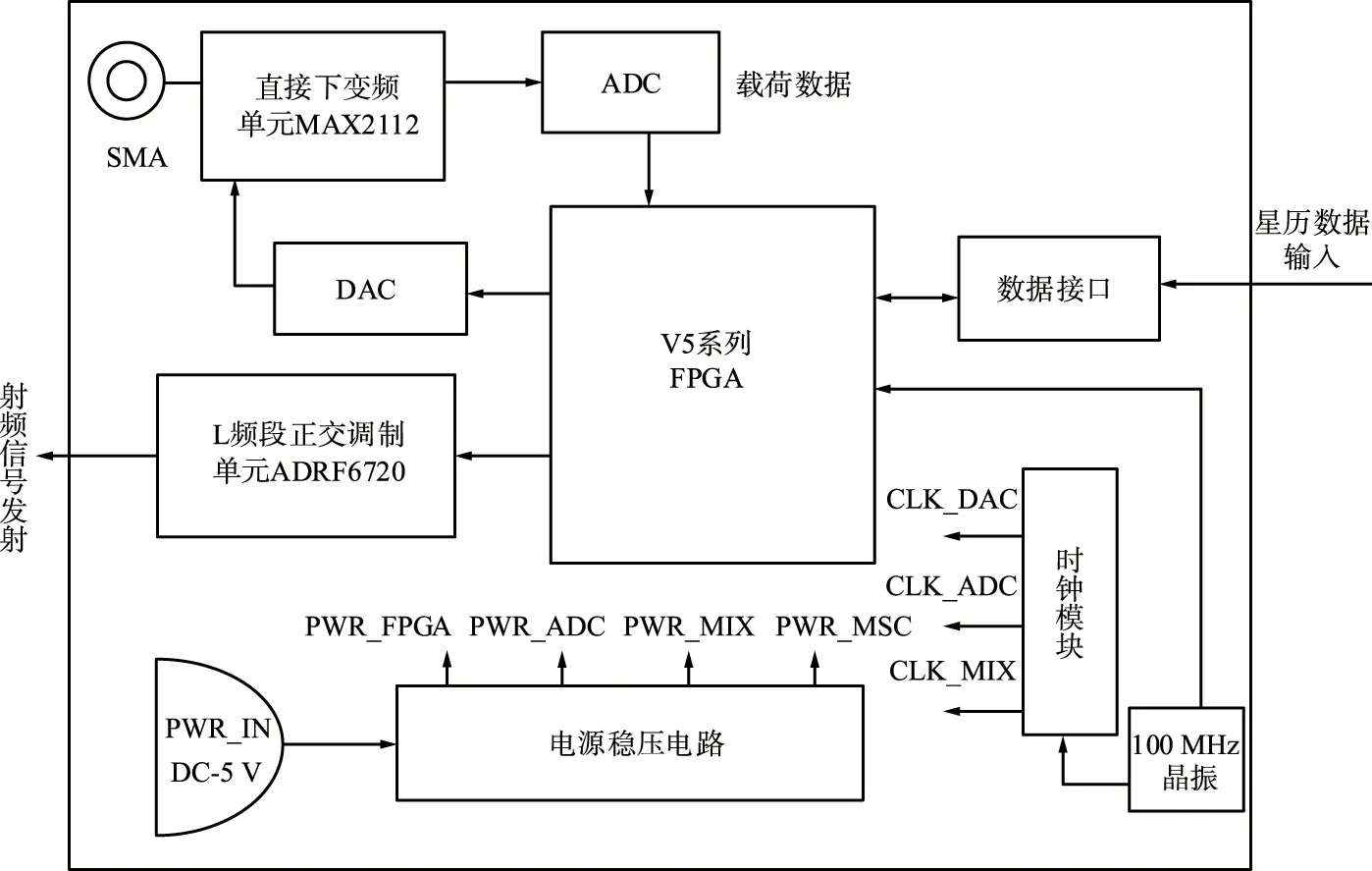

L頻段天海通信載荷數字基帶電路模塊由V5系列FPGA芯片和相關的外圍電路組成,系統框圖如圖2所示。電路包括時鐘管理模塊、正交調制模塊、電源模塊、數據接口以及直接下變頻等模塊。在FPGA內部實現與外部數據的交換、RS編碼、LDPC編碼、加擾、組幀、調制解調和模式切換等功能。基帶板集成了射頻正交調制發射模塊,基帶信號在FPGA內進行差分編碼后在調制模塊實現L波段QPSK直接調制,即完成數據的DQPSK調制輸出到功率放大器。解調模塊使用具備直接變頻功能的MAX2112芯片[8]實現將射頻信號直接變頻到基帶信號的零中頻方案。相比于超外差結構,零中頻結構的接收前端沒有中頻電路,可以減小接收端電路的體積和電路復雜度。零中頻輸出信號經模數轉換芯片AD9284[9]采樣后輸出到FPGA,該芯片雙通道差分輸入口可以實現對I,Q兩路同時采樣。為了實現零中頻接收端一定動態范圍,利用數模轉換芯片AD9744與MAX2112形成回路,用于實現自動電平增益控制(Automatic Gain Control,AGC)。

圖2 系統實現框圖Fig.2 Block diagram of system implementation

2 關鍵技術實現

2.1 工作模式切換

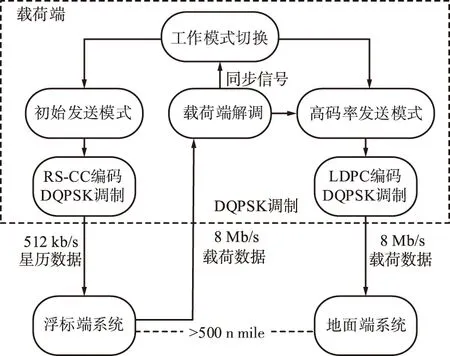

天海中繼通信載荷前向鏈路有2種工作模式:初始模式是對海面發送512 kb/s的星歷數據;高碼率模式發送8 Mb/s的數據,該數據來自載荷接收的浮標端發送的信息。載荷工作模式的切換示意如圖3所示。

圖3 工作模式切換示意Fig.3 Diagram of working mode switching

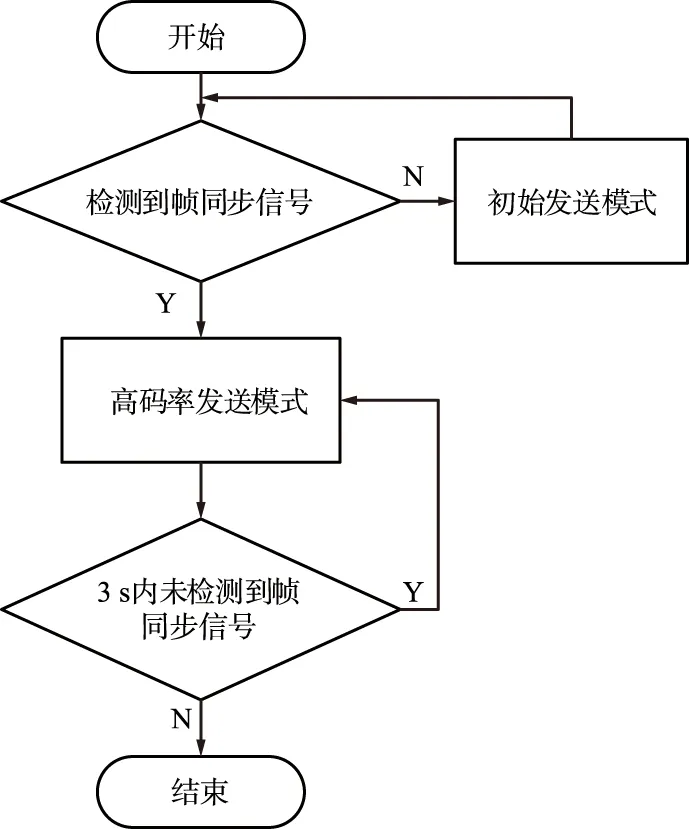

解調模塊是否檢測到幀同步信號作為載荷模式切換的依據。載荷開機后沒有收到來自海面浮標端數據,即反向鏈路沒有建立,初始模式對衛星波束覆蓋海面發送512 kb/s星歷數據。如果載荷收到浮標端的載荷數據信號,解調模塊檢測到幀同步信號,FPGA內部將切換到高碼率模式,將收到的載荷數據進行LDPC編碼調制下發至地面端系統。幀同步信號失鎖后切換回低碼率初始模式。工業級正交調制芯片ADRF6720[10]可實現將I,Q基帶數據直接調制到所需的載波頻率。因此,FPGA內實現數據切換只需要將完成編碼調制處理后輸出的I,Q兩路基帶信號進行切換,即可實現發射的工作模式切換。具體的切換流程如圖4所示。

圖4 工作模式切換流程Fig.4 Flowchart of working mode switching

為了確定載荷數據是否發完,在FPGA內使用計數器進行判斷。幀同步信號為單脈沖信號,檢測到幀頭時輸出一個脈沖信號。以32 kHz的時鐘作為計數器的驅動時鐘,在檢測到每個幀同步脈沖時將計數器復位,同時將指示信號拉高,工作模式切換為高碼率模式;若接收不到幀同步信號時則在時鐘的驅動下開始計數,計數器若計到設定的值時仍未檢測到幀同步信號則認為已失去同步,此時將指示信號拉低,工作模式切換成初始發送模式。本設計中計數器值設定為96 000,即在3 s內未檢測到幀同步信號時切換工作模式。

2.2 低碼率數據編碼

初始模式發送星歷數據時使用級聯的RS(223,255)外碼、速率適配的(2,1,7)卷積內碼實現交織編碼。由于星歷數據量較小,采用這種實現簡單且延時較小的編碼技術,能夠在滿足編碼增益需求和帶寬限制的同時節省星上資源[11]。

系統時鐘為100 MHz外部晶振輸入,在FPGA內使用DCM ip核完成分倍頻后產生系統功能模塊所需要的工作時鐘。星歷數據編碼調制后速率為512 kb/s,FPGA內部所需時鐘分別為32,256,512 kHz;同時,時鐘產生功能模塊輸出8 MHz和1 MHz時鐘,作為LDPC編碼以及后續調制模塊的參考時鐘。

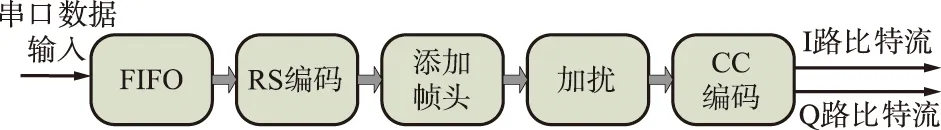

星務計算機通過異步串口RS422以1 Hz的頻率,115 200波特率將83 byte長度的一幀星歷數據發送給載荷的數字處理單元,載荷將接收到的數據送入編碼調制模塊。由于數據接收時鐘和后一級RS編碼模塊的時鐘頻率不同,使用異步FIFO對數據進行緩存,以解決跨時鐘域可能產生的亞穩態問題。輸入數據長度和編碼所需的255 byte長度不一致,故使用狀態機控制FIFO的讀寫狀態,確保在一幀星歷數據寫入FIFO后再進入讀數據狀態。星歷數據具體編碼流程如圖5所示。

圖5 星歷數據編碼流程Fig.5 Ephemeris data encoding process

編碼后完整的數據幀包含4 byte幀頭,共259 byte,以8 bit并行傳送,同時輸出幀頭指示信號。加擾模塊根據幀頭指示信號選擇性加擾,對除同步幀頭以外的傳輸幀數據加擾。卷積編碼模塊對加擾后的信號進行卷積操作,將其碼率倍增到512 kb/s。

2.3 高碼率數據編碼

衛星星上資源有限,星上載荷在尺寸、質量和功耗等方面均有限制[12],設備發射功率不可能無限制提升,因此選擇優異的信道編碼方案來獲得可觀的信道增益,有效降低信號解調門限[13]。

前向鏈路高碼率模式時,受限于衛星端搭載天線的發射功率和帶寬等因素,高碼速率模式的反向鏈路和前向鏈路中選取高編碼增益、低誤碼及譯碼性能逼近香農限的LDPC編碼[14]。

數據傳輸時使用7/8碼率的(8 160,7 136)LDPC編碼方案。該方案推薦使用的校驗矩陣H的第一大行和第二大行均屬于準循環低密度奇偶校驗碼(Quasi-Cyslic LDPC,QC-LDPC)[15],采用簡單的移位寄存器即可實現編碼計算,有利于硬件電路的實現。

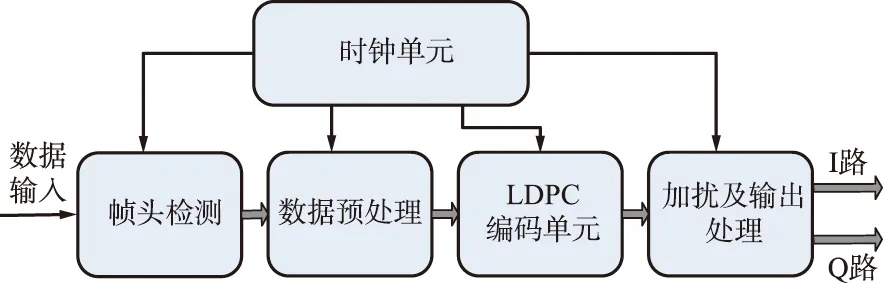

LDPC編碼單元由6個功能單元組成,如圖6所示,包括時鐘單元、幀頭檢測單元、數據預處理單元、LDPC編碼單元和輸出處理單元。其中,幀頭檢測單元檢測數據幀格式是否符合設計要求,該模塊檢測到幀頭1ACFFC1D后給出使能信號控制下一級數據預處理模塊開始工作。數據預處理單元完成對數據的并串轉換以及填充等處理,使碼字長度符合生成矩陣的基矩陣格式后,再送入編碼核心單元進行編碼。

圖6 載荷數據編碼流程Fig.6 Payload data coding process

編碼單元通過信息位碼元求出校驗位碼元。由文獻[16]中對LDPC編碼算法原理的推導可知,計算校驗位即計算信息位碼元序列與生成矩陣的非單位陣部分做矩陣乘法運算的結果,G矩陣為系統碼矩陣,G=[IkQ]生成碼字C表示為C=q·G,q為待編碼數據。

在實際設計中使用移位寄存器累加(Shift Register Adder Accumulator,SRAA)編碼電路來實現運算。在綜合比較了串行編碼和并行編碼的優缺點后,本文采用了改進結構的8位并行編碼方案,在提高編碼速率的前提下減少了資源的消耗。具體設計的并行編碼結構如圖7所示。

圖7 8位并行編碼結構Fig.7 8-bit parallel coding structure

編碼完成后,使用Cortex高碼率接收機(High Data Rate Receiver,HDR)對編碼調制后信號的誤碼率進行測試。在Eb/N0>4.0 dB時,誤碼率小于10-6,滿足設計需求。

2.4 DQPSK調制解調

調制部分采用DQPSK體制,利用前后相鄰2個碼元的相位差傳遞數據,以解決解調過程中的相位模糊、相位翻轉的問題。在FPGA內將原始絕對碼經過差分編碼后變成相對碼,再將差分編碼后的I,Q兩路基帶信號送入正交調制單元完成載波調制。在FPGA內通過SPI通信配置射頻調制芯片ADRF6720內部寄存器,使輸出增益達1 dBm,載波中心頻率為1 521.5 MHz。

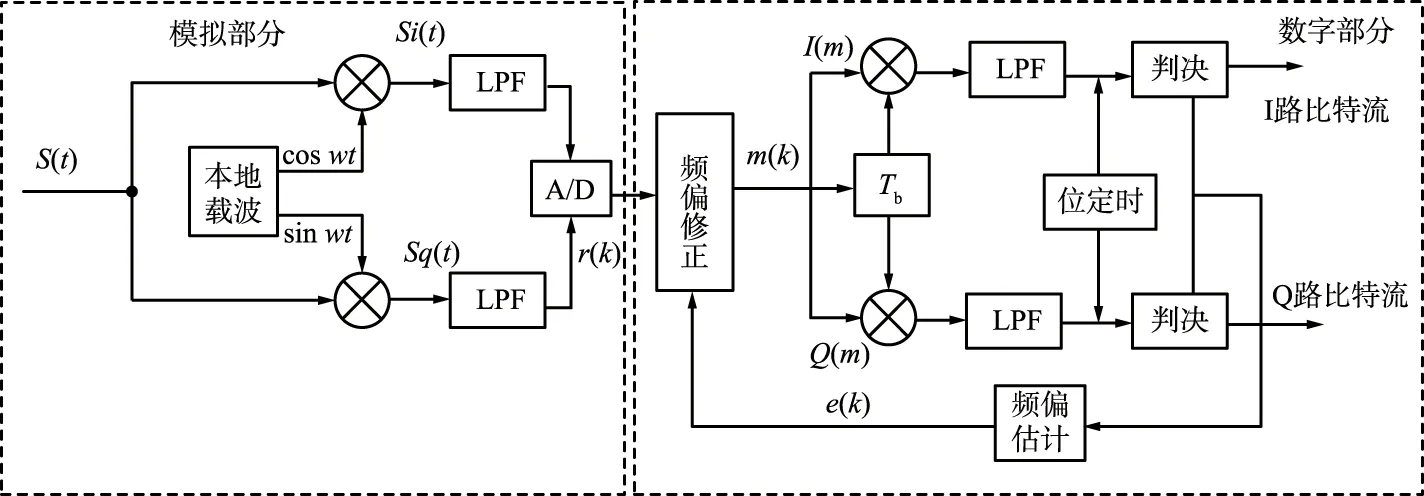

解調部分采用非相干解調以克服信號衰落變化大、頻移特性變化大的缺陷[17]。零中頻解調的結構如圖8所示。

圖8 零中頻解調結構Fig.8 Homodyne IF demodulation structure

模擬部分中MAX2112對載波下變頻后輸出16 MHz中頻信號,經模數轉換芯片采樣后得到I,Q兩路信號,送入FPGA進行非相干解調。數字解調模塊中的延時處理使用移位寄存器實現,對濾波后的輸出信號延時一個符號周期16個采樣點。將AD采集的輸入信號I路經Hillbert濾波器后變為相位差π/2的2路信號I(m)與Q(m),分別與延時Tb后的信號相乘,相乘后的信號經低通濾波器后再進行后續位同步判決過程,完成非相干解調。

低軌衛星與地面之間存在高速的相對運動,因此在解調時需要考慮多普勒效應導致的頻率相位偏移的影響。根據計算,可得500 km處該衛星過境時,多普勒頻移約為±50 kHz,為了避免多普勒效應導致的接收信號相位差的錯判[18],接收端采用反饋環路進行修正的算法對多普勒頻偏實現補償。如圖8的數字部分結構所示。

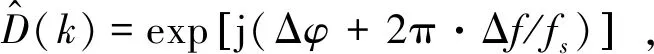

不考慮噪聲影響,未校正前的r(k)=A(k)exp[j(φk+θk)],在解調模塊中與延時一個周期后的信號相乘得到:

D(k)=r(k)·r(k-Ts)=As(k)exp[j(Δφ+Δθk)],

(2)

式中,Δφ為在發送端相距Ts時刻的調制信號的相位差信息;Δθk為相距Ts時刻之間的信息由頻偏引起的相位偏差,Δθk=2π·Δf/fs。

(3)

將e(k)送回頻偏修正模塊與未校正的信號相乘,得到修正后的m(k):

m(k)=r(k)·e(k)=A(k)exp(jφk)。

(4)

此時多普勒頻偏的影響被消除。該方法能夠消除的最大頻偏由硬判決Δφ估計值精度決定,實際測試表明,本設計完成修正后能夠正確解調±100 kHz頻偏的信號。

3 測試結果

基帶單元所有編碼、調制、解調及和衛星系統間的通信接口等功能均在FPGA芯片的XC5VSX50T-2FFG1136I 中完成。

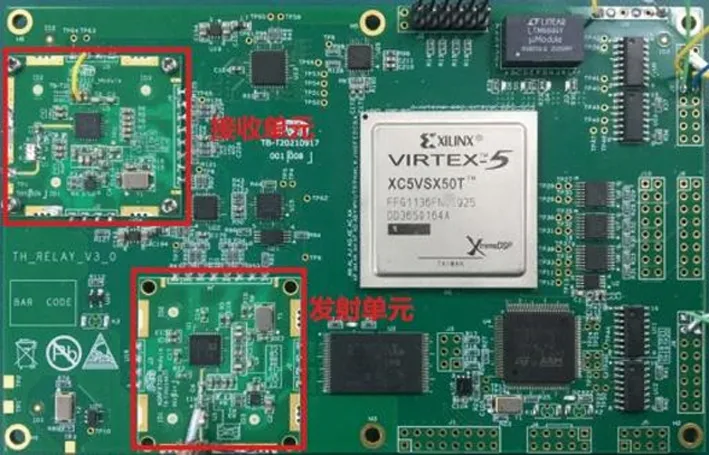

整個收發系統有較高集成度,系統采用整板SMT的封裝結構。基帶信號處理電路照片如圖9所示。

圖9 數字信號處理板照片Fig.9 Digital signal processing board

射頻接收與發射模塊采用介電常數穩定的微波板材制成獨立模塊再焊接到信號處理單元母板上,以隔離射頻模擬電路和數字電路之間的干擾。

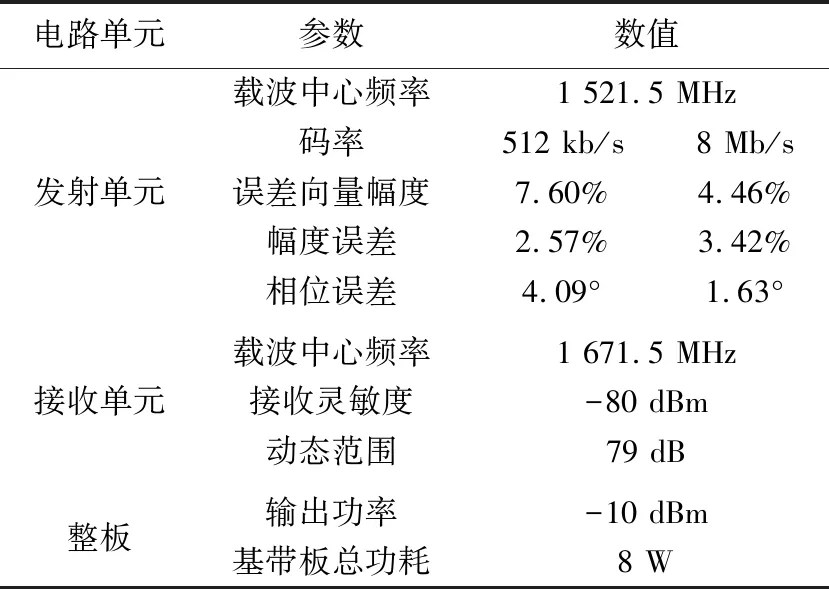

基帶電路輸出特性的測試結果如表2所示。

表2 基帶電路輸出特性Tab.2 Baseband circuit output characteristics

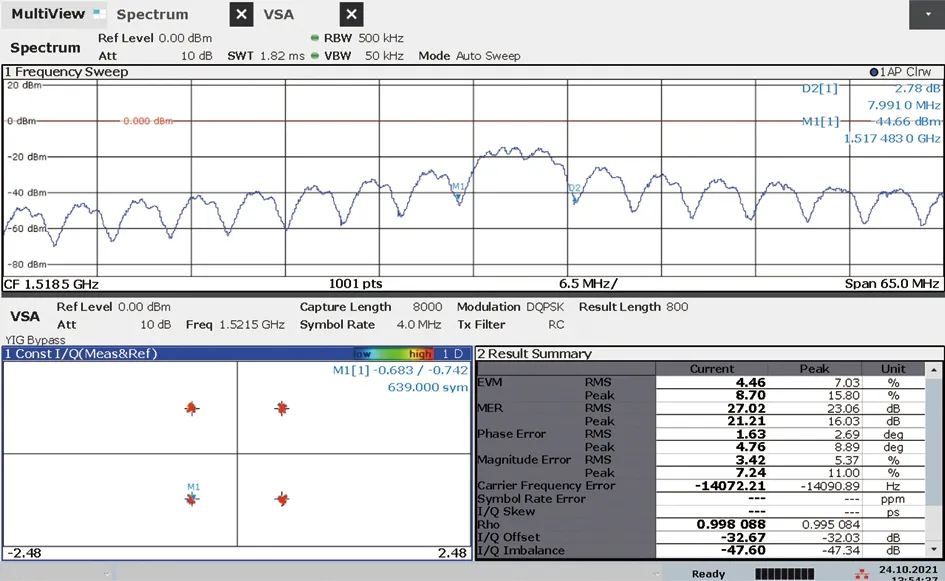

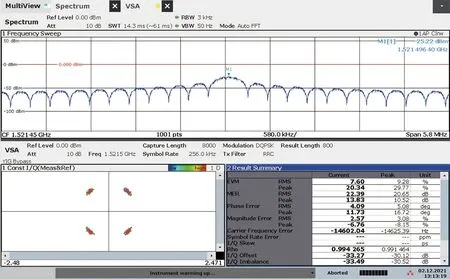

8 Mb/s和512 kb/s碼率的DQPSK調制信號星座圖和矢量誤差幅度(EVM)如圖10和圖11所示。

圖10 8 Mb/s LDPC+DQPSK調制頻譜及星座圖Fig.10 8 Mb/s LDPC+DQPSK modulation spectrum and constellation diagram

圖11 512 kb/s RS-CC+DQPSK調制頻譜及星座圖Fig.11 512 kb/s RS-CC+DQPSK modulation spectrum and constellation diagram

EVM分別為4.5%和7.6%,滿足應用性能指標,幅度誤差分別為3.42%(0.29 dB)和2.57%(0.22 dB),相位不平衡度分別為1.63°和4.09°,完全滿足CCSDS的幅度誤差(小于0.5 dB)和相位不平衡度(小于5°)要求。誤碼率測試借助運行在電腦端的模擬數據發送軟件和數據解幀軟件完成,通過對比統計編碼調制前的發送數據和解調解碼后的數據,計算出前向和反向鏈路的誤碼率。實際通信測試中,前向鏈路實測誤碼率穩定在1.2×10-6~1.5×10-6,此時接收信號的Eb/N0約為13 dB;反向鏈路實測誤碼率為10-7~10-6,均小于CCSDS標準規定的10-5,滿足通信鏈路的可靠性要求。

數字板的零中頻接收模塊通過數模轉換芯片AD9744實現AGC,FPGA內對ADC采樣的輸出進行峰峰值檢測,再由軟件設定判決,實時輸出增益控制字控制AD9744的輸出電壓幅值實現AGC,最終動態增益范圍可達79 dB。對射頻信號接收靈敏度進行測試,在Eb/N0為18 dB時,接收靈敏度為-80 dBm。整板功耗為8 W左右,滿足低功耗設計需求。

4 結束語

本文實現了天海中繼載荷數字基帶電路單元的設計。根據實際需求完成了硬件電路研制和軟件程序的測試。研究了載荷前向鏈路在不同工作模式下的信道編碼及調制解調功能,根據數據鏈路特點實現了工作模式的自動切換。根據信道特點,優化了LDPC編碼算法以及對解調過程中的多普勒頻移進行了校正。測試結果表明,基帶電路單元能夠滿足低軌衛星通信前向和反向鏈路的工程應用需求。設計的數字基帶處理單元僅支持固定碼速率的數據傳輸,在后續的研究中,將結合可變編碼調制(Variable Coding Modulation,VCM)技術進一步提高信號的傳輸效率。