基于FPGA 圖像處理的內窺鏡焊點檢測系統

賈晨鑫,張榮福,任夢圓,徐朝輝,龔姬央丹,劉翰林

(上海理工大學 光電信息與計算機工程學院,上海 200093)

引言

內窺鏡作為現代醫學的重要設備,隨著制造業的不斷發展,實現內窺鏡信號線的自動焊接已成為一個必然的趨勢。在生產制造過程中,焊點檢測系統作為自動焊接平臺的前端系統起著重要作用,通過檢測到的焊點坐標配合三軸移動平臺完成自動化焊接,可以極大地提高生產效率,減小生產成本。

近年來,國內外學者針對焊點檢測做了許多分析與研究。Bunyak 等提出一種PCB 有效層檢測算法,對焊點的圓心、半徑和形狀有較高的檢測效率[1]。Mar 等設計出一種基于機器視覺的PCB 焊點自動檢測系統,通過光照歸一化減小光源影響,將圖像從RGB 顏色空間轉換為YIQ顏色空間,從而提高焊點檢測精度[2]。王梅梅以機器視覺技術為核心,通過對PCB 板圖像進行分割,將感興趣區域(ROI)從圖像中分離出來,提高了焊點定位的精度,同時減小計算量[3]。但基于機器視覺的焊點檢測技術需要使用圖像采集卡和PC 端,從而達不到實時檢測的目標,同時成本高且不利于攜帶。此外也有基于DSP[4-5]的焊點坐標檢測技術,這種方法可以利用DSP 將圖像信號采集和圖像處理兩個模塊連接起來,但由于DSP 內部程序的執行方式是串行的,這使得該系統在圖像采集速度以及處理速度等方面存在劣勢。

針對上述問題,本文設計了一種基于FPGA 圖像處理的內窺鏡焊點檢測系統。該系統以FPGA作為主控器控制圖像信號的采集、圖像處理、焊點檢測以及圖像信號的傳輸,利用FPGA 并行執行的優勢實現對目標板焊點坐標的提取,具備檢測效率高,成本低,易攜帶,實時性強等特點。

1 系統總體概述

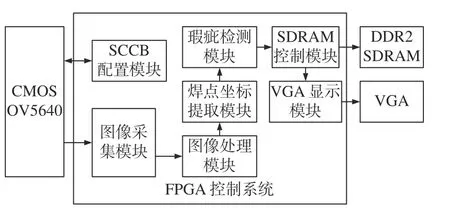

基于FPGA 圖像處理[6]的內窺鏡焊點檢測系統的整體設計如圖1 所示。整個系統主要由圖像采集模塊、圖像處理模塊、焊點坐標提取模塊、瑕疵檢測模塊、SDRAM 控制模塊和VGA顯示模塊組成。FPGA 芯片作為主控器件通過SCCB 總線協議對OV5640 進行初始化的配置。圖像采集模塊在FPGA 的控制下對OV5640 輸出的圖像信號進行采集,以單通道灰度圖像形式輸出采集結果。圖像處理模塊將采集到的圖像進行中值濾波去噪,并采用Sobel 邊緣檢測算法提取圖像中的邊緣信息。焊點坐標提取模塊的功能是構建像素坐標系,根據檢測到的邊緣信息對焊點坐標進行采集,并對采集到的坐標進行效驗。瑕疵檢測模塊主要利用采集到的焊點坐標進行檢測區域分割,在分割的區域內進行瑕疵的判別。圖像數據經過處理后將傳送到SDRAM[7]中存儲,由于系統時鐘快和數據吞吐量大的特點,這里使用16 bit 寬和1GB 容量的DDR2 SDRAM 進行圖像的存儲和處理,大大提高了視頻顯示的流暢性和實時性。最終通過VGA 實時的顯示檢測結果,極大地提高了調試效率。

圖1 系統整體框圖Fig.1 Overall block diagram of the system

2 圖像采集與處理的FPGA 實現

2.1 圖像采集模塊設計

圖像采集模塊主要是由兩部分組成,包括OV5640 圖像傳感器的初始化模塊和圖像信號采集模塊。初始化模塊在系統上電復位穩定后,根據預先存放在寄存器中的參數,通過SCCB 通信協議[8]對控制OV5640 輸出圖像大小和輸出圖像模式的寄存器進行配置,使OV5640 圖像傳感器輸出的圖像分辨率為1 280×720,圖像信號模式為RGB565。在正常工作模式下,圖像采集模塊根據OV5640 輸出的行同步信號采集圖像數據,得到三通道彩色圖像。為了在后續高速信息處理下減小數據量,提高數據處理的速率,系統將三通道彩色圖像轉換成單通道的灰度圖像作為輸出并傳到下一模塊進行進一步處理。

2.2 滑動窗口設計

在一些經典的圖像處理如Sobel 邊緣檢測、中值濾波、高斯濾波以及模糊濾波等,都需要窗處理方式以便運算操作。系統采用硬件描述語言生成3×3 圖像滑動窗口,不僅可以實現算法的加速,同時滿足對整幅圖像的處理。

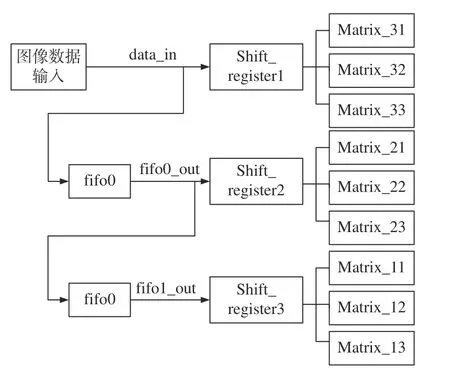

FPGA 硬件實現結構圖如圖2 所示。FPGA使用兩個fifo 實現3×3 的滑動窗口,設定每個fifo 的深度為1 280(圖像一行像素的個數),數據位寬為8 bit。當fifo0 和fifo1 全部寫滿時,下一時鐘上升沿輸出的data_in、fifo0_out 和fifo1_out就是圖像連續三行的數據,同時保持列對齊。將data_in、fifo0_out 和fifo1_out 分別利用移位寄存器經過兩個周期的延時得到3×3 窗口。

圖2 3×3 滑動窗口生成圖Fig.2 3×3 slide window to generate graph

2.3 中值濾波算法的硬件設計

中值濾波[9]是一種能有效抑制噪聲的非線性信號處理技術,在圖像處理中對保護邊緣信息具有良好的效果,實現原理是將某一像素點值用其領域內的中值所代替。

得到3×3 滑動窗口后,以流水線思想為理論基礎進行中值濾波算法的硬件設計。在一級流水線處理中內設3 個sort(三輸入排序模塊),分別對3×3 窗口的每一行數據進行排序,得到每行的最大值、最小值和中值。在二級流水線處理中,將3 個最大值、3 個最小值和3 個中值分別通過sort 模塊排序處理,找出3 個最大值中的最小值,3 個最小值中的最大值和3 個中值中的中間值。最后,三級流水線將上級輸出的3 個值通過sort 模塊再次排序處理,得到中值。

2.4 邊緣檢測算法的硬件設計

系統采用Sobel 邊緣檢測算法[10-11],該算法可以良好的保留檢測焊點的輪廓信息并剔除目標板的背景顏色。為保證整個系統的實時性,算法的FPGA 硬件實現首先需要使用3×3 滑動窗口對濾波后的圖像進行存儲,利用內部設定的橫向與縱向卷積因子模板分別與滑動窗口進行卷積,得到橫向與縱向的圖像灰度值,即Gx與Gy。Sobel 算子模板如下。

梯度幅值Gr的硬件設計則是利用FPGA 開發板內部的開平方根IP 核來實現運算過程。將得到的梯度幅值與特定的閾值相比較判斷是否為邊緣信號。

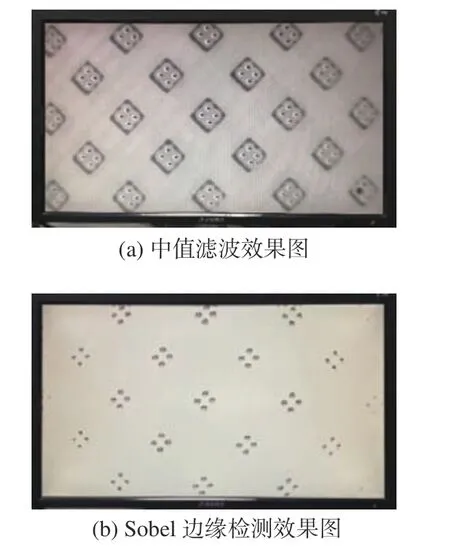

圖像處理效果如圖3 所示。

圖3 圖像處理效果圖Fig.3 Effect of image acquisition

3 焊點檢測算法的FPGA 實現

焊點檢測算法主要包括焊點坐標提取、焊點坐標效驗以及目標板瑕疵檢測。為實現焊點檢測,需要先對焊點的坐標進行采集。由于目標板在經過圖像處理模塊后可以良好的保留焊點邊緣,因此可以利用邊緣坐標比較法對焊點坐標提取,其原理是根據每個焊點的位置關系,通過邊緣信號搜索和邊緣坐標位置的實時比較來提取焊點坐標。

3.1 焊點坐標提取

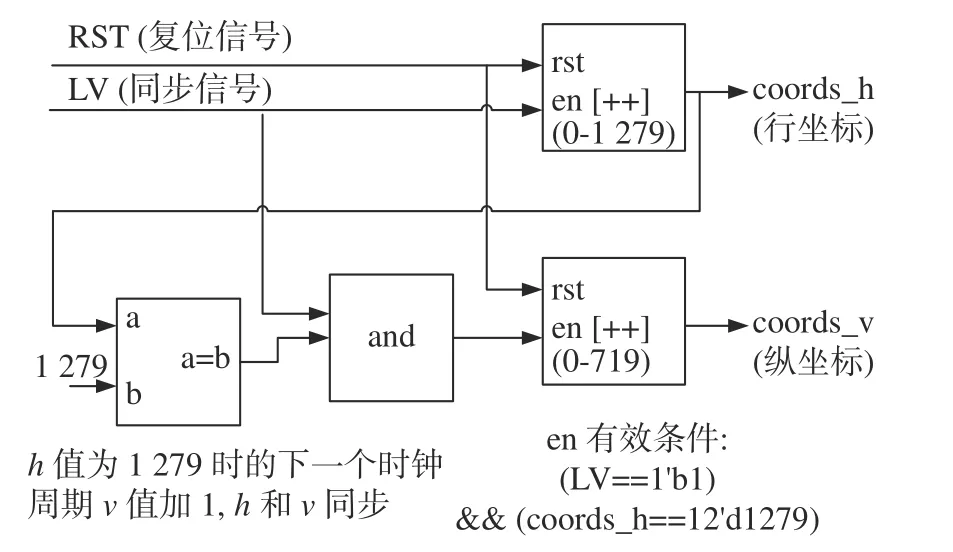

實現焊點坐標的提取需構建像素坐標系,在一級流水線處理中系統根據像素同步信號對每個輸入的像素點賦予坐標信息,像素坐標系模塊的硬件設計結構如圖4 所示。

圖4 像素坐標系實現結構圖Fig.4 Structure of pixel coordinate system

邊緣信號采集模塊利用自定義位寬的移位寄存器進行設計,移位寄存器的位寬可根據采集情況進行調整,以6 位寬的移位寄存器為例,該模塊根據同步信號對當前輸入的圖像信號進行判斷。由于處理過后的圖像為二值圖像,當輸入的圖像信號為黑色點像素,移位寄存器向左移一位,最低位賦1,否則最低位賦0。

移位寄存器[12]的值作為邊緣信號采集的重要條件。當移位寄存器內部全為0 時,表示檢測到了背景區域;當移位寄存器內部不全為1 時,表示檢測到了噪聲信號或即將檢測到焊點邊緣;當移位寄存器內部全為1 時,表示檢測到了焊點的邊緣信息。由于FPGA 內部并行處理的特性,此時像素坐標系模塊輸出的坐標可以作為焊點邊緣的坐標進行存儲。

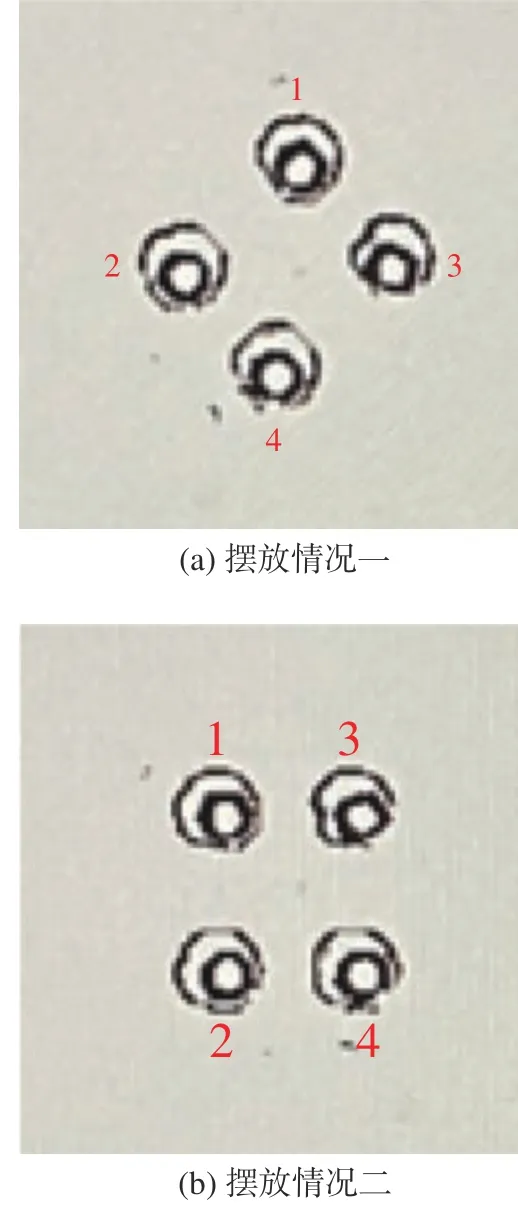

在FPGA 內部設計的邊緣坐標采集模塊從每幀圖像的第一個像素點開始依次遍歷每個像素點。在邊緣信號采集過程中,系統會檢測到很多的焊點邊緣,通過利用各焊點的位置特征對邊緣坐標進行比較,可以精確提取各個焊點的坐標。在實際的檢測過程中,目標板隨機擺放時,焊點的位置特征存在不同情況如圖5 所示。

圖5 目標板隨機擺放圖Fig.5 Random placement of the target board

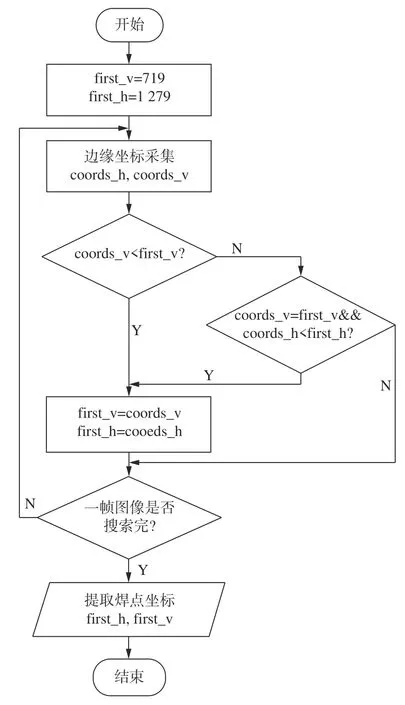

在對1 號焊點坐標提取前,通過觀察目標板隨機擺放情況可以看出,1 號焊點的縱坐標最小,但在圖(b)中縱坐標最小的焊點包括3 號焊點。因此,在邊緣信號采集過程中,通過邊緣坐標比較,找出縱坐標最小的邊緣坐標,若存在多個則將行坐標最小的邊緣坐標作為1 號焊點的邊緣坐標,經效正后得到焊點的中心坐標,其余焊點坐標的提取與之類似,硬件設計邏輯流程圖如圖6 所示。

圖6 焊點坐標采集流程圖Fig.6 Flow chart of welding point coordinate acquisition

FPGA 內設8 個寄存器用來對每幀圖像的檢測區域內4 個焊點的坐標進行存儲。在三級流水線處理中,坐標效驗是根據采集到的焊點坐標計算出相鄰兩焊點坐標之間的距離,并與特定的閾值相比較進行判斷。閾值由目標板各點之間的固定間距轉換到像素坐標系下進行設定。如果兩坐標之間的距離超出閾值范圍,則判定目標板不合格,FPGA 內設的flag 信號將會拉高,產生的flag 信號用來控制蜂鳴器發出警報或者控制分揀裝置。

3.2 瑕疵檢測

在使用檢測合格的焊點坐標進行自動化焊接前,對目標板進行瑕疵檢測,即判別各個焊點間無短路和余銅現象,有利于產品質量的進一步提升。

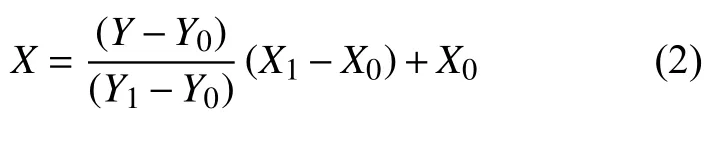

瑕疵檢測區域的邊界分割函數為

式中:(X0,Y0)和(X1,Y1)為連續兩個焊點的坐標;(X,Y)為線性區域分割的邊界坐標。該模塊的硬件設計是將采集到的合格焊點坐標利用式(2)進行線性區域分割。根據4 個焊點的坐標位置構建線性區域分割模型如圖7 所示。

圖7 線性區域分割模型Fig.7 Linear region segmentation model

系統通過在線性分割的區域內采集邊緣信號來實現瑕疵檢測。對瑕疵邊緣的采集利用邊緣信號采集模塊,通過適當調整模塊內部移位寄存器的位寬,可以提高對瑕疵邊緣的采集精度。將采集到邊緣信號的數值與設定的閾值相比較,若超出設定的閾值范圍系統將發出警報,同時將檢測區域內的瑕疵用紅色像素點顯示,有利于工作人員更直觀地發現目標板上的瑕疵所在。

4 實驗結果與總結

本系統的硬件測試平臺如圖8 所示,焊點檢測系統采用Altera Cyclone IV E FPGA 系列的EP4CE30F23C8 作為主控芯片,驅動OV5640 圖像傳感器進行焊點圖像的采集與處理工作。在Altera 公司的Quartus II 13.0 開發環境中,以Verilog HDL 硬件描述語言完成圖像信號采集模塊、圖像處理模塊、焊點檢測算法、瑕疵判別算法和VGA 驅動模塊的硬件設計。將設計好的硬件電路配置文件下載到FPGA 中,在系統上電復位后顯示器上顯示出清晰的焊點畫面。

圖8 測試平臺Fig.8 Test platform

4.1 焊點坐標檢測測試

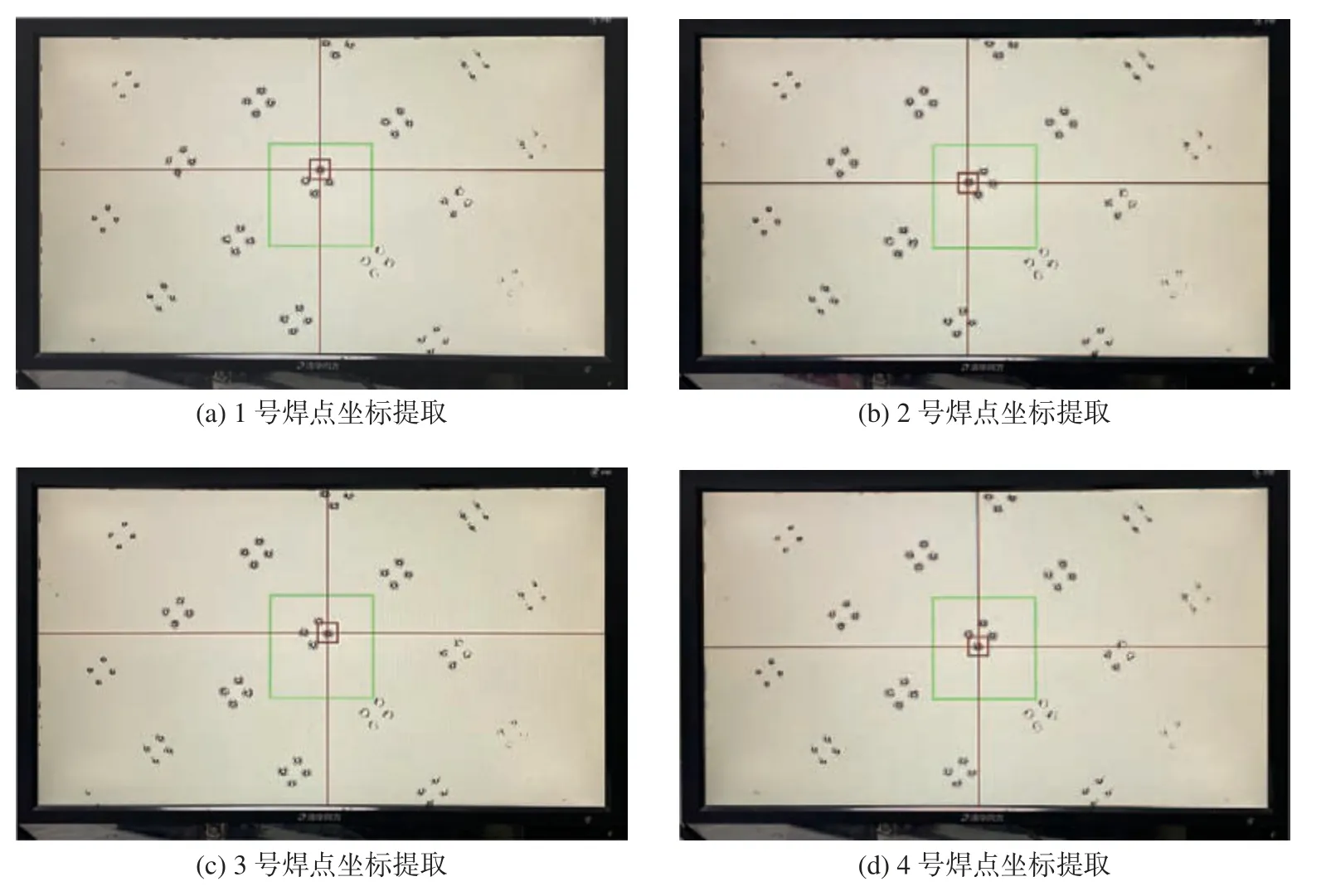

系統設置綠框標記的區域作為檢測區域,對區域內部的目標板進行檢測。為了直觀地顯示檢測到的焊點坐標,采用十字光標法對坐標進行標記,焊點坐標提取效果圖如圖9 所示。可以看出十字光標的中心位置位于焊點上,當目標板在檢測區域內移動時,十字光標也跟隨焊點位置移動,具有實時性。

圖9 焊點坐標提取圖Fig.9 Extraction of coordinates of solder joint

4.2 坐標檢測誤差分析

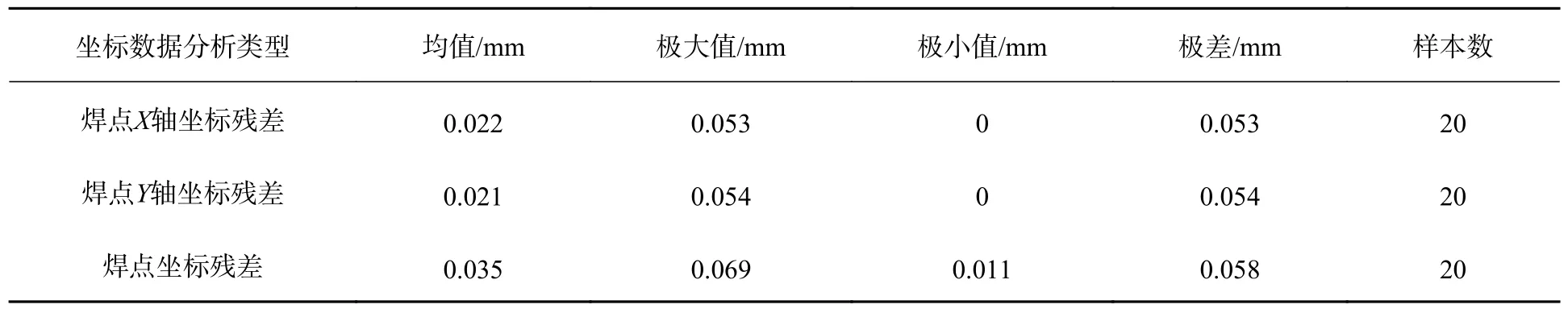

為驗證系統檢測坐標的精確性和可靠性,將系統自動檢測到的像素坐標經過坐標轉換后與人工標定得到的實際坐標進行比較,根據獲取的數據計算坐標殘差。由于1 個目標板共有4 個焊點,這里對5 個目標板進行檢測,共得到20 個焊點的坐標信息,經過計算和分析后,對比結果如表1 所示。

表1 檢測坐標與實際坐標對比Tab.1 Comparision between the detected coordinates and the actual coordinates

對系統檢測的焊點坐標進行統計分析,結果如表2 所示。

系統要求所測得的坐標誤差不超過0.1 mm,由表2 可以看出系統檢測到的坐標與實際坐標誤差范圍在0~0.07 mm 以內,在X軸和Y軸上坐標誤差范圍在0~0.06 mm 以內,最大誤差都小于0.1 mm。實驗表明,經系統檢測得到的焊點坐標在精度上達到了設計要求,可以運用到自動化焊接系統中。

表2 焊點檢測實驗結果分析Tab.2 Analysis of experimental results of welding spot detection

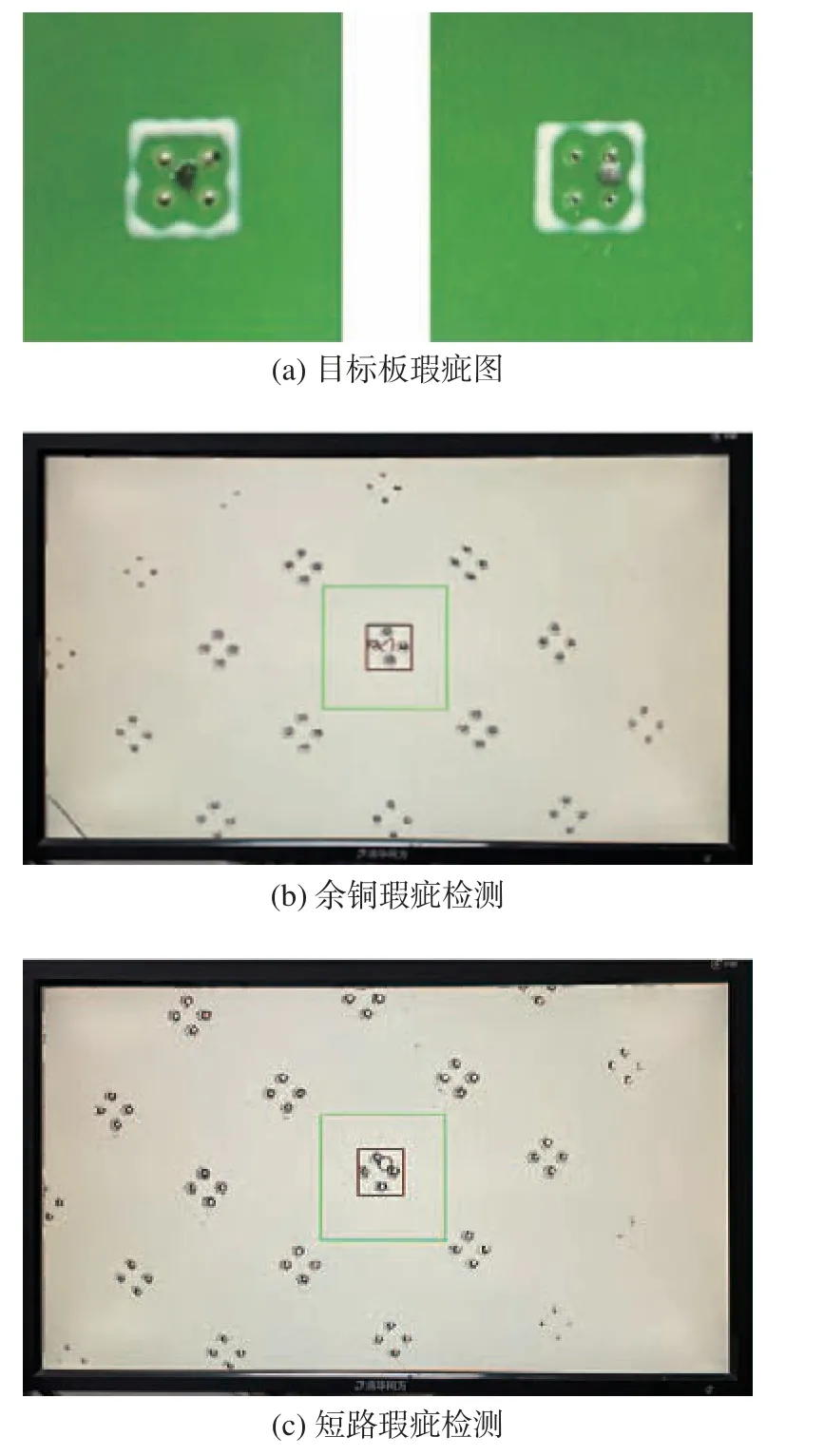

4.3 瑕疵檢測測試

目標板瑕疵檢測效果圖如圖10 所示,圖(a)中的兩個目標板在4 個焊點之間均存在約0.04 mm2的余銅。對圖(a)中兩塊目標板的瑕疵檢測結果如圖(b)、圖(c)所示,系統設置屏幕中心綠框所標記的240×240 像素區域作為檢測區域,對區域內部的目標板進行瑕疵檢測,存在瑕疵的目標板將被紅色方框所標記并以紅色像素點顯示檢測到的瑕疵邊緣。

圖10 目標板瑕疵圖Fig.10 Defect of target plate

5 結論

本文在分析內窺鏡信號線自動焊接的需求后,設計了一種基于FPGA 的內窺鏡焊點檢測系統。主要介紹系統以FPGA 為核心,與外圍硬件實現圖像采集、圖像處理、焊點檢測和瑕疵判別算法,將檢測到的焊點像素坐標進行標記,通過VGA 實時顯示處理結果。實驗結果表明,本文設計的內窺鏡焊點檢測系統具有實時性,對焊點的檢測精度≤0.1 mm,工作穩定,體積小便于攜帶,滿足系統設計的技術指標,具有實際使用價值。