一種高速軌到軌輸出差分放大器設(shè)計(jì)

范國(guó)亮,黃治華,何崢嶸,徐佳麗

(中國(guó)電子科技集團(tuán)公司第二十四研究所,重慶 400060)

目前,電子系統(tǒng)對(duì)功耗和電源電壓的要求越來越苛刻,尤其是消費(fèi)電子、可穿戴設(shè)備、生物電子等普遍采用電池供電的領(lǐng)域。作為系統(tǒng)中連接ADC 和DAC 數(shù)據(jù)轉(zhuǎn)換器等高速模塊的關(guān)鍵元件,差分放大器的性能產(chǎn)生極大影響[1-3]。功耗的降低意味電流消耗的減小,這會(huì)導(dǎo)致速度(壓擺率和帶寬)和驅(qū)動(dòng)能力的降低;電源電壓的降低直接導(dǎo)致放大器可用或可處理信號(hào)幅度的降低,這會(huì)引起數(shù)據(jù)轉(zhuǎn)換器信噪比降低,進(jìn)而降低分辨率,影響系統(tǒng)性能。盡管采用傳統(tǒng)的差分放大器可以在一定程度改善以上出現(xiàn)的問題,但是隨著供電進(jìn)入5 V 甚至3.3 V 等更低的范圍,傳統(tǒng)的差分放大器已經(jīng)不能滿足要求,需要性能更強(qiáng)的差分放大器解決低壓低功耗條件下驅(qū)動(dòng)數(shù)據(jù)轉(zhuǎn)換器的問題[1-3]。

朱樟明和Stocksatd 等[4-5]基于CMOS 襯底驅(qū)動(dòng)技術(shù)實(shí)現(xiàn)了差分放大器的軌到軌輸出,但是直流開環(huán)增益只有52 dB,單位增益帶寬只有2.5 MHz,嚴(yán)重限制了高精度和高速應(yīng)用。Michael 等[6]基于自偏置技術(shù)把差分輸出放大器的增益和帶寬分別提高到71 dB 和35 MHz[6],指標(biāo)改善極其有限,且無(wú)法實(shí)現(xiàn)軌到軌輸出,采用開關(guān)技術(shù)進(jìn)行共模控制也增加了電路的復(fù)雜度和噪聲。Timo 等[7-13]采用深亞微米或異質(zhì)結(jié)工藝,將帶寬拓展到GHz 以上,但是普遍存在工藝復(fù)雜、成本極高、精度差、壓擺率低、輸出擺幅小等問題。

針對(duì)上述問題,本文基于自主高速互補(bǔ)雙極工藝,提出了一種新型的具有軌到軌輸出的高速差分放大器,采用Class AB(AB 類推挽)共射放大輸出級(jí)實(shí)現(xiàn)接近軌到軌輸出和大輸出驅(qū)動(dòng)能力,連續(xù)共模反饋結(jié)構(gòu)確定直流共模電平,多級(jí)放大結(jié)構(gòu)實(shí)現(xiàn)100 dB 高增益,嵌套式密勒(Nested Miller)補(bǔ)償?shù)姆绞竭M(jìn)行頻率補(bǔ)償[14-15],實(shí)測(cè)帶寬和壓擺率分別達(dá)到400 MHz 和1300 V/μs,從而在低壓低功耗條件下實(shí)現(xiàn)差分放大器軌到軌輸出和高速度,為保持和改善數(shù)據(jù)轉(zhuǎn)換器以及整體系統(tǒng)的性能奠定了基礎(chǔ)。

1 差分輸出放大器的電路結(jié)構(gòu)與設(shè)計(jì)

1.1 整體電路結(jié)構(gòu)

圖1 是本文提出的差分輸出放大器結(jié)構(gòu)框圖。整個(gè)電路主要由四部分組成: 輸入級(jí)、求和電路、輸出級(jí)和共模反饋電路。輸入級(jí)是一個(gè)H 橋結(jié)構(gòu)的差分輸入輸出結(jié)構(gòu)的放大電路,實(shí)現(xiàn)差分輸入電壓到電流的轉(zhuǎn)換,其詳細(xì)原理將在1.2 小節(jié)論述。求和電路本質(zhì)上是一個(gè)帶射極反饋電阻的共射極放大電路,其詳細(xì)原理將在1.3 小節(jié)論述。輸出級(jí)由一個(gè)H 橋結(jié)構(gòu)放大電路和Class AB 型輸出放大結(jié)構(gòu)共同組成,二者結(jié)合可以提供更優(yōu)的增益、速度和驅(qū)動(dòng)能力,但是難點(diǎn)在于頻率補(bǔ)償和Class AB 結(jié)構(gòu)靜態(tài)電流的控制,詳細(xì)原理將在1.4 小節(jié)論述。由于整個(gè)信號(hào)通路是差分形式,共模反饋電路必不可少,它設(shè)定了每一級(jí)電路的輸出直流共模電平,保證其工作在放大區(qū)。共模反饋原理將在1.5 節(jié)論述。

圖1 差分輸出放大器結(jié)構(gòu)框圖Fig.1 Building blocks of differential output amplifier

另外,為各個(gè)支路提供電流的偏置電路是一個(gè)典型的PTAT 電流源[1-2],PTAT 電流源結(jié)構(gòu)比較簡(jiǎn)單,在多個(gè)文獻(xiàn)中都有分析,其詳細(xì)原理此處不再贅述。

圖1 中的RF和RG是設(shè)置閉環(huán)增益的外圍電阻,用于設(shè)定放大倍數(shù),其值為:

1.2 H 橋電路

H 橋電路由于其結(jié)構(gòu)酷似英文字母“H” 而得名,如圖2 所示。

圖2 H 橋式結(jié)構(gòu)Fig.2 “H” bridge structure

該電路對(duì)稱性極強(qiáng),Q1~Q8和R0構(gòu)成了H 橋結(jié)構(gòu)的核心,Q1~Q4是射極跟隨器,對(duì)輸入信號(hào)進(jìn)行緩沖,同時(shí)設(shè)定了Q5~Q8的靜態(tài)電流。Q5~Q8對(duì)輸入信號(hào)進(jìn)一步緩沖。假設(shè)NPN 管和PNP 管的Vbe相等,最終輸入信號(hào)施加在電阻R0上,產(chǎn)生如式(2)所示的電流:

跨導(dǎo)為:

小信號(hào)增益為:

電流I會(huì)隨著差分輸入信號(hào)的增加而增大,輸入信號(hào)的快速變化會(huì)迅速轉(zhuǎn)化為對(duì)應(yīng)電流,寄生節(jié)點(diǎn)可以較大的電流進(jìn)行充放電,這意味H 橋結(jié)構(gòu)的速度非常快,即壓擺率很大。與傳統(tǒng)的差分對(duì)只能以固定電流對(duì)容性節(jié)點(diǎn)充放電相比,這是H 橋結(jié)構(gòu)的一大優(yōu)勢(shì)。

較大的R0會(huì)減小電流,降低跨導(dǎo),進(jìn)而降低電路速度和增益,但是電路穩(wěn)定性會(huì)提高。所以需要結(jié)合后級(jí)電路,選擇合適的R0,以達(dá)到速度和穩(wěn)定性的折中。

1.3 求和電路

求和電路如圖3 所示。H 橋結(jié)構(gòu)的輸出電壓經(jīng)Q9~Q10緩沖后,由Q13~Q16進(jìn)行放大。Q13~Q16是帶射極反饋電阻/電容的共射極放大電路。

圖3 求和電路Fig.3 Summing circuit

求和電路的小信號(hào)跨導(dǎo)為:

式中:gm13~16是Q13~Q16的跨導(dǎo);C是與Q13~Q16發(fā)射極電阻并聯(lián)的電容;R11~R14的存在主要是為了便于接收共模反饋信號(hào)以控制VOP和VON的直流電平。但是發(fā)射極電阻會(huì)減小跨導(dǎo),降低增益。隨著頻率逐漸升高,發(fā)射極電阻的并聯(lián)電容C能夠改善跨導(dǎo)的減小,跨導(dǎo)由低頻下的恢復(fù)為高頻下的一定程度上改善了增益的降低。

另外,公式(5)引入了一個(gè)零極點(diǎn),且零點(diǎn)遠(yuǎn)低于極點(diǎn)。選擇合適的RC,零點(diǎn)可以抵消VOP和VON處的寄生極點(diǎn)最終求和電路只有一個(gè)高頻極點(diǎn)帶寬得到明顯拓展。

1.4 輸出結(jié)構(gòu)

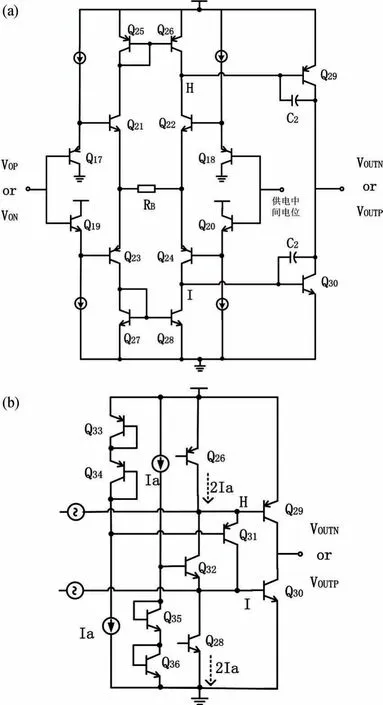

輸出級(jí)如圖4(a)所示。輸出級(jí)是一個(gè)兩級(jí)放大器,Q17~Q24和RB再次組成H 橋結(jié)構(gòu),負(fù)載從輸入級(jí)的電阻變成了此處的電流鏡負(fù)載。Q29和Q30分別是PNP 和NPN 共射極放大器,二者的集電極連接在一起,構(gòu)成輸出級(jí)的一端。該結(jié)構(gòu)在軌到軌輸出放大器結(jié)構(gòu)中十分常見,難點(diǎn)在于輸出級(jí)靜態(tài)電流的控制。

圖4(b)是一種用于控制Class AB 輸出級(jí)的電路。所有的P 管和N 管分別構(gòu)成一個(gè)環(huán)路,假設(shè)Q31和Q32流過的電流相等且均為Ia,可得如下等式:

圖4 (a)輸出級(jí);(b)Class AB 靜態(tài)電流控制Fig.4 (a)Output stage;(b) The control of quiescent current of Class AB circuit

從式(8)和(9),可以看出,輸出晶體管Q29和Q30靜態(tài)電流可以通過電流源Ia和晶體管面積得到精確控制。另外,Q17~Q24組成的H 橋結(jié)構(gòu)可以為Q29和Q30提供較大的且快速變化的驅(qū)動(dòng)電流,經(jīng)由Q29和Q30的AB 類工作進(jìn)一步放大,可以實(shí)現(xiàn)大電流驅(qū)動(dòng)能力和軌到軌輸出擺幅。

1.5 共模反饋電路

共模反饋電路用于設(shè)定差分放大級(jí)的直流共模輸出電平,保證放大器可以工作在有源放大狀態(tài)。在設(shè)計(jì)共模反饋環(huán)路的時(shí)候,需要考慮以下幾個(gè)方面:(1)共模反饋環(huán)路的直流增益要盡可能大;(2)共模反饋環(huán)路的帶寬要盡可能大,最好能和差分通路接近;(3)共模反饋環(huán)路的相位裕度也必須達(dá)到一定要求,比如45°以上的相位裕度。

圖5 所示的共模反饋電路與輸入級(jí)非常類似,負(fù)載電阻R17~R24分別與輸入級(jí)和求和電路連接(A~H 節(jié)點(diǎn)),后續(xù)的信號(hào)通路與差分信號(hào)一致。輸出共模信號(hào)采用簡(jiǎn)單的大電阻采樣。對(duì)于A~D 節(jié)點(diǎn),整個(gè)共模反饋環(huán)路由求和電路、輸出級(jí)與共模反饋電路構(gòu)成,對(duì)于E~H 節(jié)點(diǎn),整個(gè)共模反饋環(huán)路由輸出級(jí)與共模反饋電路構(gòu)成。差分和共模信號(hào)路徑十分接近,增益接近,調(diào)整補(bǔ)償電容和電阻Rc以調(diào)整共模反饋環(huán)路的穩(wěn)定性,可以實(shí)現(xiàn)高速、寬帶、穩(wěn)定的共模反饋環(huán)路。

圖5 共模反饋電路Fig.5 Common mode feedback circuit

1.6 頻率補(bǔ)償

輸入級(jí)、求和電路和輸出級(jí)(兩級(jí)放大)實(shí)際上構(gòu)成了四級(jí)放大結(jié)構(gòu)。輸入級(jí)增益較小(8 dB 左右),寄生極點(diǎn)較高,遠(yuǎn)遠(yuǎn)超過整個(gè)放大器-3 dB 帶寬以外,可以忽略輸入級(jí)對(duì)頻率特性的影響。所以需要對(duì)一個(gè)三級(jí)放大結(jié)構(gòu)進(jìn)行頻率補(bǔ)償,否則無(wú)法保證閉環(huán)工作穩(wěn)定。三級(jí)放大器的頻率補(bǔ)償常用的是嵌套式密勒補(bǔ)償(Nested Miller Compensation)[14-15],該補(bǔ)償方式在多個(gè)教科書和文獻(xiàn)中已經(jīng)詳細(xì)論述,此處只給出結(jié)論。

假設(shè)補(bǔ)償后的傳輸函數(shù)是三階Butterworth 頻率響應(yīng),則單位增益帶寬近似為:

式中:wo是單位增益帶寬;Gm1是輸入級(jí)的跨導(dǎo);C1是跨接整個(gè)輸出級(jí)的頻率補(bǔ)償電容。

2 仿真、版圖與測(cè)試

2.1 仿真

本文提出的放大器基于自主高速互補(bǔ)雙極工藝設(shè)計(jì),利用Spectre 仿真器對(duì)電路進(jìn)行了仿真驗(yàn)證。如圖1 所示,采用外部電阻RF和RG是設(shè)置閉環(huán)增益的。

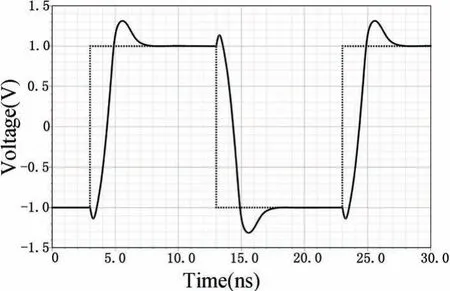

圖6 給出了增益的幅頻特性的仿真曲線,圖7 給出了大信號(hào)瞬態(tài)響應(yīng)的仿真曲線。

圖6 閉環(huán)頻率響應(yīng)Fig.6 Closed loop frequency response

圖7 大信號(hào)瞬態(tài)響應(yīng)Fig.7 Large signal transient response

如圖6 所示,當(dāng)RF=RG=200 Ω,即閉環(huán)增益為1時(shí),仿真閉環(huán)-3 dB 帶寬約520 MHz,200 MHz 處有增益尖峰,但是幅度僅為0.1 dB 左右。

如圖7 所示,當(dāng)RF=RG=200 Ω,即閉環(huán)增益為1時(shí),虛線代表輸入電壓,實(shí)線代表輸出電壓,輸入信號(hào)幅度±1 V,脈沖寬度10 ns,可以看出壓擺率SR+≈SR-=1500 V/μs。輸出波形約有20%以內(nèi)的過沖,增加C1可以減小過沖,但是也會(huì)使得帶寬減小。

2.2 版圖

圖8 是放大器的整體版圖。

圖8 放大器的整體版圖Fig.8 The overall layout of amplifier

2.3 測(cè)試結(jié)果

對(duì)本文提出的放大器進(jìn)行流片,實(shí)測(cè)結(jié)果如表1所示。表 中Icc、IIB、IIO、VOS、Av、BW、SR、ISC、SWING 分別表示電源電流、輸入偏置電流、輸入失調(diào)電流、輸入失調(diào)電壓、增益、帶寬、壓擺率、輸出短路電流和輸出擺幅。

表1 測(cè)試結(jié)果(Vs=5 V,25 ℃)Tab.1 Test results(Vs=5 V,25 ℃)

從測(cè)試結(jié)果可以看出,AD8138 的電源電流和本文提出的電路比較接近,但是-3 dB 帶寬和壓擺率小于本文提出的電路,單端輸出幅度只有1~3.9 V。AD8137 采用了某種形式的大擺幅輸出結(jié)構(gòu),輸出幅度有所改善,達(dá)到0.45~4.55 V,但是依然比本文提出的電路低0.5 V 左右,-3 dB 帶寬和壓擺率分別只有75 MHz 和450 V/μs。與AD8138 和AD8137 相比[16-17],本文提出的電路實(shí)現(xiàn)了0.5 mV 的輸入失調(diào)電壓,-3 dB 帶寬達(dá)到400 MHz,壓擺率達(dá)到1300 V/μs,單端輸出擺幅達(dá)到0.2~4.8 V,速度和輸出幅度性能非常優(yōu)越。

3 結(jié)論

本文設(shè)計(jì)了一款基于高速互補(bǔ)雙極工藝的高速寬帶軌到軌輸出差分放大器,有效克服了低壓下傳統(tǒng)差分放大器輸出擺幅、速度和驅(qū)動(dòng)能力嚴(yán)重降低的問題。利用Spectre 仿真器對(duì)電路進(jìn)行了仿真驗(yàn)證,并進(jìn)行了流片。測(cè)試結(jié)果表明,在單5 V 工作的情況下,提出的差分輸出放大器低頻開環(huán)增益達(dá)到100 dB,輸入失調(diào)電壓為0.5 mV,單端輸出幅度為0.2~4.8 V,-3 dB 帶寬和壓擺率分別達(dá)到400 MHz 和1300 V/μs。通過電路結(jié)構(gòu)設(shè)計(jì)和分析,理論上說明了軌到軌全差分輸出的可行性,對(duì)高速ADC 驅(qū)動(dòng)、線纜驅(qū)動(dòng)等需要高速差分信號(hào)的領(lǐng)域,軌到軌的寬輸出擺幅可以大大改善系統(tǒng)的信噪比等關(guān)鍵性能指標(biāo),對(duì)于推動(dòng)寬帶大擺幅高速差分放大器的進(jìn)一步研究及應(yīng)用具有十分重要的意義。