基于FPGA的DDS信號(hào)發(fā)生器設(shè)計(jì)

董殿國(guó),侯文

(中北大學(xué) 信息與通信工程學(xué)院,山西太原,030051)

0 引言

隨著現(xiàn)代電子技術(shù)的飛速發(fā)展,直接數(shù)字頻率合成DDS技術(shù)逐漸被廣泛使用,從其技術(shù)理論上看,具有靈活性高、變頻速度快、變頻簡(jiǎn)單等優(yōu)點(diǎn)。從實(shí)際效果來(lái)看,變頻時(shí)分辨率高,相位噪聲低,電路集成度高、頻率穩(wěn)定等優(yōu)點(diǎn)。該技術(shù)已經(jīng)逐漸被應(yīng)用到現(xiàn)代雷達(dá)、導(dǎo)航、遙感、現(xiàn)代儀器儀表等關(guān)鍵領(lǐng)域。

使用DDS技術(shù)產(chǎn)生任意頻率波形的方案主要有三種。第一種是直接使用高性能專(zhuān)用DDS集成電路芯片,比如AD9833,此種方案的優(yōu)點(diǎn)是產(chǎn)生的波形頻率準(zhǔn)確,變頻時(shí)分辨率高,直接使用通訊協(xié)議控制輸入。缺點(diǎn)是,可以產(chǎn)生的波形類(lèi)型受限,只有特定的幾種,且內(nèi)部配置靈活性很低。第二種是使用單片機(jī)實(shí)現(xiàn)DDS技術(shù),此種方案在低頻時(shí)配置較為簡(jiǎn)單,易于實(shí)現(xiàn),在中高頻時(shí)配置容易受到其他模塊影響,嚴(yán)重影響波形頻率精度。第三種是基于現(xiàn)場(chǎng)可編程門(mén)陣列FPGA來(lái)實(shí)現(xiàn),此種方案靈活性較高,配置簡(jiǎn)單,易于實(shí)現(xiàn),且變頻范圍廣,分辨率高,唯一缺點(diǎn)就是,浪費(fèi)FPGA內(nèi)部未使用資源,造價(jià)高昂[1]。

1 DDS基本原理和核心設(shè)計(jì)

■1.1 DDS基本原理

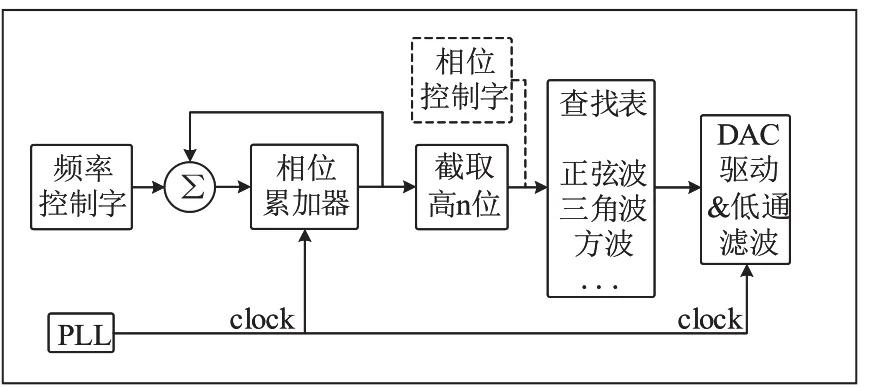

DDS技術(shù)原理框圖如圖1所示,主要有以下關(guān)鍵幾部分組成,N位相位累加器、頻率控制字、相位控制字、ROM查找表和時(shí)鐘源等。

圖1 DDS結(jié)構(gòu)原理圖

相位累加器在高頻時(shí)鐘下以頻率控制字的字長(zhǎng)K做累加。累加后的相位累加器值通過(guò)高位截取后變?yōu)橄辔豢刂谱郑辔豢刂谱旨礊椴檎冶淼牡刂贰T诓檎冶碇屑纯烧业綄?duì)應(yīng)波形的多位數(shù)字輸出值。這就是DDS基本工作原理。若要輸出波形,將輸出的多位二進(jìn)制數(shù)字輸出通過(guò)D/A轉(zhuǎn)換輸出對(duì)應(yīng)的模擬電壓信號(hào),再通過(guò)一個(gè)低通濾波器輸出平滑的曲線[2]。

■ 1.2 DDS核心設(shè)計(jì)

若要實(shí)現(xiàn)更高的頻率分辨率和精度,共有兩種方式,第一,將查找表中的波形數(shù)據(jù)取的分辨率更高,取樣點(diǎn)的數(shù)據(jù)更多,這就意味著增加等倍的存儲(chǔ)空間;第二,增加相位累加器的位數(shù)。事實(shí)上,典型的DDS系統(tǒng)會(huì)使用非常“長(zhǎng)”位數(shù)的相位累加器,比如28位、32位甚至36位,來(lái)實(shí)現(xiàn)高精度和高分辨率的信號(hào)輸出頻率。在FPGA內(nèi)部所使用的硬件資源來(lái)看,只是多使用幾個(gè)寄存器,但是對(duì)其內(nèi)部資源來(lái)講,影響微乎其微。但是從其實(shí)際意義上看,可以大大提高其頻率的精度和分辨率[3]。

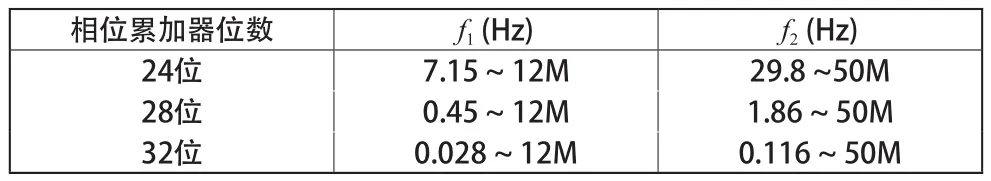

表1中,f1為外部時(shí)鐘輸入經(jīng)過(guò)倍頻后的輸出頻率為120MHz,f2為外部時(shí)鐘輸入經(jīng)過(guò)PLL倍頻后的輸出頻率為500MHz,波形可調(diào)的最低頻率即為頻率的分辨率。

表1 不同情況下頻率可調(diào)節(jié)范圍和分辨率

如表1所示,相位累加器位數(shù)更高,其對(duì)應(yīng)的頻率分辨率越高,系統(tǒng)主頻經(jīng)過(guò)倍頻后的頻率越高,輸出波形的上限頻率越高。

需要注意的是,查找表地址為8位,比如當(dāng)f1=120MHz時(shí)候,在不同累加器位數(shù)下,其可調(diào)的波形分辨率不同,但是120M/28=468 75kHz是一個(gè)臨界值,當(dāng)輸出頻率小于等于468 75kHz時(shí)候,輸出的波形特征則可以完全還原查找表中的波形數(shù)據(jù)點(diǎn);當(dāng)輸出的波形頻率大于468 75kHz時(shí)候,頻率越高,輸出的波形無(wú)法還原查找表中的波形數(shù)據(jù)點(diǎn),還原度越來(lái)越低,波形特征越來(lái)越不明顯。同樣的對(duì)于f2=500MHz時(shí)候,500M/28≈1 95MHz也是可以保持原查找表中波形數(shù)據(jù)點(diǎn)的最大頻率[4]。

2 系統(tǒng)硬件設(shè)計(jì)

■2.1 硬件整體方案

函數(shù)信號(hào)發(fā)生器的硬件系統(tǒng)主要包括MCU控制電路,F(xiàn)PGA構(gòu)成的DDS發(fā)生器、DAC轉(zhuǎn)換和低通濾波電路,及一些用于輸入輸出的器件等。

按鍵輸入和LCD輸出顯示主要由MCU負(fù)責(zé)控制,MCU然后將輸入的信號(hào)運(yùn)算處理后發(fā)送給FPGA,F(xiàn)PGA根據(jù)輸入的各種參數(shù)在ROM表中尋址,同時(shí)輸出對(duì)應(yīng)控制的波形、頻率和幅度的數(shù)字信號(hào),最后經(jīng)過(guò)DA轉(zhuǎn)換為對(duì)應(yīng)的模擬電壓信號(hào),在經(jīng)過(guò)一個(gè)低通濾波器使得模擬電壓信號(hào)變得平滑。

■ 2.2 硬件模塊電路

系統(tǒng)的硬件電路主要分為兩個(gè)部分,一是系統(tǒng)主控電路,二是DDS信號(hào)發(fā)生器電路。

系統(tǒng)主控電路包括以STM32F103C8T6為主控的最小系統(tǒng)板、四路用戶按鍵輸入、OLED顯示屏輸出(SPI)、UART通信連接上位機(jī)、硬件SPI連接FPGA負(fù)責(zé)信號(hào)數(shù)據(jù)傳輸,如圖2所示。

圖2 系統(tǒng)主控電路

DDS信號(hào)發(fā)生器電路,其中的FPGA模塊的核心芯片為L(zhǎng)attice LCMXO2-4000HC-4MG132,其模塊上內(nèi)置8路輸出LED指示燈、4路按鍵輸入、4路撥碼輸入和兩位數(shù)碼管輸出燈資源。DAC芯片采用3PEAK的高速10位DAC芯片3PD5651E,采樣速率125MSPS,CMOS數(shù)模轉(zhuǎn)換器。本系統(tǒng)中采用12MHz的外部晶振經(jīng)過(guò)PLL倍頻為120MHz小于DAC芯片的最大采樣速率,符合使用要求。

3 系統(tǒng)軟件設(shè)計(jì)

■3.1 MCU程序流程設(shè)計(jì)

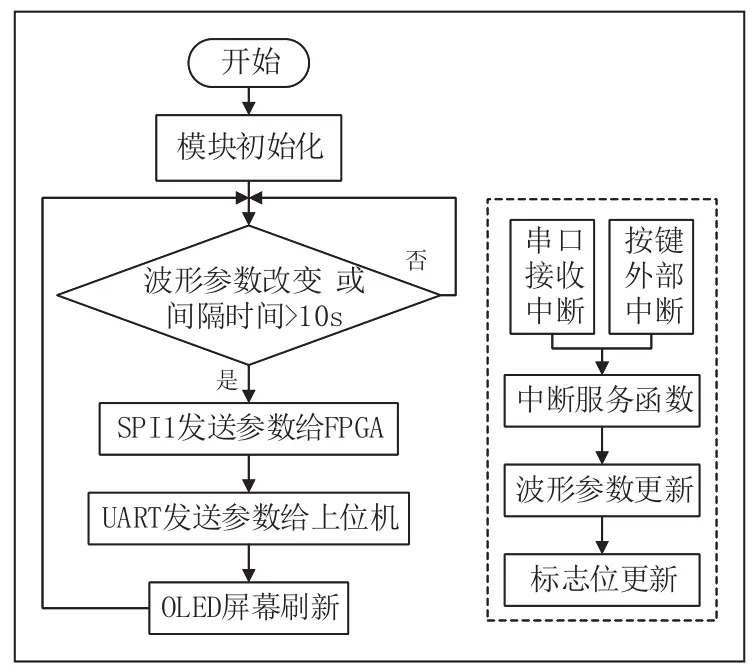

MCU主控制器主要負(fù)責(zé)系統(tǒng)中各個(gè)子任務(wù)的任務(wù)調(diào)度,系統(tǒng)的程序流程如圖3所示,系統(tǒng)上電后先對(duì)各個(gè)模塊進(jìn)行初始化,包括串口初始化、OLED顯示屏對(duì)應(yīng)SPI1外設(shè)初始化、FPGA的SPI2外設(shè)初始化、按鍵和LED輸入輸出初始化等。

圖3 MCU程序設(shè)計(jì)流程

程序中共有兩個(gè)自定義的中斷源,串口接收中斷和按鍵的外部中斷,按鍵的外部中斷用于改變波形的相關(guān)參數(shù)對(duì)應(yīng)的各個(gè)全局變量;而串口接收中斷用于接收來(lái)自上位機(jī)中的信息,一類(lèi)是波形參數(shù)對(duì)應(yīng)的全局變量同步和參數(shù)顯示,另一類(lèi)是接收自定義波形數(shù)據(jù)表,并且通過(guò)SPI硬件通信接口實(shí)時(shí)存入FPGA的ROM模塊中。此處有一個(gè)關(guān)鍵問(wèn)題,上位機(jī)中波形參數(shù)的改變與顯示,硬件上波形參數(shù)的改變和顯示器的顯示、程序內(nèi)部波形參數(shù)對(duì)應(yīng)的全局變量,以及波形的實(shí)際輸出參數(shù),在程序的運(yùn)行過(guò)程中,需要時(shí)刻保證這四個(gè)模塊中波形參數(shù)數(shù)據(jù)的同步。即先判定數(shù)據(jù)的輸入輸出屬性,在每一個(gè)輸入模塊中添加波形參數(shù)更新標(biāo)志位,實(shí)時(shí)更新程序中的全局變量,然后再根據(jù)參數(shù)對(duì)應(yīng)的全局變量,隨即更新參數(shù)更新來(lái)源模塊之外的參數(shù)顯示模塊即可以實(shí)現(xiàn)四個(gè)模塊的實(shí)時(shí)同步。

在MCU主程序的主函數(shù)中,主任務(wù)即為循環(huán)判斷波形參數(shù)的全局變量是否改變,若改變則對(duì)串口傳輸上位機(jī)顯示、SPI2對(duì)應(yīng)的OLED顯示屏顯示、SPI1對(duì)應(yīng)的FPGA三個(gè)模塊做刷新處理;若未改變,則在間隔時(shí)間大于10s時(shí)候做刷新處理來(lái)降低容錯(cuò)率。

■3.2 FPGA模塊設(shè)計(jì)

在整個(gè)系統(tǒng)中,F(xiàn)PGA模塊主要負(fù)責(zé)DDS核心數(shù)字變頻技術(shù)的實(shí)現(xiàn)。主要包括,PLL模塊、SPI通訊接收模塊、數(shù)據(jù)轉(zhuǎn)換模塊、DDS累加器模塊、ROM查找表模塊、幅度變換模塊等。總共例化了四個(gè)波形數(shù)據(jù)的ROM,其mif文件通過(guò)MATLAB軟件編寫(xiě),然后調(diào)用IP讀取。但是由于FPGA內(nèi)部ROM資源限制,只能采用相位截?cái)喾椒ㄈ「遪為作為查詢地址使用。

FPGA的DDS系統(tǒng)模塊設(shè)計(jì),主要由SPI通訊接收模塊負(fù)責(zé)接收MCU傳輸?shù)牟ㄐ螀?shù),包括波形類(lèi)型、波形頻率和波形幅度等。然后由數(shù)據(jù)轉(zhuǎn)換模塊負(fù)責(zé)將對(duì)應(yīng)的波形類(lèi)型,頻率、相位、幅度轉(zhuǎn)換為相應(yīng)的頻率控制字和相位控制字,最后將控制字直接輸入DDS累加器模塊中,相位累加器在120MHz的時(shí)鐘信號(hào)下產(chǎn)生采樣地址,通過(guò)波形類(lèi)型選擇選擇對(duì)應(yīng)的ROM查找表模塊。在ROM模塊中存儲(chǔ)有正弦波、三角波、方波等常見(jiàn)波形的10位數(shù)字信號(hào)量,根據(jù)波形類(lèi)型查找對(duì)應(yīng)的10位數(shù)字信號(hào)值并輸出到幅度變換模塊。幅度變換模塊同時(shí)根據(jù)輸入的幅度設(shè)定值來(lái)輸出對(duì)應(yīng)的10為數(shù)字信號(hào)量。

FPGA不同于MCU的串行運(yùn)行機(jī)制,F(xiàn)PGA內(nèi)部是通過(guò)組合邏輯和時(shí)序邏輯所構(gòu)成的并行運(yùn)行機(jī)制的電路模塊。所以在很多需要串行運(yùn)行的模塊中,就需要添加各種標(biāo)志位或者狀態(tài)機(jī)來(lái)實(shí)現(xiàn)。其中,SPI通信接收模塊、數(shù)據(jù)轉(zhuǎn)換模塊、幅度變換模塊都有關(guān)鍵的完成標(biāo)志位,方便開(kāi)啟下一級(jí)模塊使用。

■3.3 上位機(jī)軟件設(shè)計(jì)

上位機(jī)軟件使用NI公司的Labview軟件開(kāi)發(fā),Labview以其使用簡(jiǎn)單、圖形化的編程方式、功能模塊封裝度高、對(duì)各類(lèi)硬件采集卡和常見(jiàn)的標(biāo)準(zhǔn)接口適配性高等優(yōu)點(diǎn)而收到廣大工程師和相關(guān)從業(yè)者使用。通訊方式使用串行通信UART串口連接,波特率115200,停止位1位,無(wú)奇偶校驗(yàn)位。為了提高調(diào)節(jié)各類(lèi)參數(shù)和數(shù)據(jù)同步的響應(yīng)時(shí)間,通訊協(xié)議使用自定義方式,第一位功能碼,代表此時(shí)調(diào)節(jié)的參數(shù)類(lèi)型,第二位到第九位為對(duì)應(yīng)的參數(shù)值,使用ASCII字符傳輸,第十位為CRC校驗(yàn)位,校驗(yàn)數(shù)據(jù)傳輸。最后一位為結(jié)束字符,用于判斷串口傳輸是否完成。

上位機(jī)軟件主要分為兩個(gè)模塊構(gòu)成,一是串口的發(fā)送和接收模塊,主要在系統(tǒng)的串口控件處發(fā)送和接收相關(guān)數(shù)據(jù);二是數(shù)據(jù)處理模塊,主要將對(duì)應(yīng)的信號(hào)參數(shù)數(shù)據(jù)實(shí)時(shí)轉(zhuǎn)換到對(duì)應(yīng)的控件顯示上,或者將對(duì)應(yīng)的控件顯示數(shù)據(jù)編碼準(zhǔn)備發(fā)送。

由于在實(shí)際測(cè)試實(shí)驗(yàn)中所需的實(shí)驗(yàn)波形多種多樣,且FPGA中數(shù)據(jù)存儲(chǔ)資源有限,所以就需要在上位機(jī)軟件中集成可以實(shí)時(shí)傳輸自定義波形數(shù)據(jù)的功能,這就是上位機(jī)軟件中另一個(gè)主要功能,由于Labview軟件可以直接與MATLAB腳本做混合程序設(shè)計(jì),所以可以先通過(guò)在MATLAB中生成所需要波形的mif數(shù)據(jù)文件,直接在Labview上位機(jī)中導(dǎo)入生成所需的波形數(shù)據(jù),完成自定義波形數(shù)據(jù)導(dǎo)入功能。

4 結(jié)果分析

■ 4.1 基本功能實(shí)現(xiàn)

信號(hào)發(fā)生器的幅度和頻率等相關(guān)參數(shù)可以實(shí)現(xiàn)板載的手動(dòng)調(diào)節(jié),同樣也可以連接計(jì)算機(jī)在上位機(jī)的視圖中調(diào)節(jié)使用。需要注意的是,上位機(jī)調(diào)節(jié)和板載調(diào)節(jié)并不是簡(jiǎn)單孤立的,雙方在不同參數(shù)的調(diào)節(jié)過(guò)程中是同步的。

■ 4.2 性能分析

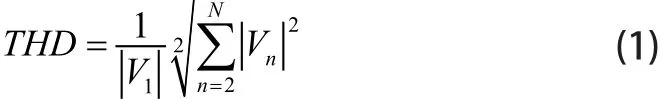

以信號(hào)發(fā)生器輸出正弦波為例,輸出不同頻率的正弦波來(lái)分析其諧波失真(THD)。在此次測(cè)量實(shí)驗(yàn)中,使用泰克MDO32頻譜分析儀(模擬通道帶寬1GHz、采樣率2 5GS/s)來(lái)測(cè)量信號(hào)發(fā)生器輸出正弦波時(shí),基波之外的高次諧波分量,來(lái)計(jì)算其諧波失真[5]:

在實(shí)驗(yàn)測(cè)量中,無(wú)法計(jì)算所有的高次諧波分量,只計(jì)算了8次諧波分量,所以在(1)式中N=8。實(shí)驗(yàn)測(cè)試結(jié)果如圖4所示,橫坐標(biāo)為頻率測(cè)試范圍,從1Hz到10MHz。正弦波的THD值在局部上有所波動(dòng),但是在整體上趨于平穩(wěn)。即該信號(hào)發(fā)生器的總諧波失真≤-10dB。

線性度是描述三角波的一個(gè)重要參數(shù)。在參數(shù)性能測(cè)試實(shí)驗(yàn)中,本文使用NI公司的PXI-6115多功能IO采集卡(最大采樣率10MS/s)采集三角波在不同頻率下的波形數(shù)據(jù)樣點(diǎn),并計(jì)算三角波在不同頻率下的線性度。

在三角波的線性度性能測(cè)試實(shí)驗(yàn)中,標(biāo)定了三角波的對(duì)稱(chēng)性為50%,幅值為3Vpp,頻率從1Hz~1MHz范圍,采集其樣點(diǎn)數(shù)據(jù),并做數(shù)據(jù)分析,計(jì)算其線性度。從增長(zhǎng)趨勢(shì)上來(lái)看,信號(hào)的頻率越高,其線性度越差,但是從頻率的整體范圍上來(lái)看,其線性度一直保持在1%以下。符合系統(tǒng)預(yù)期的三角波線性度要求。

■ 4.3 性能總結(jié)

信號(hào)發(fā)生器的最高頻率以正弦波輸出的最高頻率為12MHz;DAC芯片的采樣率為125Msps,但是FPGA的內(nèi)部主頻經(jīng)過(guò)PLL倍頻后為120MHz,所以該信號(hào)發(fā)生器的采樣率為120MSa/s;FPGA的數(shù)字信號(hào)量輸出為10bits,且DAC芯片也為10bits,則信號(hào)發(fā)生器的垂直分辨率為10bits,系統(tǒng)內(nèi)置常見(jiàn)的波形,正弦波、三角波、方波等,但是可以根據(jù)需要,重新生成任意波形數(shù)據(jù)樣點(diǎn)保存后并輸出。

5 結(jié)束語(yǔ)

本文基于DDS技術(shù),使用MCU和FPGA聯(lián)合設(shè)計(jì)的信號(hào)發(fā)生器,經(jīng)過(guò)實(shí)驗(yàn)各種性能測(cè)試,結(jié)果表明,該信號(hào)發(fā)生器精度高,穩(wěn)定可靠,噪聲小,可以在各種實(shí)驗(yàn)室和工業(yè)場(chǎng)合使用。但是,也存在波形幅度較小和頻率較高時(shí),波形失真明顯,需要進(jìn)一步改進(jìn)。