基于PCIe的高精度低雜散信號源設(shè)計

段雄風,張 鵬

(1.中北大學(xué)儀器與電子學(xué)院,山西 太原 030051;2.中北大學(xué)電子測試技術(shù)國家重點實驗室,山西 太原 030051)

0 引言

信號源能產(chǎn)生多種可調(diào)的激勵信號,在電子電路、雷達遙測和軍工航天等領(lǐng)域有著廣泛的應(yīng)用[1]。對壓力信號采集測試儀器而言,一方面信號源為自測試設(shè)備模擬真實環(huán)境,產(chǎn)生測試波形信號,用于測試設(shè)備的正常功能指標;另一方面高精度的信號源激勵被測系統(tǒng)用于校準測試系統(tǒng)[2]。傳統(tǒng)的信號源輸出類型單一、精度低、誤差較大、電路設(shè)計冗雜。目前,大多采用直接數(shù)字式頻率合成器(direct digital synthesis,DDS)技術(shù)設(shè)計信號源系統(tǒng)。實現(xiàn)DDS信號生成的方案有2種。第一種是采用專用DDS芯片。這種方案控制簡單、穩(wěn)定性高,但是波形數(shù)據(jù)在內(nèi)部存儲器中固化,無法充分滿足用戶的各種需求。第二種是在現(xiàn)場可編程門陣列(field programmable gate array,FPGA)中根據(jù)需求實時產(chǎn)生任意可調(diào)波形。這種方案具有很強的靈活性[3]。

本文采用第二種方案,通過在FPGA中編程實現(xiàn)多功能高精度信號的發(fā)生(其中包括幾種常用的基本信號與調(diào)制信號),并可根據(jù)用戶需求通過上位機實時發(fā)送波形數(shù)據(jù)到FPGA,以產(chǎn)生任意波形的信號。在FPGA的可編程邏輯基礎(chǔ)上,該方案靈活使用DDS與有限長單位沖激響應(yīng)(finite impulse response,F(xiàn)IR)濾波器的相關(guān)知識產(chǎn)權(quán)(intellectual property,IP)核,針對信號雜散的產(chǎn)生原因進行分析處理,使輸出信號滿足高精度、低雜散的需求。另外,該方案通過高速串行計算機擴展總線(peripheral component interconnect express,PCIe)標準接口傳輸指令和波形數(shù)據(jù),實現(xiàn)信號源的標準化和實時性,提供1種頻率分辨率高、易于集成和小型化的多功能精密信號源產(chǎn)品。該產(chǎn)品方便集成在信號采集系統(tǒng),用以輸出穩(wěn)定信號,并用于儀器自測試。

1 系統(tǒng)總體設(shè)計方案

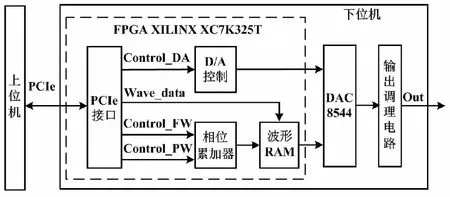

基于FPGA實現(xiàn)的信號源系統(tǒng)含上位機、主控制器FPGA、信號數(shù)模(digital to analog,D/A)轉(zhuǎn)換和信號輸出調(diào)理部分。上位機對要輸出的波形數(shù)據(jù)進行量化,將量化后的數(shù)據(jù)和控制指令分別通過PCIe存入FPGA內(nèi)的波形存儲器和命令控制器,并采用控制頻率控制字與相位控制字對查找表尋址提取對應(yīng)數(shù)據(jù),再由數(shù)字模擬轉(zhuǎn)換器(digital to analog converter,DAC)和輸出調(diào)理電路轉(zhuǎn)為要求電壓范圍內(nèi)的模擬信號[4]。PCIe的物理接口采用金手指插入主機卡槽。邏輯功能通過Xilinx公司提供的XDMA IP核實現(xiàn),可配置AXI4-Lite 選項來訪問用戶邏輯側(cè)寄存器。信號源系統(tǒng)整體如圖1所示。

圖1 信號源系統(tǒng)整體框圖

當信號源工作時,設(shè)定的頻率控制字FW決定了輸出信號的頻率,而相位控制字PW決定了信號的初始相位。信號的最小頻率分辨率受相位累加器位數(shù)的影響,滿足式(1):

(1)

當系統(tǒng)基準時鐘不變、累加器的位數(shù)一定時,DDS輸出信號的最小頻率分辨率不會改變[5]。通常,為了獲得較好的頻率分辨率,會將相位N設(shè)置得比較大。

2 信號源硬件電路設(shè)計

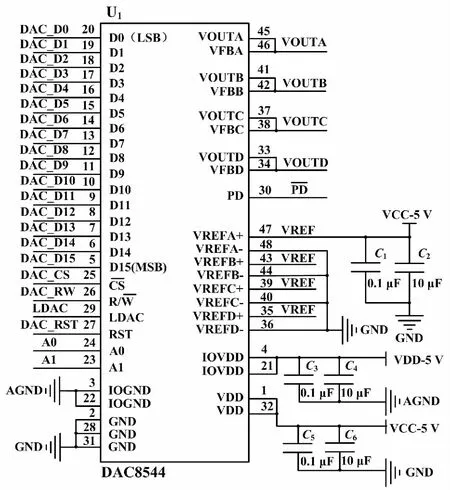

2.1 四通道D/A轉(zhuǎn)換電路設(shè)計

在FPGA的信號發(fā)生邏輯設(shè)計中,波形隨機存取存儲器(ramdom access memory,RAM)存儲的是連續(xù)數(shù)字量,需要經(jīng)過D/A轉(zhuǎn)換才能輸出對應(yīng)的模擬信號[6]。為滿足設(shè)計需求,本文選擇TI公司的低功耗4通道DAC8544芯片搭建D/A轉(zhuǎn)換電路,以實現(xiàn)在初始化和復(fù)位時同步操作內(nèi)部的轉(zhuǎn)換器。該芯片采用并行輸出接口,轉(zhuǎn)換精度高達16位,內(nèi)部含有精密輸出放大器實現(xiàn)電壓輸出,并具有超低的串擾;采用雙電源供電,同時具有模擬和數(shù)字接地引腳,可以更好地控制返回電流,對輸出誤差影響較小。本文設(shè)計的D/A 轉(zhuǎn)換電路如圖2所示。

圖2 D/A轉(zhuǎn)換電路

DAC8544芯片通過外部參考電壓來設(shè)置DAC的輸出范圍。其計算式為:

(2)

式中:UOUT為轉(zhuǎn)換器輸出電壓,V;D為轉(zhuǎn)換器輸入數(shù)字量。

根據(jù)所設(shè)計的UREF+為+5 V、UREF-接地為0 V,可得DAC輸出范圍為0~5 V。輸入數(shù)據(jù)D經(jīng)并行數(shù)據(jù)線DAC_D0~DAC_D15進入轉(zhuǎn)換器,輸出4路電壓信號VOUTA~VOUTD。

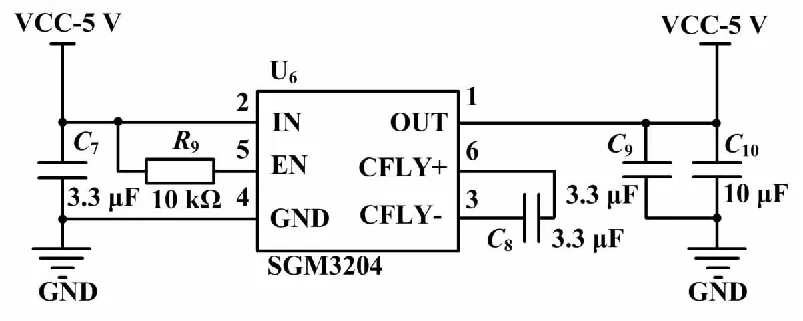

DAC8544芯片的雙極性電源中,VCC-5 V模擬電源由PCIe插槽提供,同時經(jīng)過SGM3204電壓逆變器后,有效提供VCC-5 V負極性電源。電源轉(zhuǎn)換電路如圖3所示。

圖3 電源轉(zhuǎn)換電路

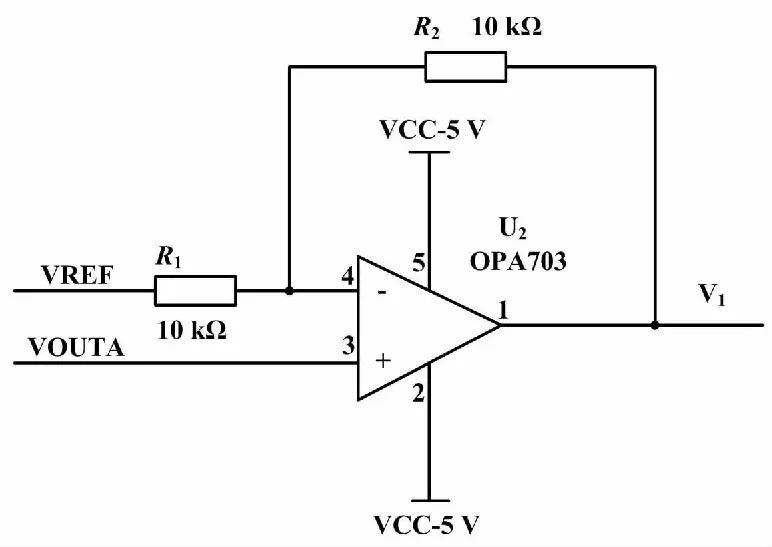

2.2 輸出調(diào)理電路設(shè)計

為了獲得雙極性±5 V電壓輸出,要在輸出的UOUT信號后接1個運算發(fā)大器OPA703,配置R1=R2=10 kΩ。此時,雙極性輸出Uk(k=1,2,3,4)可由式(3)得到。

(3)

經(jīng)DAC轉(zhuǎn)換后的模擬信號需要經(jīng)過濾波處理,濾除輸出信號中不必要的諧波分量[7]。本設(shè)計采用7階橢圓濾波器,截止頻率為10 MHz。該濾波器具有陡峭的衰減性,過度效果良好。雙極性輸出電路如圖4所示。

圖4 雙極性輸出電路

3 系統(tǒng)軟件邏輯設(shè)計

信號源系統(tǒng)的軟件設(shè)計內(nèi)容包括PCIe接口邏輯、信號發(fā)生邏輯、雜散處理與上位機軟件。根據(jù)PCIe傳輸協(xié)議和DDS信號發(fā)生原理,在VIVADO軟件中采用Verilog硬件描述語言進行設(shè)計。該系統(tǒng)采用Xilinx公司7系列的XC7K325T作為主芯片,具有豐富的邏輯存儲資源[8]。在VIVADO開發(fā)平臺中,可調(diào)用內(nèi)部提供的XDMA IP核、RAM IP核與DDS Compiler IP核,從而降低系統(tǒng)的設(shè)計難度。

3.1 PCIe接口邏輯設(shè)計

PCIe接口用于實現(xiàn)上位機與FPGA之間的高速數(shù)據(jù)和命令的傳輸。本方案采用PCIe2.0 ×8接口,理論傳輸帶寬可達到4 GB/s。Xilinx公司提供的XDMA IP核不僅對數(shù)據(jù)鏈路層和物理層的數(shù)據(jù)包進行了封裝,而且處理了事務(wù)層傳輸線脈沖發(fā)生器(transmission line pulse,TLP)的組包解包。XDMA IP核的接口中,M_AXI和 M_AXI_ LITE接口都是數(shù)據(jù)傳輸接口。前者一般與先入先出(first input first ouput,FIFO)隊列或雙倍速率(double data rate,DDR)通信。后者一般用于配置信息,將數(shù)據(jù)存于雙極隨機存取存儲器(bipolar access memory,BRAM)中。

對XDMA IP核進行配置時,選擇×8通道、AXI接口數(shù)據(jù)位寬為128位、參考時鐘為100 MHz。啟動一次直接存儲器訪問(direct memory access,DMA)操作,總線開始傳輸多個非連續(xù)存儲塊數(shù)據(jù),并在主機上對寄存器進行處理[9]。控制信息通過M_AXI_ LITE接口映射到BRAM用戶邏輯地址。波形數(shù)據(jù)下發(fā)到DAC8544之前,通過M_AXI接口接到異步FIFO緩存,以保證信號發(fā)送的連續(xù)性。

3.2 信號發(fā)生邏輯設(shè)計

在本文設(shè)計中,基本信號類型的發(fā)生需按地址查詢RAM中的波形數(shù)據(jù)表,調(diào)用Block Memory Generator IP核,申請1塊BRAM地址空間。1個周期的波形數(shù)據(jù)以.coe文件存儲在該空間中。同時,使用Xilinx公司的DDS IP核。DDS IP核集成了相位發(fā)生器和正余弦查找表的功能,可以設(shè)置成單獨或組合使用,能產(chǎn)生連續(xù)的相位值尋址存儲RAM。

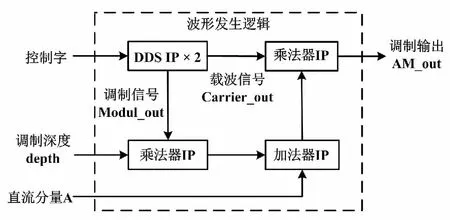

調(diào)制波形的實現(xiàn)原理是在高頻的載波信號中攜帶根據(jù)幅度或頻率變化的低頻信息[10]。調(diào)幅(ampltude modulation,AM)采用雙DDS結(jié)構(gòu),分別產(chǎn)生調(diào)制信號Modulate_out與載波信號Carrier_out。調(diào)制信號經(jīng)乘法器IP核與調(diào)制深度depth相乘,再經(jīng)加法器IP核與直流分量A相加。調(diào)制深度在0~1之間,以0.1為間隔分為11個等級。加法器輸出的信號與載波信號相乘就可以得到AM調(diào)制波形。該調(diào)制波形的幅度變化表示了調(diào)制信號內(nèi)容,而其頻率為載波信號頻率。

AM信號實現(xiàn)邏輯如圖5所示。

圖5 AM信號實現(xiàn)邏輯框圖

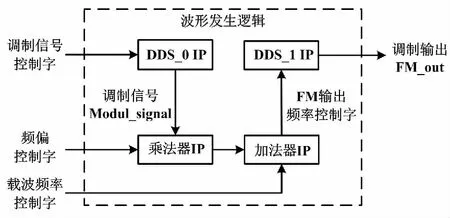

調(diào)頻(frequency modulation,F(xiàn)M)調(diào)制波形的頻率是隨調(diào)制信號幅度變化而改變的,且幅值保持不變。設(shè)計時,設(shè)置FM調(diào)制波形的中心頻率f0為5 MHz,最大頻偏fd為4 MHz。該中心頻率即為載波的頻率。當輸入調(diào)制信號幅度最大(即+215)時,將其與頻偏設(shè)置值相乘,輸出FM頻率最大值為9 MHz。反之,當輸入調(diào)制信號幅度最小(即-215)時,輸出FM頻率最小值為1 MHz。頻偏后的頻率控制字經(jīng)加法器運算輸出給DDS IP核,得到頻率變化的FM調(diào)制波。FM信號實現(xiàn)邏輯如圖6所示。

圖6 FM信號實現(xiàn)邏輯框圖

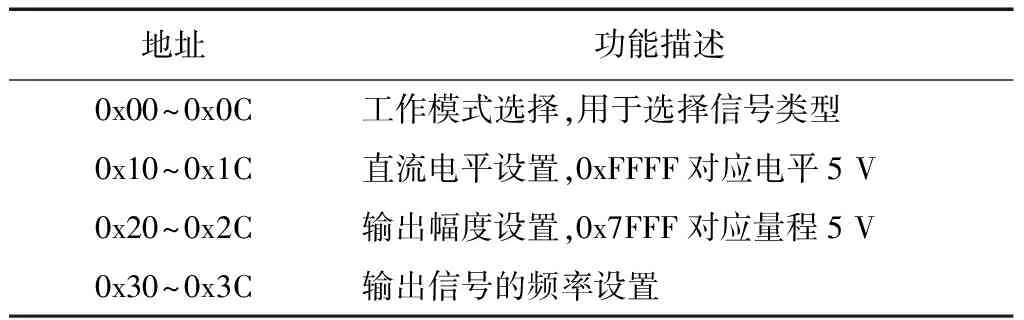

任意波形的實現(xiàn)均采用上位機下發(fā)自定義波形數(shù)據(jù)。上位機將自定義的波形數(shù)據(jù)存入主機寄存器,通過PCIe以DMA方式下發(fā)到用戶邏輯側(cè)寄存器,存入RAM后經(jīng)過DAC輸出。信號源的控制寄存器地址說明如表1所示。

表1 寄存器地址說明

3.3 雜散處理設(shè)計

經(jīng)過分析,DDS信號源系統(tǒng)的雜散源自相位截斷以及幅值量化的過程。為了獲得較好的頻率分辨率,本文設(shè)計系統(tǒng)時鐘為100 MHz、DDS查找表相位寬度N為32位,再根據(jù)式(1)可得頻率最小分辨率為0.023 Hz。但由于太高的相位寬度占用了很大的存儲容量,會消耗芯片存儲資源,本文使用相位截斷,選擇累加器的高16位進行波形數(shù)據(jù)表的尋址。由于相位截斷造成可尋址的相位點變少,此時便引入了相位截斷誤差,使得輸出波形引入雜散,并且分析相位誤差序列可知其與輸出的雜散均具有周期性[11]。另外,波形查找表中存儲的是二進制數(shù)據(jù),需要量化為波形的幅值。而在一般DDS方案中,并非波形存儲器中的每個單獨點都在結(jié)果輸出波形中表示。相反,DDS輸出波形的最佳近似值部分或完全跳過了波形中的小特征,嚴重時會導(dǎo)致失真。

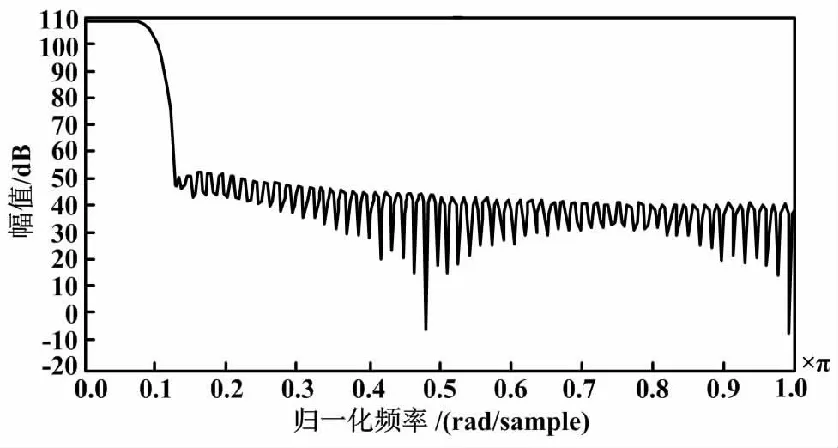

針對相位截斷引起的雜散具有周期性的特點,Xilinx提出1種相位抖動解決方案,即在DDS IP核中提供1種隨機化信號,打破地址錯誤的規(guī)律性,提供約12 dB的無雜散動態(tài)范圍[12]。設(shè)計者只需在配置IP核時,在系統(tǒng)參數(shù)的噪聲整形選項中選中增加相位抖動,即可極大程度地提高輸出信號的質(zhì)量。針對幅值量化引起的雜散,本設(shè)計方案采用了插值濾波處理,使用Xilinx提供的FIR IP核,可對波形存儲器輸出的值實時內(nèi)插,并實現(xiàn)低通濾波。FIR IP核中可導(dǎo)入帶有濾波器設(shè)置參數(shù)的.coe文件。此文件可由MATLAB軟件中的Filter Designer產(chǎn)生。在軟件中的參數(shù)上選取采樣頻率為200 MHz、截止頻率為10 MHz、濾波窗函數(shù)為Hamming、插值倍數(shù)為10倍。所設(shè)計的FIR歸一化幅頻特性曲線如圖7所示。

圖7 FIR 歸一化幅頻特性曲線

插值濾波過后的波形數(shù)據(jù)在不提高芯片分辨率的情況下,既節(jié)省了存儲容量,又能通過DAC精確地反映信號的頻率特性。

3.4 上位機軟件設(shè)計

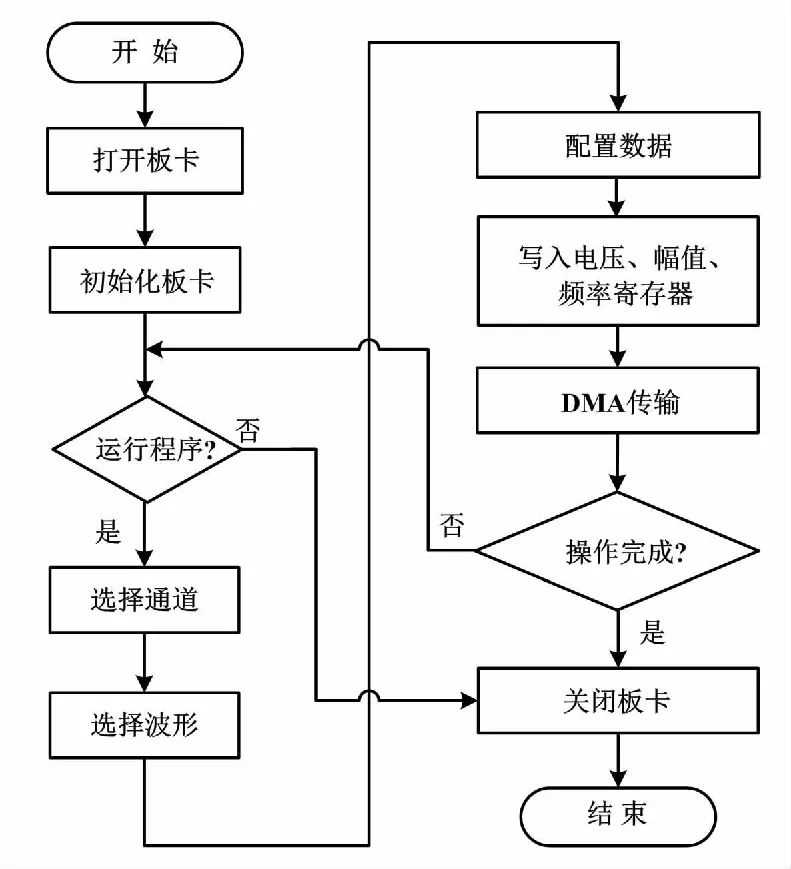

上位機軟件基于LabVIEW平臺設(shè)計,可實現(xiàn)人機交互功能。通過PCIe下發(fā)指令和波形數(shù)據(jù),在選中并初始化信號源測試板卡后,對是否運行程序作出判斷。若在運行狀態(tài)下,則選擇信號輸出通道、信號的波形種類及幅值頻率等參數(shù)。參數(shù)數(shù)據(jù)存放在規(guī)定地址的主板寄存器中。如4個通道的輸出電壓幅值寄存器地址范圍為0x20、0x24、0x28、0x2C,對應(yīng)地址處寫入數(shù)值0~0x7FFF,即可輸出幅值為0~5 V的電壓。寄存器中的數(shù)據(jù)通過PCIe的DMA操作,直接與FPGA的存儲單元進行傳輸,從而控制信號源的輸出。上位機設(shè)計流程如圖8所示。

圖8 上位機設(shè)計流程圖

在上位機界面中,用戶使用鼠標點擊布爾開關(guān)使能輸出通道,通過鍵盤可寫入幅值、頻率等參數(shù)值。用戶選擇板卡及通道并設(shè)定參數(shù)后,可以在波形顯示界面預(yù)覽輸出信號特征,以便使用。

4 試驗測試結(jié)果與分析

4.1 PCIe數(shù)據(jù)傳輸

PCIe具有高帶寬、高速數(shù)據(jù)傳輸能力的特點,通過上位機向FPGA發(fā)起DMA寫操作,發(fā)送含目的地址、傳輸大小及數(shù)量信息的TLP配置寄存器。配置信息完成后,在上位機終端測試將一個大小為8 MB的bin文件傳輸?shù)紽PGA,同時再以二進制文件形式讀取文件。經(jīng)測試,8 388 608 B大小的數(shù)據(jù)寫入時間為0.002 556 s,寫數(shù)據(jù)速度為3 129.9 MB/s。此外,讀取文件中的數(shù)據(jù)與發(fā)送數(shù)據(jù)一致,表明數(shù)據(jù)傳輸正確,具有很高的完整性。

4.2 四通道波形輸出

將設(shè)計的信號源輸出端連接到示波器后進行觀察,可以在示波器上觀察到波形輸出。頻率控制字FW設(shè)置為42 950時的正弦波,則測得波形輸出頻率為近似1 KHz,輸出幅值為近似5 V,且波形無明顯失真。

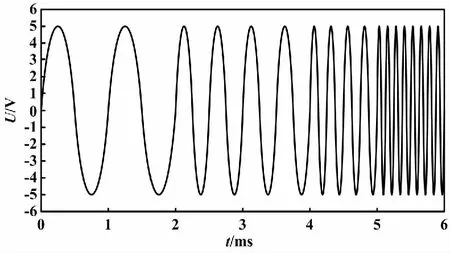

通過波形輸出驗證,本文設(shè)計的信號源輸出頻率范圍為10 Hz~10 MHz,三角波與鋸齒波頻率最高為5 MHz,在范圍內(nèi)無明顯失真情況。分別設(shè)置頻率控制字為42 950、85 900、214 748、429 497,正弦波輸出頻率在1 kHz、2 kHz、5 kHz、10 kHz連續(xù)變化。正弦波變頻輸出曲線如圖9所示。

圖9 正弦波變頻輸出曲線

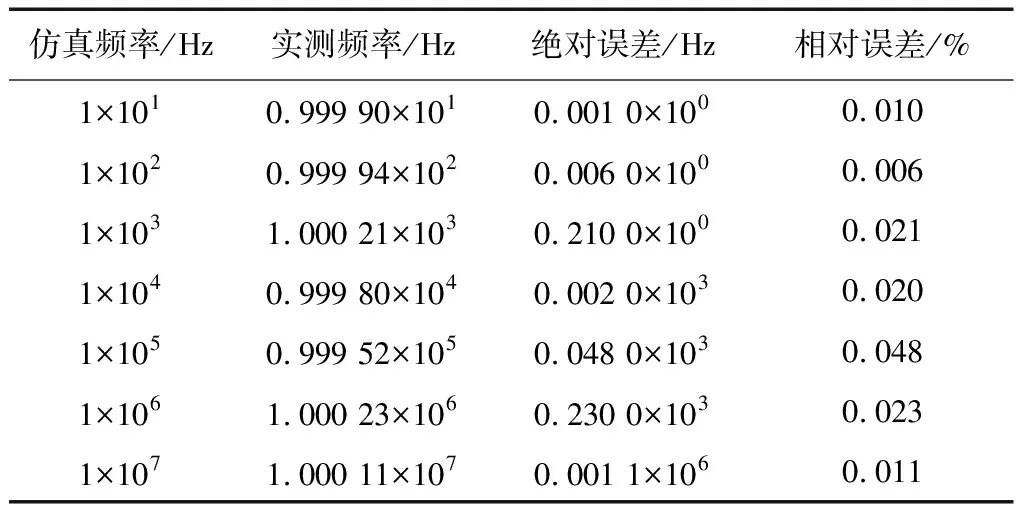

分析各頻率點測量值與設(shè)置值的誤差,雖然相對誤差隨頻率變化波動,但都維持在0.01%~0.05%之間,精度高于傳統(tǒng)信號源。正弦波輸出頻率誤差分析如表2所示。

表2 正弦波輸出頻率誤差分析

4.3 輸出信號頻譜分析

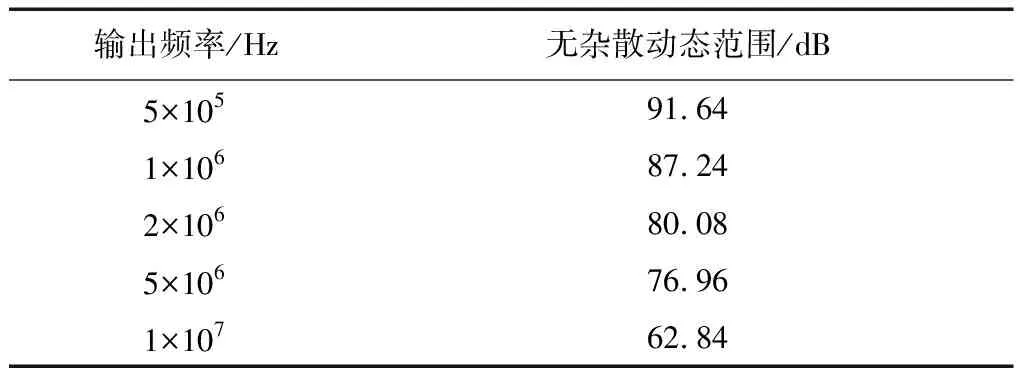

使用ROHDE&SCHWARZ示波器對信號的無雜散動態(tài)范圍進行測試,使信號源輸出5 MHz正弦信號。近端雜散測試范圍在100 MHz以內(nèi),無雜散動態(tài)范圍可達76.96 dB。輸出信號雜散測試結(jié)果如表3所示。

表3 輸出信號雜散測試結(jié)果

5 結(jié)論

本文設(shè)計的高精度低雜散信號源基于FPGA與DAC8544芯片,利用Xilinx豐富的IP核資源,實現(xiàn)了4通道的任意信號輸出。該信號源擁有多種波形輸出類型及幅度頻率可調(diào)的功能,通過PCIe發(fā)送波形數(shù)據(jù),具備根據(jù)用戶要求實時輸出信號的能力。在信號發(fā)生邏輯中,創(chuàng)新使用FIR插值濾波技術(shù),采用DDS IP核設(shè)計,利用相位抖動技術(shù),輸出信號頻譜質(zhì)量較好。輸出信號頻率誤差比一般信號源誤差更小、精度更高,同時電路體積與復(fù)雜程度更小。經(jīng)試驗驗證,該信號源的功能豐富、使用方便,具有PCIe標準化接口,可制成板卡,集成于儀器儀表,用于壓力測試系統(tǒng),為測試系統(tǒng)提供模擬信號源。目前,該信號源模塊已實現(xiàn)產(chǎn)品設(shè)計,并已應(yīng)用于某沖擊波壓力測試儀。但本文設(shè)計還存在一些不足之處,后續(xù)研究還可以考慮提升輸出信號的帶寬,同時保證高頻輸出信號的頻譜質(zhì)量。