一種數字波束合成處理架構及其子陣設計

李 杰,李 翔,侯京辰

(成都振芯科技股份有限公司,四川 成都 610000)

0 引 言

基于數字波束合成(DBF)技術的數字相控陣具有靈活多變的波束控制及調度功能,易于實現收/發并行多波束,支持自適應數字波束形成(ABDF)功能。與傳統模擬相控陣相比,數字相控陣在多目標并行跟蹤、抗干擾能力、瞬時動態范圍、雜波抑制等方面具有明顯優勢[1-3],可用于雷達[4-6]、電子對抗[7-9]、衛通測控[10-11]等領域,應用前景廣泛。

DBF處理架構是數字相控陣系統的核心技術之一,直接影響數字相控陣系統的成本、尺寸、功耗、功能性能、技術先進性、可重構特性等指標。常見的DBF處理架構采取電傳輸及多級合成的分布式處理方案,技術成熟,但是系統體積大,難以滿足收發通道與數字處理分開的技術發展趨勢。本文以某數字相控陣項目的DBF處理架構為研究對象,考慮技術先進性以及較高的尺寸限制,并著眼于未來技術發展趨勢,提出了一種基于光傳輸的集中式DBF處理架構,并完成對其可重構處理子陣的詳細設計、樣機制造及試驗驗證。

1 數字波束合成處理架構設計

根據某項目需求,針對數字波束合成處理架構問題,提出2種解決方案:(1)電傳輸及分布式處理架構;(2)光傳輸及集中式處理架構。下面研究分析2種處理架構的詳細方案及其優缺點,在此基礎上確定該項目的數字波束合成處理架構。

1.1 電傳輸及分布式處理架構

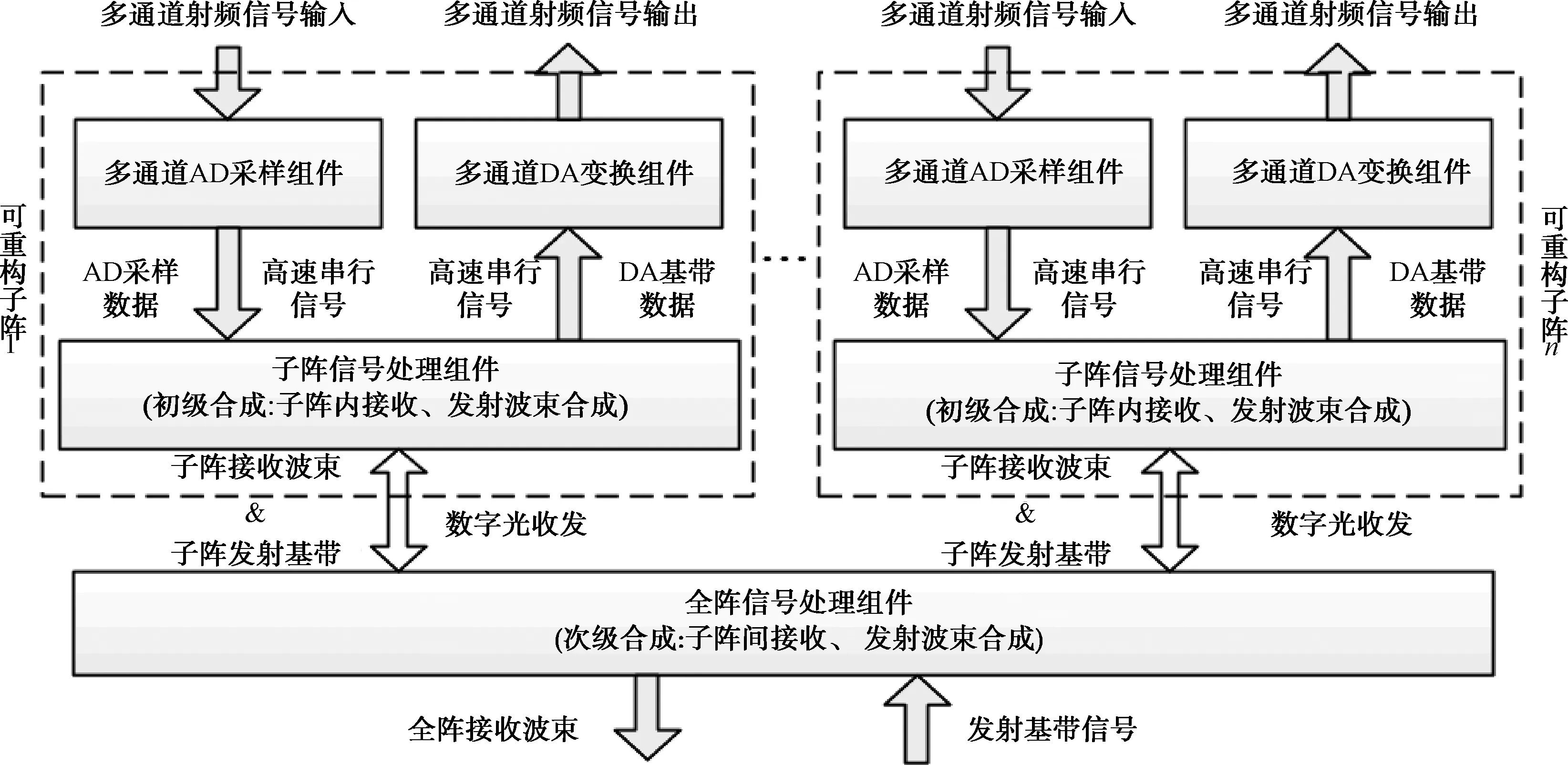

電傳輸及分布式數字波束合成處理架構如圖1所示,其主要特點為:

圖1 電傳輸及分布式數字波束合成處理架構

(1)在結構尺寸滿足要求的情況下,信號處理組件位于各個可重構子陣內部,系統整體結構更加緊湊,但是單個可重構子陣的尺寸增加,對系統尺寸的要求更高,是一種較為傳統的處理架構方案;

(2)采用分布式數字波束合成處理架構,各個可重構子陣獨立完成初級波束合成,再由全陣信號處理組件完成全陣波束合成;

(3)各個可重構子陣對外輸出波束合成數據,合成波束個數遠小于通道個數,數字光收、發組件的成本更低;

(4)單個可重構子陣結構緊湊,信號處理組件、模數轉換(ADC)采樣組件和數模轉換(DAC)組件同在一個子陣內部,距離近,大規模通道數據的高速傳輸可采用電傳輸方案,成本低;

(5)通過子陣重構,可實現任意規模陣列的擴展。

1.2 光傳輸及集中式處理架構

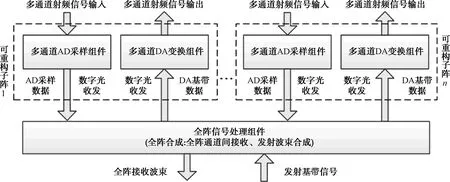

光傳輸及集中式數字波束合成處理架構如圖2所示,其主要特點為:

圖2 光傳輸及集中式數字波束合成處理架構

(1)信號處理組件獨立于各個可重構子陣,可重構子陣的結構更加緊湊;

(2)數據采集和數據處理相互獨立,子陣波束合成處理和全陣波束合成處理集中在具有超大規模計算能力的全陣信號處理組件中完成;

(3)集中式處理架構是一種較為先進的處理架構,符合數字陣列的發展趨勢,如智能蒙皮、模數/數模(AD/DA)轉換前移、超高速光傳輸、集中式信號處理等;

(4)信號處理組件獨立于各個可重構子陣,信號處理組件與ADC采樣組件、DAC變換組件的距離較遠,為提高傳輸可靠性,需采用光傳輸方案,成本較高;

(5)通過子陣重構,可實現任意規模陣列的擴展。

1.3 對比分析及結論

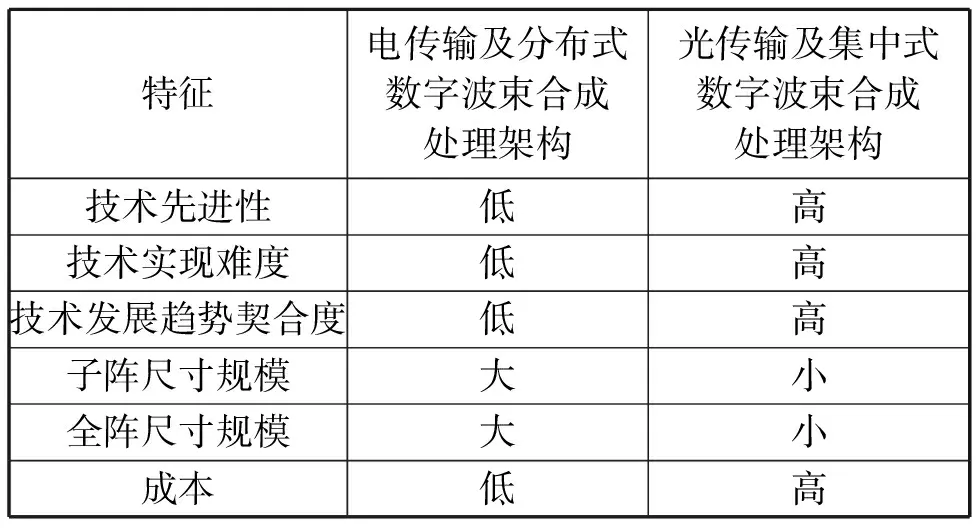

根據分布式處理架構方案及集中式處理架構方案的特點,2種方案對比分析結果如表1所示。

根據表1 的分析結果可知,光傳輸及集中式處理架構比電傳輸及分布式處理架構在技術先進性、技術發展趨勢契合度、尺寸規模等方面具有明顯優勢,但是光傳輸及集中式處理架構的技術實現難度及成本較高。

表1 數字波束合成處理架構方案對比分析結果

光傳輸及集中式處理架構的技術實現難度和成本主要受限于高速、高容量數字收發光模塊。根據前期技術調研,國內部分廠家可研制滿足技術要求的收發光模塊。隨著技術的發展,數字收發光模塊的技術穩定性和成本將逐漸改善,可進一步降低光傳輸及集中式處理架構的技術實現難度和成本。

綜合以上分析,考慮項目的技術先進性以及較高的尺寸限制,并著眼于未來技術發展趨勢,擬采用光傳輸及集中式數字波束合成處理架構方案。

2 可重構處理子陣設計

2.1 功能視圖

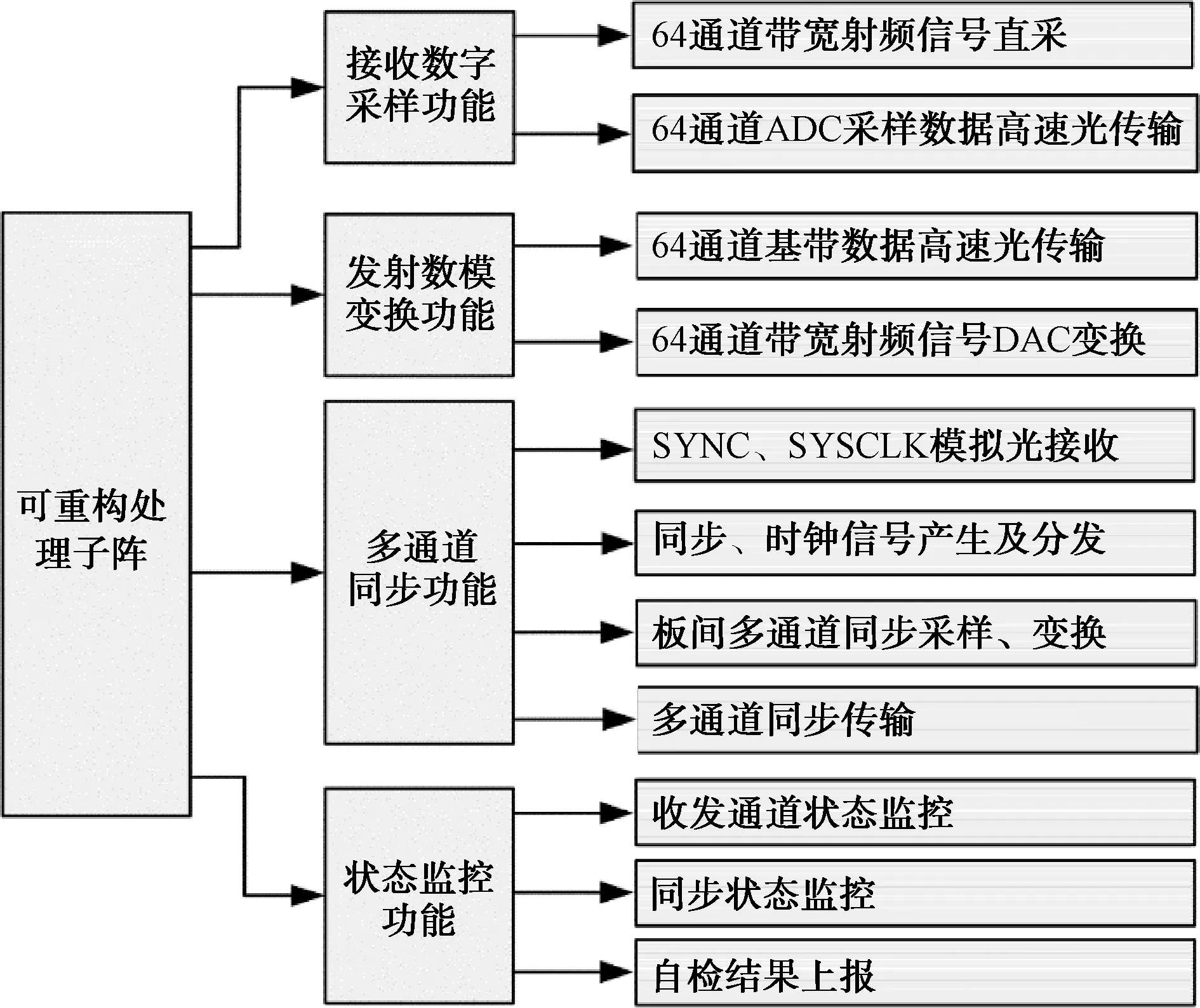

根據圖2可知,基于子陣重構方法,可實現陣列通道數目的任意擴展,可重構子陣是陣列的最小功能顆粒,其功能視圖如圖3所示。可重構子陣主要完成接收采樣、發射數模變換、數字光發射、數字光接收、多接收通道同步、多發射通道同步及狀態監控等功能。

圖3 可重構處理子陣功能視圖

2.2 硬件架構

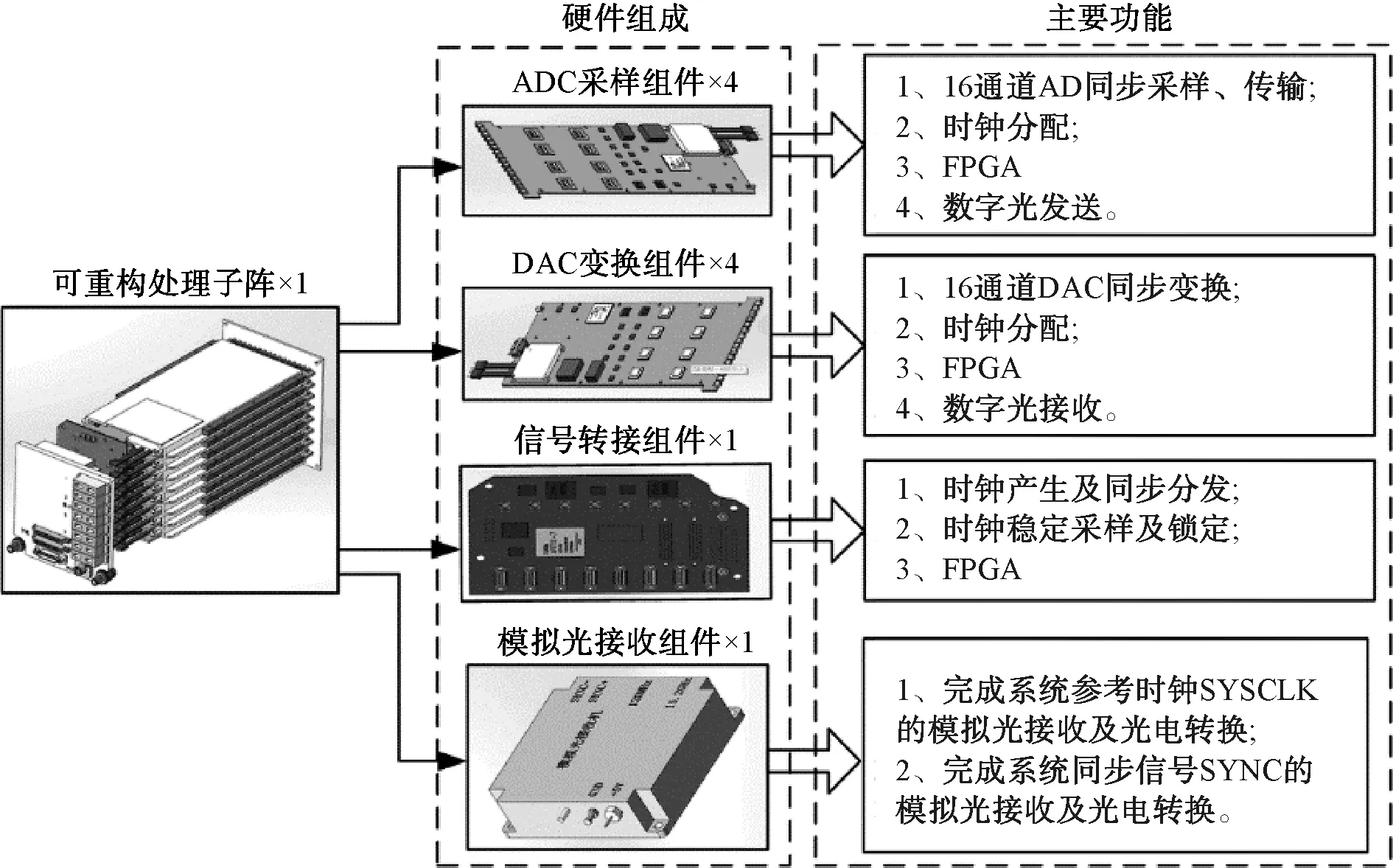

可重構子陣的硬件組成如圖4所示,包括4個ADC采樣組件、4個DAC變換組件、1個信號轉接組件以及1個模擬光接收組件,核心元器件或者模塊包括64路ADC、64路DAC、數字光收發組件、模擬光收發組件、時鐘分發模塊、現場可編程門陣列(FPGA)配置芯片等。

圖4 可重構處理子陣硬件架構

2.3 總線關系及互聯邏輯

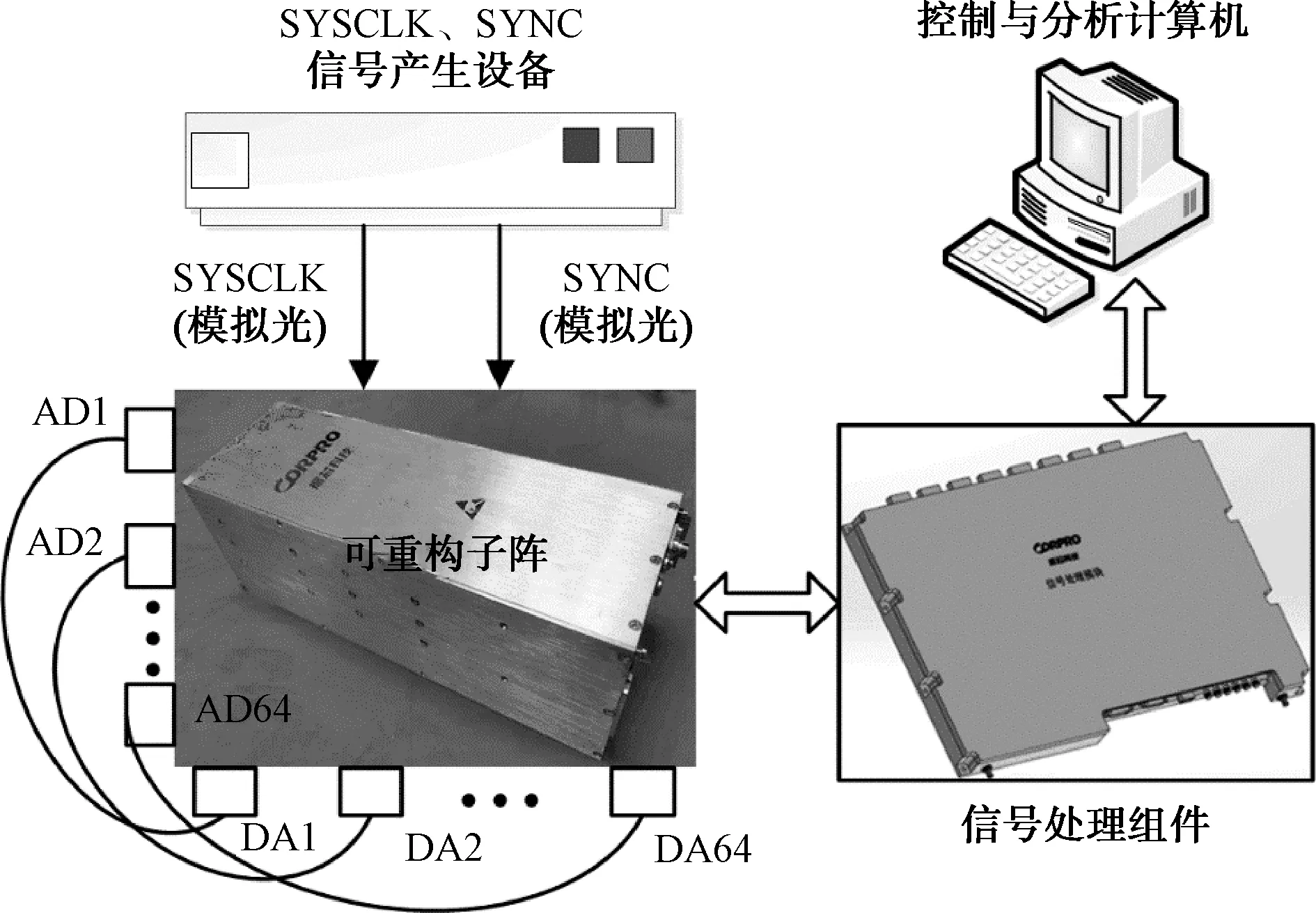

可重構處理子陣總線關系及互聯邏輯如圖5所示,外部交互接口包括64路射頻信號輸入、64路射頻信號輸出、多路數字光輸入及輸出、系統同步SYNC信號模光接口、系統參考時鐘SYSCLK模擬光接口、供電及系統控制調試接口,其中:

圖5 可重構處理子陣總線關系及互聯邏輯

(1)64路射頻信號輸入由ADC采樣組件完成采集,通過數字光發送模塊送入陣列的信號處理組件完成波束合成;

(2)DAC變換組件的數字光接收模塊接收來自信號處理組件的數字基帶數據,并由DAC芯片完成64路射頻信號輸出;

(3)系統同步SYNC信號、系統參考時鐘SYSCLK信號由模擬光組件完成接收,并進行光電轉換;

(4)信號處理組件通過控制調試接口實現對可重構子陣的配置和控制;

(5)信號轉接組件接收模擬光組件的同步SYNC信號及系統參考時鐘SYSCLK信號,產生ADC組件、DAC組件所需的同步信號和時鐘信號。

2.4 功能軟件架構

陣列系統的軟件架構組成如圖6所示,主要包括接口通信、芯片配置、系統控制以及波束合成等功能。其中:

圖6 可重構處理子陣功能軟件架構

(1)信號處理模塊的FPGA1駐留接口通信程序、系統控制程序、波束合成程序以及芯片配置程序,用于完成上位機通信、系統控制、發射/接收波束合成以及信號處理模塊芯片的基礎配置;FPGA2、FPGA3、FPGA4駐留接口通信程序和波束合成程序,用于完成各自FPGA的對外通信交互及發射/接收波束合成;

(2)可重構子陣的信號轉接組件、ADC采樣組件、DAC變換組件駐留接口通信程序和芯片配置程序,用于完成各組件上FPGA_A7的對外通信交互及芯片的基礎配置。

3 試驗分析

根據前述分析,設計制造的可重構處理子陣實物如圖7所示,與信號處理子陣配合,可同時完成64(8×8)通道接收、發射數字波束合成。為測試波束合成結果,搭建如圖8所示的波束方向圖掃描測試系統。

圖7 可重構處理子陣實物

圖8 可重構處理子陣波束方向圖掃描試驗框圖

測試流程說明如下:

(1)外置信號產生設備,按照時序要求,生成可重構子陣所需的SYNC信號和SYSCLK信號,電光轉換后,發送給可重構子陣;

(2)可重構子陣的DAC輸出接入可重構子陣的ADC輸入;

(3)獲取通道間的幅相不一致性,并進行通道校準;

(4)信號處理組件集成發射數字波束合成功能和接收數字波束合成功能,通過發射波束合成功能模擬不同來波方向對應的時差和相位差,并通過可重構子陣的DAC輸出滿足通道間時差和相位差要求的射頻信號;

(5)可重構子陣的ADC采集DAC輸出的模擬不同來波方向的射頻信號,信號處理組件的接收波束合成功能完成接收波束合成,并提取波束幅度;

(6)發射波束合成功能完成全空域模擬來波方向掃描,通過接收波束合成,即可形成全空域的波束方向圖。

按照上述流程,僅考慮一維8通道數字波束合成,采集完成的波束方向圖如圖9所示。其中,波束指向從左到右依次為-70°~70°,按照10°步進。根據圖9可知,各個合成波束的指向正確,主副瓣比符合理論分析結果,設計的可重構子陣可用于任意規模數字陣列的擴展重構。

圖9 可重構處理子陣波束方向圖掃描結果

4 結束語

針對某數字陣列項目需求,考慮項目的技術先進性以及較高的尺寸限制,并著眼于未來技術發展趨勢,設計了一種光傳輸及集中式數字波束合成處理架構,并對該處理架構的可重構處理子陣進行了詳細設計。基于該處理架構以及可重構處理子陣,可實現任意規模數字陣列的擴展。為驗證處理架構、可重構處理子陣設計結果的正確性,搭建試驗系統,獲取了可重構處理子陣實物的數字波束合成方向圖。測試結果表明,可重構處理子陣合成波束的指向正確,主副瓣比符合理論分析結果,可用于任意規模數字陣列的擴展重構。