基于FPGA 和ARM 內核的無線SoC 設計

魏繼清

(電子科技大學 電子科學與工程學院,四川成都,611731)

0 引言

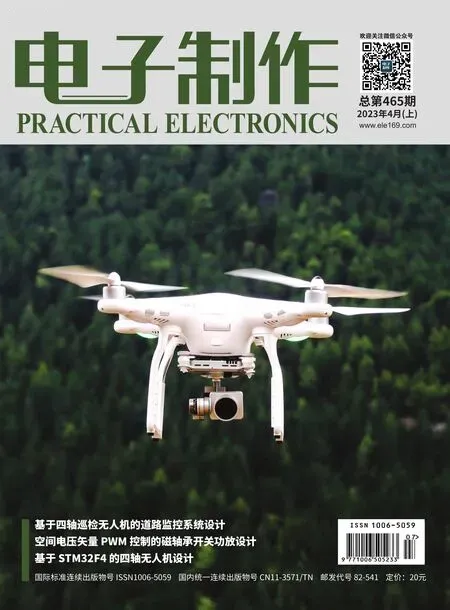

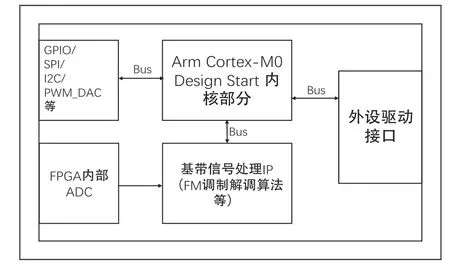

無線SoC 已成為物聯網產業發展的基礎,在現代信息社會中占有越來越重要的地位。但由于課程體系等多方面的原因,同時熟悉無線通信和SoC 設計的人才極為稀缺。本文基于ARM Cortex-M0 處理器在FPGA 上構建具備無線通信基帶信號處理的片上系統,配合控制外圍擴展電路實現FM 通信信號的調制解調等處理。在此基礎上增加適當的功能以滿足特定的物聯網應用,使系統具有實用性、可演示性和創新性,同時兼顧了系統靈活性、可移植性、通用性的要求[1]。該系統的總體設計框圖如圖1 所示。

圖1 無線SoC 系統框圖

1 無線SoC 系統

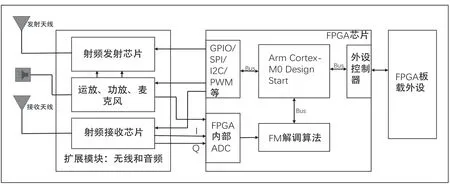

由圖1 可知,將ARM Cortex-M0 內核移植到FPGA上并在FPGA 上構建好硬件系統后,再與射頻擴展模塊、FPGA 板載外設模塊相連接即可構成無線SoC 系統的硬件部分,還需軟件和硬件協同,即可構成完成的無線SoC,二者之間通過指令集架構搭建起橋梁,如圖2 所示。

圖2 軟硬件開發層次

整個系統的開發流程為:

(1)將ARM Cortex-M0 軟核移植到FPGA 芯片上;

(2)使用Verilog 硬件描述語言搭建SoC 系統,包括搭建外設驅動、編寫基帶信號處理IP、連接射頻擴展模塊與外設模塊等;

(3)在集成開發環境keil 中編寫軟件代碼,生成十六進制機器碼;

(4)將機器碼下載至FPGA 中的ARM 內核中,進行仿真;

(5)燒錄到FPGA 中并調試。

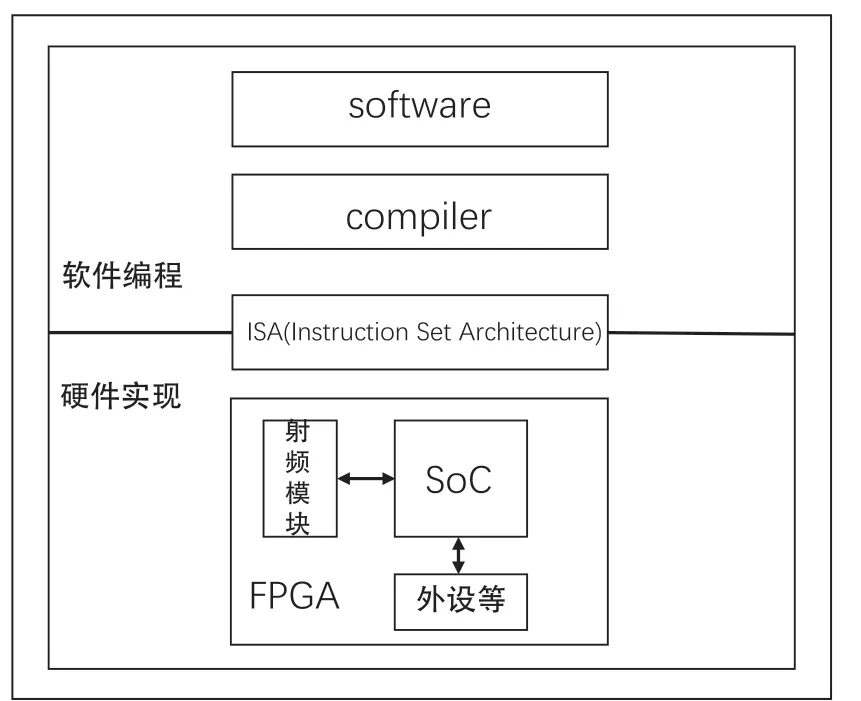

其中的軟件控制流程為:該系統上電復位以后,初始化所有外設并打開中斷,然后通過SPI 模塊與射頻接收芯片通信,來選擇接收的頻點,接著將接收到的FM 模擬信號送入AD 模塊轉換為數字信號,在基帶信號處理IP 中進行FM解調,將解調后得到的數字信號經DA 轉換后送入音頻輸出電路播放;在程序的執行過程中,隨時可以通過GPIO 按鍵觸發中斷,執行對應的中斷程序,中斷程序的功能有:可以通過按鍵更換接收的頻點、可以通過按鍵發射FM 信號、可以通過按鍵保存頻點、可以通過按鍵與上位機UART 通信,將接收的頻點信息發送給上位機等。軟件系統控制流程如圖3 所示。

圖3 軟件系統執行流程

2 FPGA 片上無線系統電路

2.1 ARM 內核模塊

ARM 處理器采用精簡指令集(RISC)處理器架構,Cortex-M 系列在低功耗、微控制系統領域應用廣泛,且使用keil 集成開發環境,可迅速完成軟件應用程序開發,以及實現設計代碼的重用,具有極大優勢[2]。Cortex-M0 微處理器包括:處理器核、嵌套向量中斷控制器(NVIC)、調試子系統、喚醒中斷控制器、AHB-Lite 總線接口以及連接這些單元的內部總線系統。處理器核對數據進行處理,包含內部寄存器、算術邏輯單元(ALU)、數據通路和控制邏輯,取指、譯碼和執行的指令通道采用三級流水結構,顯著提高處理器指令通道的吞吐量和運行效率。嵌套中斷向量控制器包含32 個中斷請求信號,以及一個不可屏蔽中斷。調試子系統用于管理調試、程序斷點,以及數據監控點。喚醒中斷控制器用于低功耗應用,通過關閉大部分元件,使微處理器進入休眠模式,當檢測到中斷事件時,通知電源管理單元上電,使處理器從休眠狀態進入到正常工作狀態。AHB-Lite 總線系統也與傳統的總線相同,包括地址總線、控制總線和數據總線,總線用于處理器核和其他模塊之間的通信,處理器核為主機,其他所有模塊都為從機。該項目的FPGA 片上無線系統電路如圖4 所示。

圖4 FPGA 片上系統框圖

2.2 基帶信號處理IP 模塊

基帶信號處理IP 包括兩個部分,一是將ADC 送過來的數字FM 調制信號進行解調;二是將麥克風電路輸入的語音模擬信號經AD 轉換后進行FM 調制。

2.2.1 FM 數字正交解調

軟件無線電一般采用數字正交解調法,實際工程中,一般調制都能用正交調制法進行,實質上調制不外乎用調制信號去控制一個載波的某一個或幾個參數,讓這個給參數按照調制信號的規律變化,載波可以是正弦波或脈沖序列,以正弦信號作為載波的調制叫做連續波調制,FM 是一種連續波調制,且是對載波信號的頻率進行調制的方法。對于連續波調制,以調信號的數字表達式如公式所示:

將上式和差化積后得到公式:

式中:

由于我們的射頻接收芯片已經將I、Q 兩路信號得出,所以我們只需要AD 轉換后進行解調算法的編寫即可。利用相位差分計算瞬時頻率f(n)時,由于計算相位要用到除法和反正切運算,這對于非專用數字處理器來說是較復雜的,在用軟件時,也可以用下面的方法來計算瞬時頻率f(n):

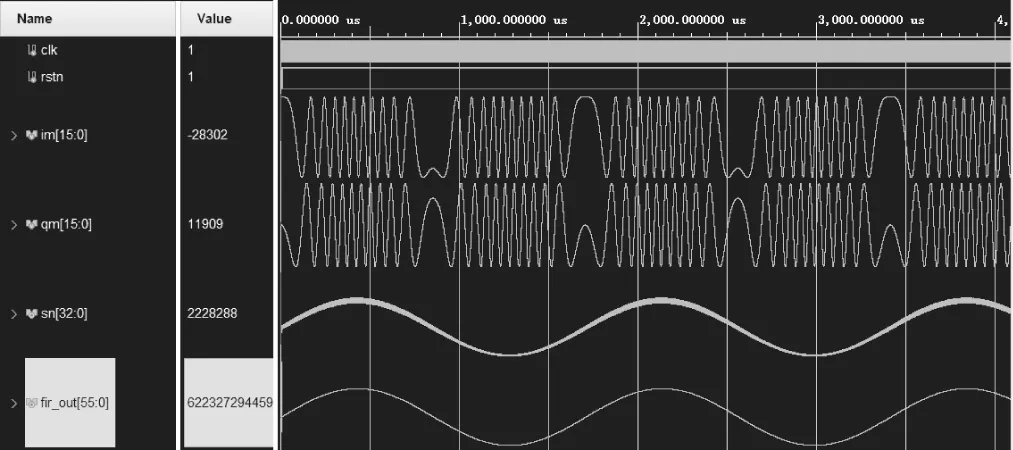

這種方法只有乘法和減法[3],計算起來簡便,最后我們仿真將其實現,如圖5 所示,可知經過I、Q 兩路信號解調出來的信號(倒數第二行波形)有些許高頻噪聲,再加上低通濾波器去除高頻噪聲得到最后一行波形,即解調出來的波形。

圖5 FM 解調并濾波得到原信號

2.2.2 FM 數字調制

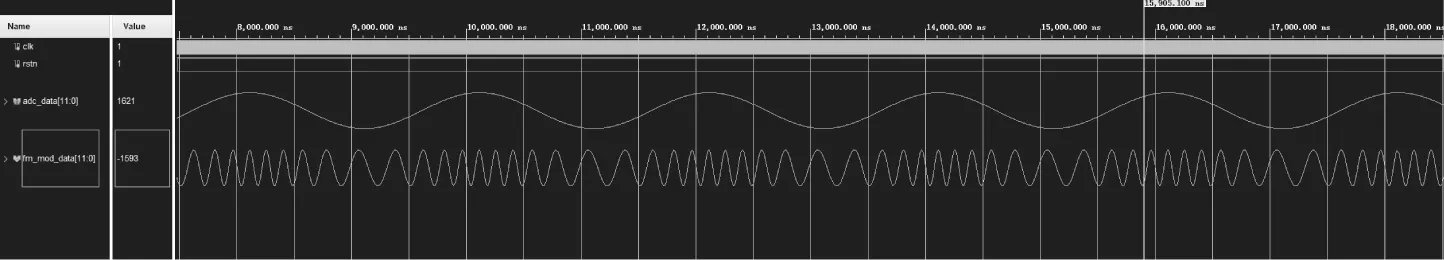

FM 調制模塊有兩個比較重要的概念:中心頻率和頻偏。頻偏即與中心頻率的差值。假設中心頻率為5MHz,頻偏為:-75kHz~75kHz,輸入信號位寬為12 位。當輸入調制信號幅度為0 時,輸出的FM 已調信號頻率為5MHz,即載波頻率;當輸入調制信號幅度最大(即+2^11)時,輸出的FM 已調信號頻率為5.075MHz(5M+75K);當輸入調制信號幅度最小(即-2^11)時,輸出的FM 已調信號頻率為4.925MHz(5M-75K),使用DDS 控制模塊可以實現FM 調制[4]。將其仿真得到如圖6 所示的結果,可知送入的信號以頻率為調制,即完成FM 調制。

圖6 FM 調制

2.3 外設模塊

搭載的外設有UART、SPI、I2C、LCD;其 中UART用于與上位機串口通信;SPI用于與射頻接收芯片通信,控制接收的頻段與頻點等;I2C用于與射頻發射芯片通信,控制發射;LCD 用于顯示接收和發射的頻點。

2.3.1 UART 模塊

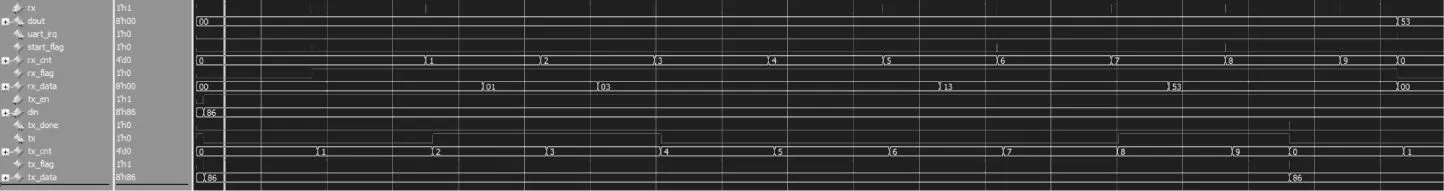

通用異步接收發送器(UART)用于實現兩個設備間的異步串行通信;UART 一幀數據由起始位開始,緊跟著八位數據位(由低到高)、奇偶校驗位(可選)、停止位結束。將UART 驅動連接到AHB-Lite 總線上,就可以實現SoC 與上位機之間的UART通信,硬件架構搭建完畢并成功仿真以后,在Keil 上進行軟件程序的編寫,編寫的軟件程序生成十六進制治理文件下載到Cortex-M0 內核中運行,從而可以控制UART 的發送與接收,仿真結果如圖7 所示。

圖7 UART 串行通信

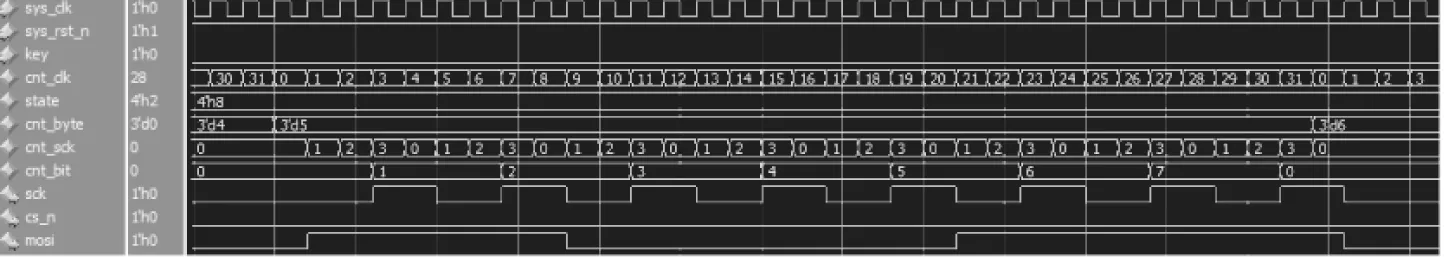

2.3.2 SPI 模塊

串行外圍設備接口(SPI)通訊協議,是一種高速、全雙工、同步通信總線,只需要四根線來控制數據傳輸,SPI通訊協議包含 1 條時鐘信號線、2 條數據總線和 1 條片選信號線,時鐘信號線為 SCK,2 條數據總線分別為 MOSI(主輸出從輸入)、MISO(主輸入從輸出),片選信號線為 CS;SPI 的優點是支持全雙工通信、速率較快,缺點是沒有應答機制,在數據可靠性上有一定缺陷;我們使用的射頻接收芯片是MSI001,其數據格式是24bits,20bits 是數據,4bits 是寄存器地址,我們通過SPI 發送24bits 數據,控制相應的寄存器配置成不同的值,就可以選擇頻段與頻點等;仿真結果如圖8 所示。

圖8 SPI 同步通信

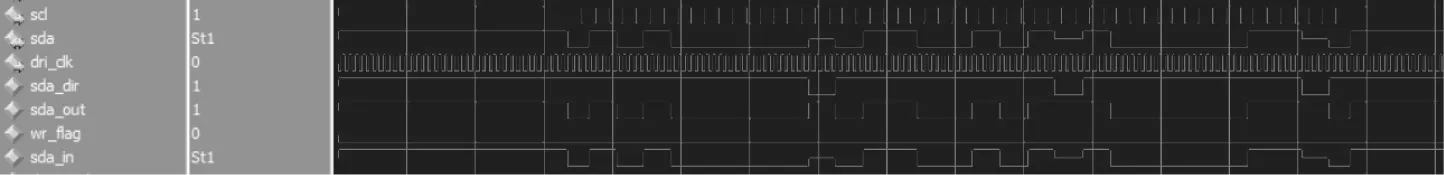

2.3.3 I2C 模塊

I2C 通信協議是雙向二線制同步串行總線,支持一主多從,總線通過上拉電阻連接到電源,當I2C 設備空閑時,輸出高阻態;當所有設備都空閑,都輸出高阻態時,由上拉電阻把總線拉成高電平;每一個從機都有一個獨立的地址,主機利用這個地址訪問不同的設備;I2C 總線只有兩條線,一條串行時鐘線(SCL)用來提供時鐘同步,同步數據的收發;一條串行數據線(SDA)用來讀寫數據,具有三種傳輸速率:標準模式傳輸速率為100kbit/s,快速模式為400kbit/s,高速模式可達3.4Mbit/s。SoC 通過I2C 控制發射芯片QN8027,將輸入的模擬音頻信號發射,I2C 仿真結果如圖9所示。

圖9 I2C 通信

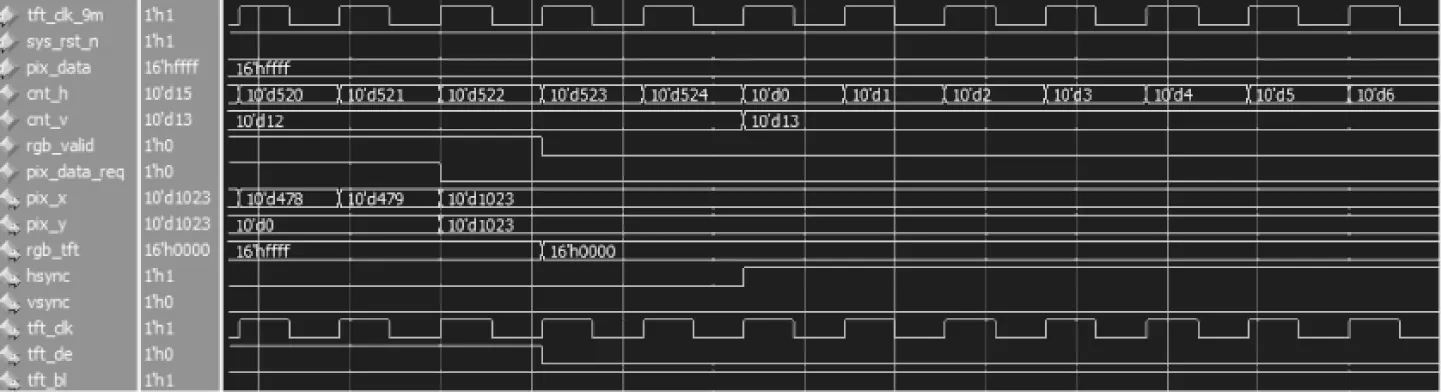

2.3.4 LCD 模塊

TFT-LCD 即薄膜晶體管液晶顯示器,它在液晶顯示屏的每一個像素上都設置一個薄膜晶體管,可有效克服非選通時的串擾,提高了圖片質量。本文使用到的2.4 寸LCD 屏采用的驅動芯片是ILI9341,且使用8080 16 位總線接口,可直插FPGA;LCD 模塊使用的基本原理是,主機通過引腳向驅動芯片發送一系列指令和數據,之后驅動芯片會根據這些指令和數據刷新LCD 屏幕并進行顯示。LCD 的仿真測試結果如圖10 所示。

圖10 LCD 模塊

3 射頻擴展模塊

射頻擴展模塊使用的是DMZ_FMSDR 開發板,可以和FPGA 開發板配合使用;DMZ_FMSDR 內部包含了50MHz~120MHz,400MHz~1000MHz 射 頻 接 收 電 路,76MHz~08MHz 的FM 頻道發射電路,麥克風電路,音頻輸出和功放電路,可以通過編程實現FM 收音機、FM 發射機、FM對講機以及其他頻段的接收機。

(1)射頻接收電路模塊可以接收多個頻段的信號,廣播信號FM 在VHF 頻段(64~108MHz),可以通過配置MSI001 寄存器的值來選擇;經過MSI001 芯片的處理后,下變頻產生I、Q 兩路信號,送到FPGA 的AD 接口;

(2)FM 頻道發射電路模塊發射頻率覆蓋76MHz~108MHz,支持立體聲或單聲道,輸出接拉桿天線,通過配置QN8027 的寄存器來配置發射頻點、時鐘選擇、音頻信號處理等,其他可用默認值,實現FM 發射;

(3)麥克風電路模塊在射頻板上有3.5mm 接口的麥克風輸入插口,從而可以實現模擬音頻信號的輸入;

(4)音頻輸出和功放電路模塊,可以外接音箱、耳機或喇叭(右聲道)即可實現音頻的輸出。

將射頻擴展模塊開發板的各個模塊與FPGA 片上系統相應的接口相連后,就可以通過軟件下載到FPGA 片上系統上控制射頻擴展模塊,從而實現FM 射頻接收與發射、音頻播放、麥克風輸入等功能。

4 結語

本文設計了一款基于ARM 處理器的無線SoC,該系統將Arm Cortex-M0 內核移植到FPGA,能夠實現FM 廣播信號接收、FM 信號調制解調、FM 廣播信號播放、FM 信號發射(對講)、LCD 顯示頻段頻點、與上位機串口通信等功能。此外,因為FPGA 的可編程性,電路具有很強的擴展性,可以增加許多功能模塊,比如存儲頻道、手動選臺、實時以太網傳輸、實時USB 傳輸、錄音存儲等功能。