基于FPGA的高速模擬量采集系統設計

肖鵬,蔡曉樂,孫少華,趙君,閆穩

(航空工業西安航空計算技術研究所,陜西西安,710119)

0 引言

隨著航空機載系統綜合化、模塊化發展,飛機上各個系統的重要數據需要由分布在各種子系統的終端設備采集并發送給通用綜合處理設備統一管理。飛機上各子系統例如航電系統、飛控系統、機電系統、液壓系統等通常分布著大量終端數據,這些終端數據里面包括各種類型的數字信號,也包括大量的模擬信號。數字信號通過個各種總線直接和綜合處理設備進行通訊和傳輸。而模擬信號則需要轉換成數字信號后在總線上進行傳輸和處理。綜合處理設備根據這些模擬量轉換后的數字信號產生特定的控制輸出來實現各個系統不同的控制功能[1]。因此,模擬量采集功能成為機載系統中一個必不可少且至關重要的功能,其采集的精度和可靠性也影響整個機載系統運行的穩定性和可靠性。

機載系統中的模擬量包括但不限于:姿態傳感器的輸出信號(俯仰角、偏航角、俯仰角速度、滾轉角速度、偏航角速度等) 、執行機構的反饋信息(副翼舵反饋、升降舵反饋等) 、發動機轉速及溫度、電源電壓等[2]。若將這些模擬量根據信號類型進行分類,概括起來,機載系統需要采集的模擬量包括電壓信號、電流信號和電阻信號3 種類型[3]。機載系統中一般要求模擬量采集功能的精度高,并且需要采集的模擬量信號的種類和路數也很多[4]。本文針對機載系統中大量的模擬量采集要求,提出一種基于FPGA的高速模擬量采集系統設計方法。

1 系統結構及原理

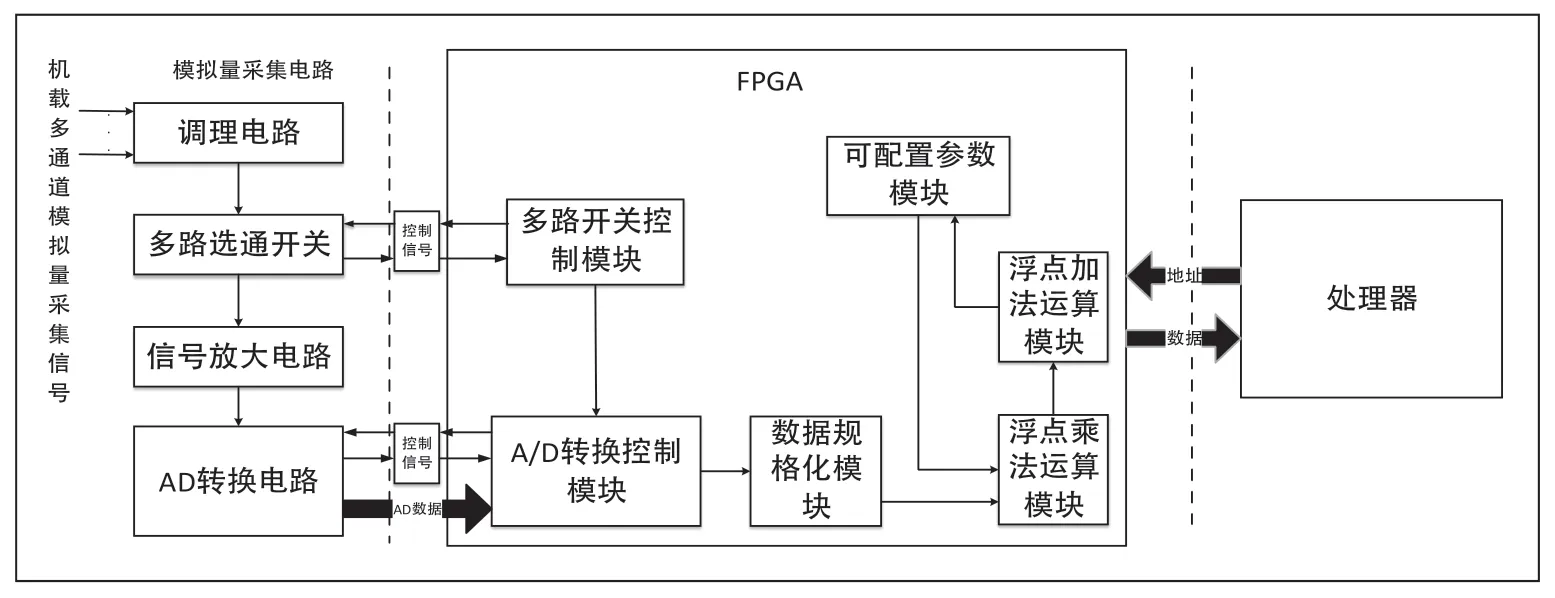

本文提出一種基于FPGA的高速模擬量采集系統設計方案,該設計總體結構圖如圖1所示,機載系統中多通道模擬信號經過分壓限幅、濾波等調理電路處理后進入多路開關電路,再經過運放跟隨、放大電路進入A/D轉換電路,其中多路開關的切換控制由FPGA 內的可編程邏輯實現,通過開關切換輪轉,A/D轉換電路最終將所有通道的數據轉換成數字信號存放在FPGA 內部相應通道的RAM 中,在FPGA 內部模擬量數據直接轉換為浮點數,處理器直接讀取數據即可。

圖1 總體結構圖

2 詳細設計

■2.1 信號調理電路

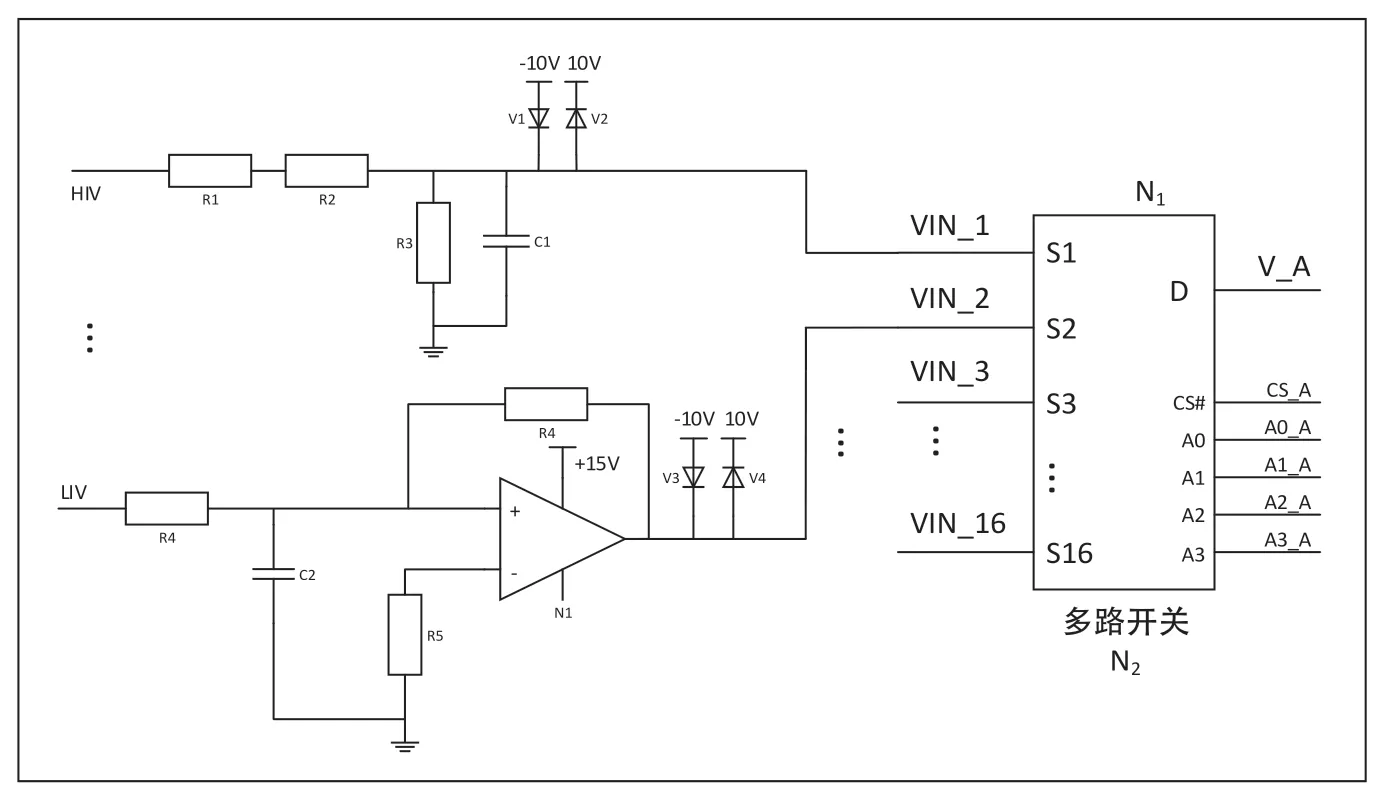

針對不同類型的模擬量信號,且機載系統中通常有大量的雜波信號,為了實現高精度采集,通過相應的調理電路將采集信號歸一化處理,常用的調理電有分壓、濾波及限幅電路。

機載系統輸入的電壓信號有-100mV~100mV,0~32V,0~115V,0~270V 等,本文設計的模擬量采集電路采集范圍為-10V~10V,因此電路調理電路前端針對不同的輸入信號,采取通過調理電路將輸入電壓控制在-10V~10V 內。

對于高電壓輸入信號,通過電阻分壓,將輸入電壓控制在采集范圍內。對于小電壓輸入信號,通過放大電路將輸入信號控制到采集范圍內。針對輸入接口的雜波信號,根據雜波信號的典型頻率,設計針對的RC 低通濾波電路。為了防止前端分壓電阻失效和輸入的瞬變大電壓造成后端電路器件的損壞,使用二極管組成限幅電路,將輸入電壓控制在采集范圍內。

機載系統中的模擬輸入數量繁多,如果采用每個通道使用一個AD 采集,會造成產品成本高,體積大,重量大,且一般也沒有一對一采集設計需求。為了提高模擬量輸入采集效率,并實現小型化、輕量化,多路開關電路可根據模擬量采集數量,PCB 面積選擇合適模擬開關電路,本文選擇16路多路開關,通過邏輯控制切換通道采集。

信號調理電路示意圖如圖2所示。

圖2 調理電路示意圖

■2.2 A/D轉換電路設計

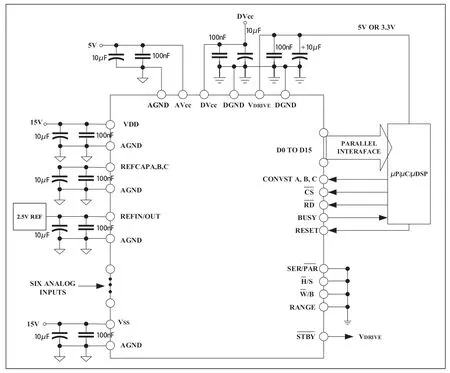

可根據采集精度、采集速度等要求選擇合適A/D轉化開關,常用的多通道A/D轉換開關有16位6 通道或者8 通道A/D轉換器。

本文選用6 通道A/D轉換器,該芯片是一種16位6 通道同步采樣的逐次逼近型A/D轉換器,具有電路集成度高、使用簡便、功耗小等特點,主要由控制邏輯、16位SAR 型A/D轉換器、基準電壓源、時鐘、緩沖器和采樣電路組合而成,模擬量輸入電壓為-10V~10V,經AD 轉換器后轉換成16位數字信號輸出,轉換時間不大于4μs。A/D轉換電路如圖3所示。

圖3 A/D轉換電路

■2.3 基于FPGA的高速模擬量采集邏輯設計

2.3.1 多路開關切換模擬量采集邏輯設計

針對多路模擬量信號采集,通過增加A/D轉換芯片個數提高通道數,會使電路非常冗余且成本太高。因此通過增加電路中的多路模擬開關提高模擬量采集通道數量,采用控制多路開關切換保證每一個模擬量輸入信號能夠被正確的采集到。

本文以16位6 通道A/D轉換芯片控制邏輯為例說明。模擬量信號均轉化為電壓信號采集,電壓信號的建立需要時間,因此切換通道后對當前通道保持一段時間后控制A/D轉換芯片啟動轉換,同時為了提高采集精度,切換到采集通道前先將多路開關輸出通道切換到“地”上,泄放掉電路中的。

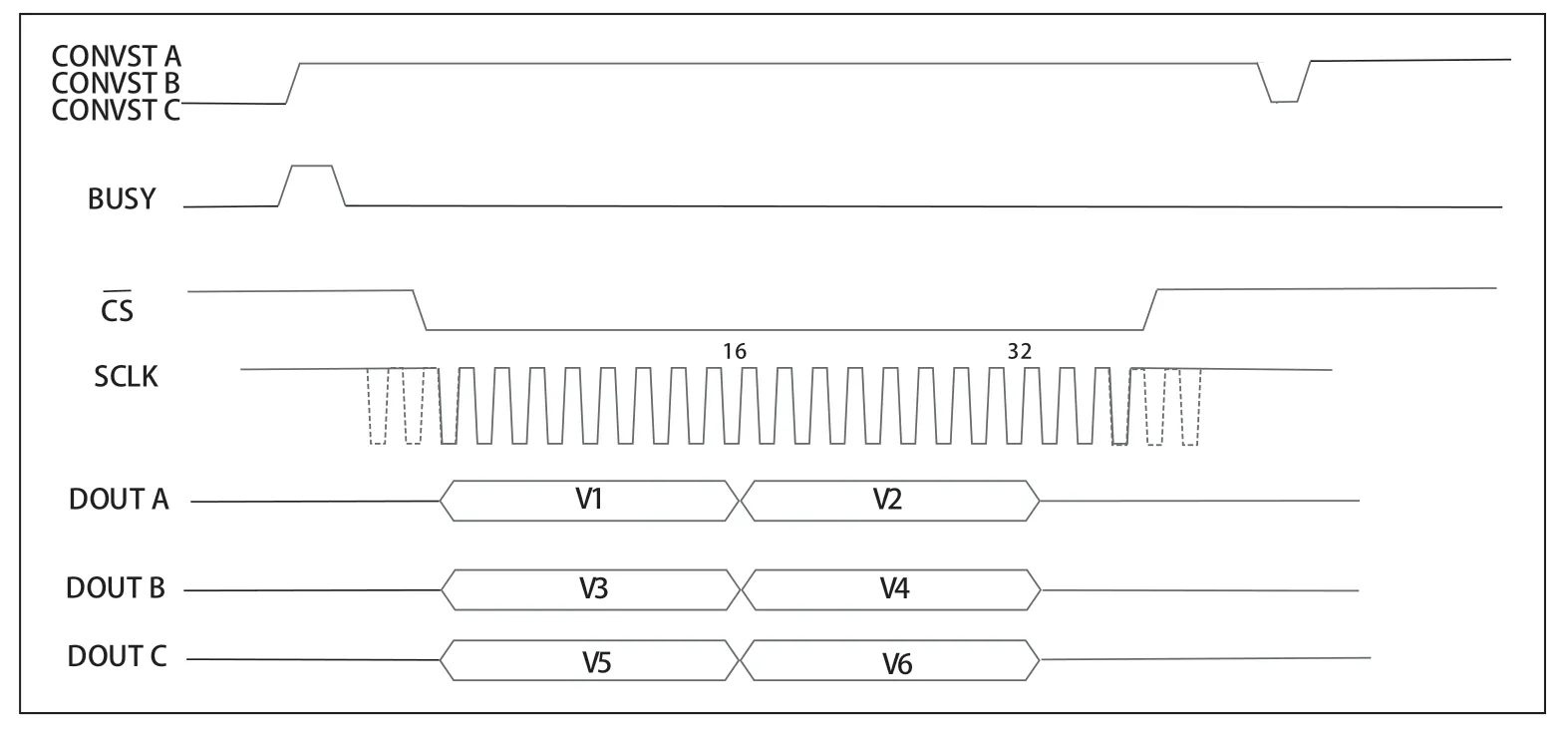

選用的16位6 通道同步采樣的逐次逼近型A/D轉換器,采集范圍為-10V~10V,線 性 誤 差 為±3LSB, 參考電壓為2.50Vdc,轉換時間3μs。當模擬量采集信號完全建立后,控制轉換控制信號CONVSTA,C O N V S T B,C O N V S T C 由低電平變為高電平,在上升沿啟動對應通道信號轉換,為保證采集信號完全轉換完成,在15μs 后控制CS 信號和RD 信號,通過并行總線將數據發送到FPGA。對于多通道模擬量采集,采集完當前輸入信號后,邏輯自動控制開關切換通道,遍歷所有輸入通道并自動更新模擬采集數據。A/D轉換器操作時序如圖4所示。

輸入輸出引腳連接示意圖如圖4所示。這里采用將兩個獨立8位狀態序列發生器SEQ1和SEQ2級聯成16狀態序列發生器SEQ,將ADCLO連接模擬地AGND,這樣連接后輸入參考電壓ADCLO=OV,在計算最后轉化結果時也不影響數據的準確性,同時防止信號零點漂移現象。

圖4 A/D轉換器操作時序

2.3.2 模擬量采集數據浮點化設計

通常FPGA 將A/D轉換后的數據以二進制數據存在寄存器中,由處理器讀取寄存器數據后按照器件手冊得出的計算公式得出最終的模擬量采集結果。本文設計在FPGA 中直接將A/D轉換數據轉換為浮點型數據,同時在FPGA 邏輯設計可配置參數模塊,直接將模擬量數據計算為十六進制的浮點數,處理器直接讀取結果后直接進行數據類型轉換即可得到十進制的浮點數,無需再進行計算。

本文設計的使用邏輯浮點運算計算模擬量采集結果數值基于16位6 通道A/D轉換器的數據采集方式基礎上設計。由于輸出的數據結果為單精度浮點數,數據總線為32位總線。

(1)A/D轉換器采集數據規格化模塊

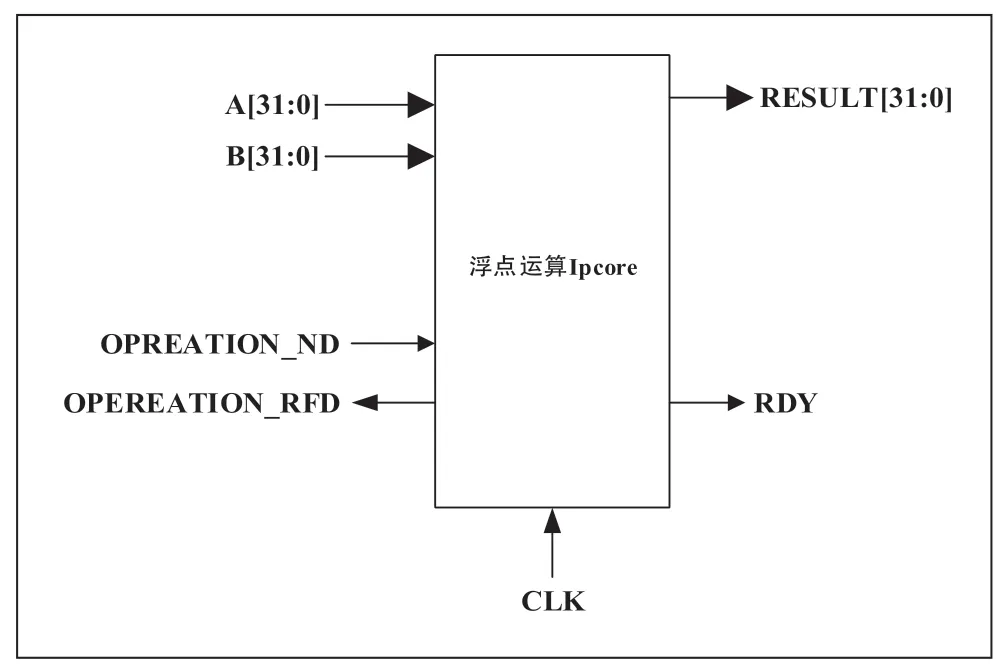

在邏輯中調用xilinx的float_point IP 核計算浮點乘法運算。IP 核的外部接口如圖5所示。A 和B 是浮點運算的兩個操作數。A 和B 必須是32 為規格化浮點數。RESULT 為A*B的結果。RDY 為高時表示數據計算完畢。OPERATION_ND 為 高 表 示IP 核 有 輸 入。OPERATION_RFD為高時表示IP 核可以接收新的操作數。

圖5 浮點運算ip 核的外部接口

A/D轉換器的采集結果計算設計思路是:將A/D轉換器的分辨率0.000305V 進行規格化的數作為操作數B,即操作數B 為常數。操作數A為A/D轉換器采集到的碼值進行規格化的數。

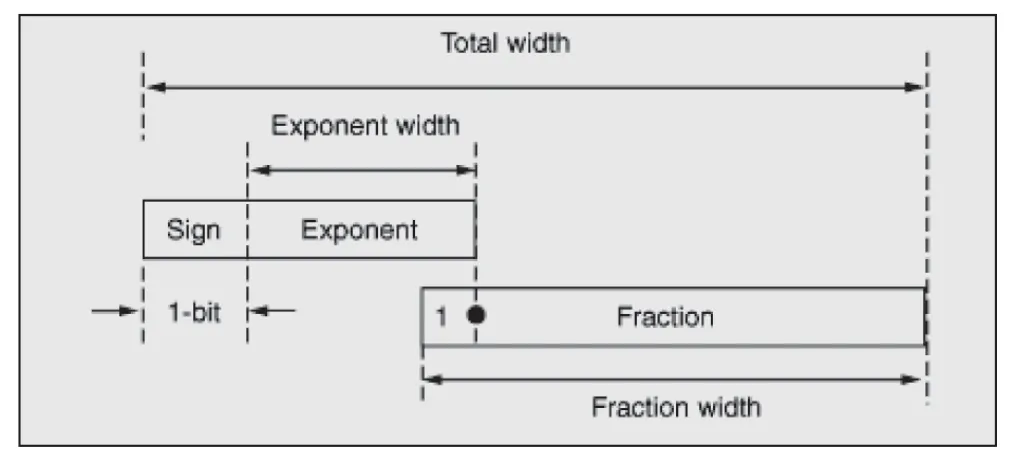

A/D轉換器采集到的數據規格化:浮點數的表示遵循IEEE754 標準,一個浮點數是由四部分組成的:符號、尾數(有效數)、指數及基。規格化的浮點數組成如圖6所示。S 為1位符號位,Exponet 為8位指數部分,Fraction 為23 為小數部分。

圖6 規格化的浮點數組成

浮點數的IEEE754 標準表達式如下式:

S 為符號位,當S=0 時,此表達式表示的是一個正值;當S=1 時,此表達式表示的是一個負值。e 是指數位,由浮點數指數部分的值決定。按照IEEE754 標準,通常浮點數的指數用移碼表示即使得e=E-bias,對單精度浮點數bias=127。1.f 表示的是尾數,尾數通常用原碼表示,且規格化后的尾數其第一位數為1(規格化的32位數據中第一位數1 不體現在碼值中,所以實際上小數部分為24位)。在邏輯中通過移位和數據拼接完成數據的規格化。

(2)可配置參數模塊

在模擬量采集系統中為了提高采集進度,通常會在軟件中對采集數據進行按照公式對采集數據進行修調,本文將修調參數設計為軟件可配置邏輯模塊,邏輯中可配置默認參數,在處理器上電初始化中對修調參數按照對應通道進行配置。

3 仿真及測試驗證

■3.1 A/D采集數據規格化仿真

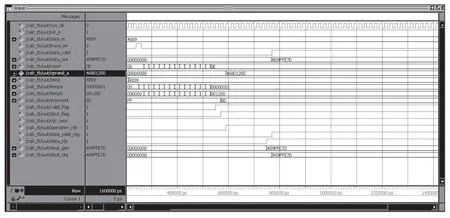

仿真激勵1:A/D轉換器采集到的電壓為5V,則轉換器輸出碼值為5/0.000305 =16393(d)=4009(h),仿真結果如圖7所示。

圖7 數據規格化模塊和數據運算仿真1

從圖7 仿真結果中看出,4009(h)進行規格化后的浮點數為46801200(h),最終計算出的模擬量結果為409FFE7D(h),轉化為十進制的結果為4.99981546402。

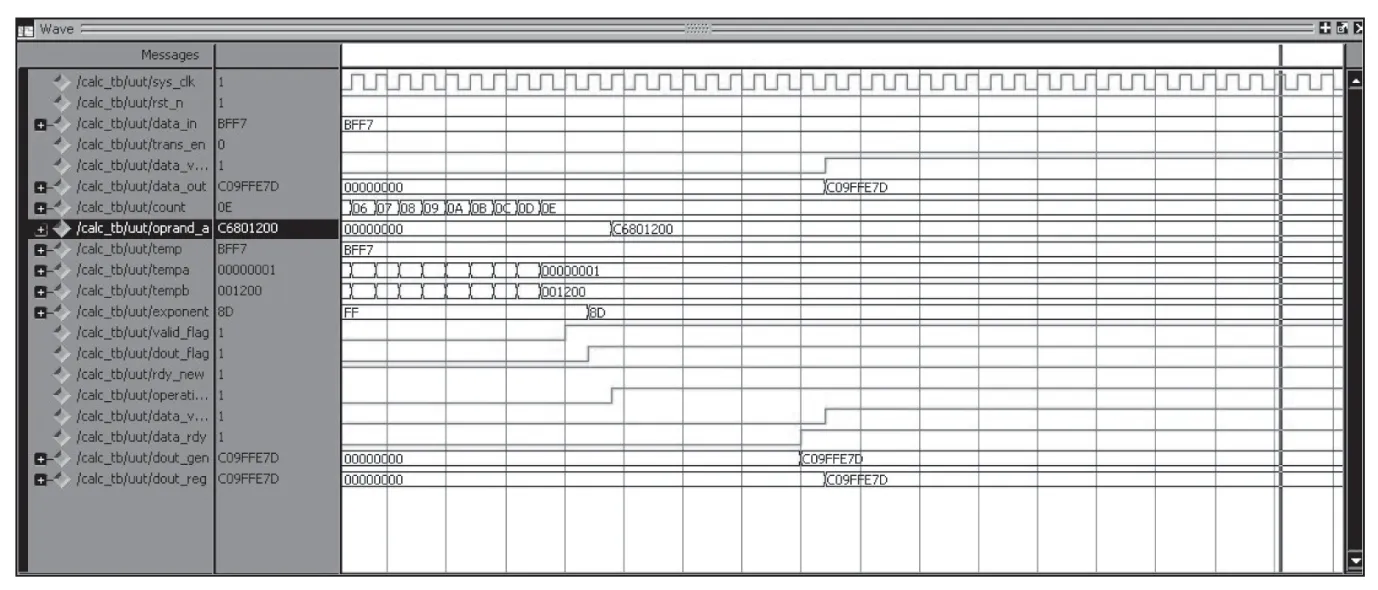

仿真激勵2:A/D轉換器采集到的電壓為-5V,則轉換器輸出碼值為-5/0.000305=-16393。A/D轉換器的輸出編碼方式為二進制補碼,-16393的補碼為BFF7。仿真結果如圖8所示。

圖8 數據規格化模塊和數據運算仿真2

從圖4 中看出BFF7(h)規格化的浮點數為C6801200(h),最終計算出的模擬量結果為C09FFE7D(h),轉換為十進制數為-4.9998156402。

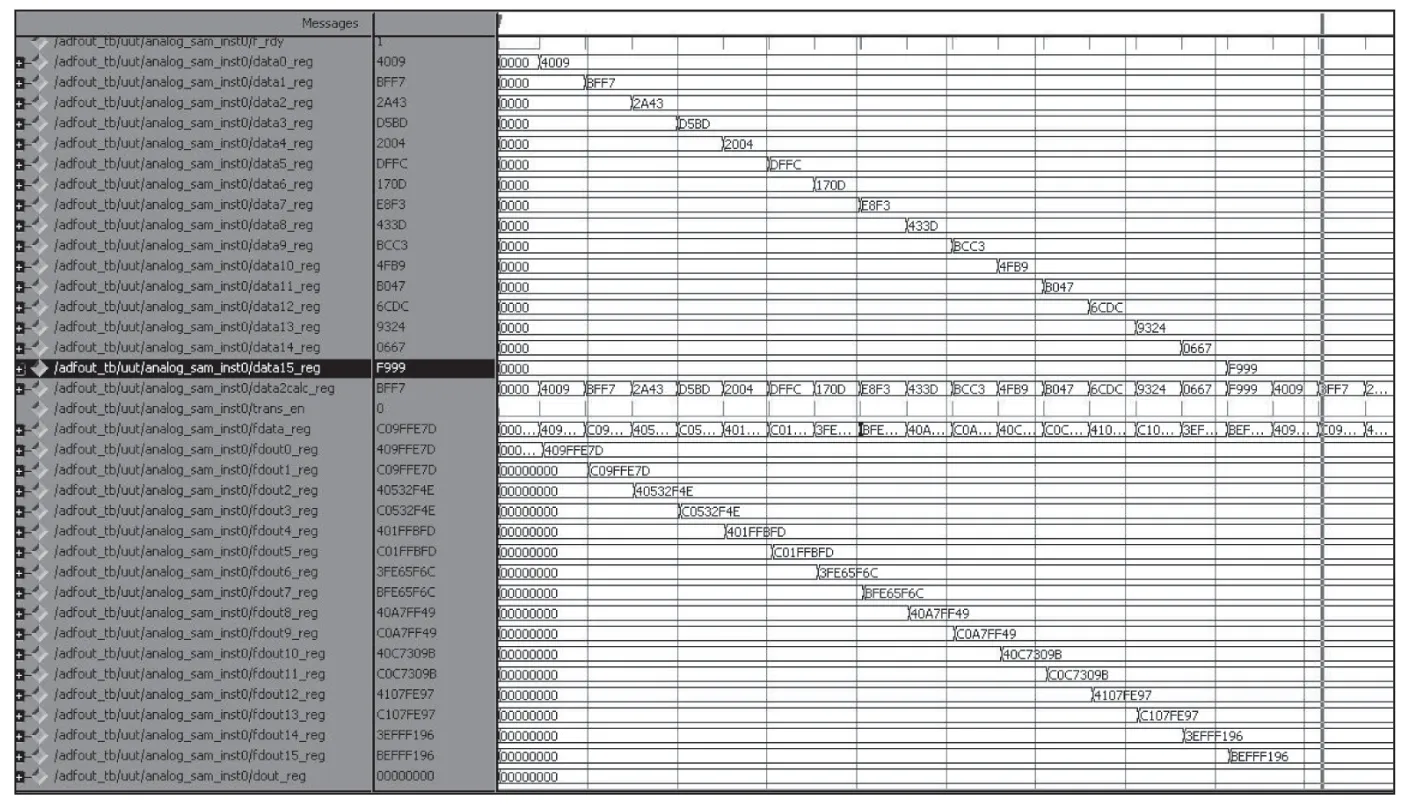

■3.2 模擬量自動采集及結果計算仿真

設計在5ms 內完成16 路模擬量采集,并在采集到數據將采集到數據計算出模擬量結果放到對應寄存器。

仿真激勵如表1所示,仿真圖如圖9所示。通過仿真得到的碼值進行計算得到采集到的值如表1所示。

表1 仿真激勵及仿真結果

■3.3 測試結果

測試內容:在外部輸入16 路模擬量激勵電壓,通過本文設計的系統電路采集,激勵電壓范圍為-10V~10V,修正參數預設(A,B)均為(1,0)。系統上電后,完成硬件初始化,FPGA 開始自動采集模擬電壓,將采集結果與給定激勵進行對比,經過多次測試,試驗抽取部分測試結果如表2所示,從表中可以看出,模擬量輸入范圍在-10V~10V 采集誤差在20mV 以內,采集精度高,同時在5ms 內即可完成采集數據的解算及上傳,實時性高。

表2 模擬量采集試驗結果

4 總結

本文基于FPGA 控制及浮點數運算技術,設計了一種機載系統多通道模擬量采集系統,設計了信號調理電路、開關電路、A/D轉換電路和FPGA 高速模擬量采集邏輯模塊,利用FPGA 采集A/D碼值并將采集結果轉化為浮點數碼值,處理讀取到數據后直接進行數據類型轉換即可得到浮點數據,同時在邏輯中設計了軟件可配置的修調參數模塊,便于對采集結果進行修調提高采集精度。經過仿真和實際測試,本設計能夠實現高速采集多路模擬量需求,同時有較高的采集精度,具備較強的工程實現意義,利用FPGA 并行采集數據的優勢,可很好的滿足多路模擬量、高實時性采集需求。

圖9 模擬量自動采集仿真圖