一種頻率注入型的快速起振晶體振蕩器

蔣徐前,陳磊,張鳴,賈曉哲

(上海電力大學 電子與信息工程學院,上海,201306)

0 引言

隨著物聯網的飛速發展,便攜式設備、傳感器節點等被廣泛應用于工農業、交通物流、生物制藥等諸多生產與生活領域中。由于這些電子系統大多采用電池供電,為了提高芯片的續航時間,減少系統的功耗,一種常見的做法是周期性的切換高低功耗的工作模式,并且系統在大多數時間是處于低功耗模式,當需要進行數據傳輸與接收時才會喚醒設備。這對集成電路設計的功耗與喚醒時間提出了更高的要求。

在芯片中,作為基準頻率源的時鐘產生電路,這類電路我們稱之為振蕩電路。其中,石英晶體振蕩電路是利用晶體的壓電效應以產生機械共振,因其具有極高的頻率穩定度而被廣泛用于頻率精度要求高的場景中。然而傳統的石英晶體振蕩器由于其高品質因子,在沒有輔助啟動電路的幫助下,常常需要幾毫秒才可以輸出穩定的頻率。而芯片內其余模塊,例如PLL、BG、LDO 等,其啟動時間往往在10μs 左右,因此晶體振蕩器的啟動時間決定了整個芯片的啟動時間以及啟動過程中消耗的能量[1]。

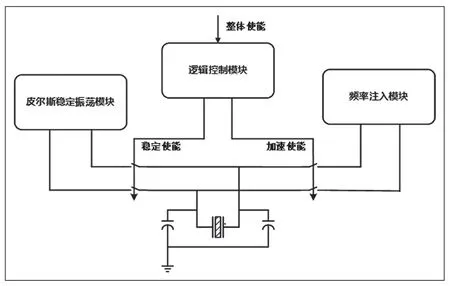

本文設計了一種頻率注入型的快速起振的皮爾斯晶體振蕩器,由邏輯控制電路、頻率注入電路、主振蕩電路以及輸出檢測電路構成。并且該電路的時序控制由內部環路自生成,無需額外的寄存器時序控制信號。由于其起振速度快,適用于低功耗及快速響應的電子系統。

1 石英晶體模型及啟動時間分析

■1.1 石英晶體模型

石英晶體的等效模型及其電抗隨頻率變化的曲線如圖1所示:低頻時,晶體呈現為容性;隨著頻率的增加,晶體逐漸接近串聯諧振點fs,此時晶體的等效串聯阻抗達到最小值;當頻率增加到串聯諧振工作點fs以上時,晶體呈現為感性,并且隨著頻率的增加,晶體逐漸趨近并聯諧振工作點fp,此時晶體相當于一個LC 并聯電路,等效阻抗達到最大;隨著頻率繼續增大,晶體在此呈現出容性。

圖1 石英晶體等效模型及電抗頻率曲線

石英晶體由于其高品質因數,其串聯諧振頻率fs與并聯諧振頻率fp十分接近,其表達式如式(1)和式(2)所示。

■1.2 振蕩器電路的起振條件

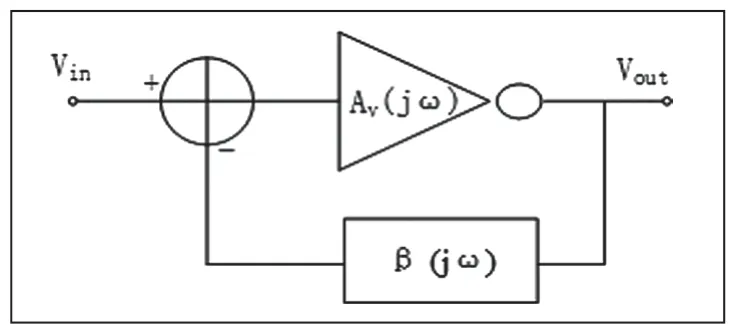

任何一個振蕩電路模塊,其模型都可以用標準反饋系統等效,其包括增益放大單元和反饋單元,反饋網絡模型如圖2所示,該反饋網絡的閉環反饋環路系統的傳遞函數如式(3)所示。

圖2 閉環反饋系統模型

圖3 快速起振晶體振蕩器系統框圖

石英晶體振蕩器要求系統為增益大于1的正反饋環路,需要滿足(1)環路增益| Av ( jw ) * β( jw)|≥ 1;(2)相位?(Av(jw) ) +?(β(jw) ) = 2nπ(其中n 為整數)。石英晶體振蕩器工作時會經歷自激放大和平衡狀態兩個過程[2]:

(1)自激放大

環路中的反相放大器會對環路中的噪聲進行放大,而高品質因數的晶體會對這些噪聲進行選頻,由此晶體環路產生了自激。這些自激的信號會通過增益模塊不斷循環放大,振蕩信號的擺幅也被逐漸放大,隨后產生電路需求的振蕩信號。

(2)平衡狀態

在自激的過沖中,增益模塊會對擺幅不斷地進行放大,并且晶體會對放大的信號選頻,所以特定頻率的信號會不斷的放大。隨后,當輸入端信號的幅度達到一個臨界值時,放大模塊會進入線性區,環路增益會變為1,此時幅度不再增長,整個電路轉而進入平衡狀態,振蕩器表現為穩幅振蕩的工作狀態。

■1.3 振蕩器電路的起振時間

忽略非線性因素帶來的影響,晶體振蕩器啟動時間表達為式(4)所示[3]:

其中CT為振蕩電路總并聯電容大小;τ= 1/α,為輸出電壓指數率增長的時間常數;i(0)為晶體的RLC 串聯支路的初始電流。

2 快速啟動電路設計

■2.1 系統框圖及分析

該方案通過邏輯控制模塊進行加速使能與穩定使能的切換:

(1)加速使能時,由RO 構成的頻率注入模塊對晶體注入能量,該頻率與晶體的本征頻率相近,因此晶體內部RLC 串聯的等效電路的電流擺幅會迅速增加,由此幫助晶體振蕩器迅速起振[4]。

(2)本設計在注入時間達到2μs 時,通過邏輯控制模塊斷開頻率注入模塊的加速使能,開啟皮爾斯振蕩器模塊的穩定振蕩使能,由于晶體的RLC 串聯支路在加速起振階段已經具備一個初始的較大電流值[5],因此皮爾斯振蕩器的輸出端的振蕩電壓信號會迅速產生。該低擺幅的振蕩信號會被中頻放大器檢測到并且通過大增益的兩級放大器放大,迅速產生晶體本征頻率的方波信號。

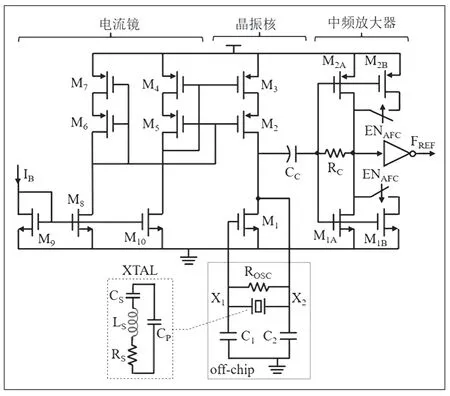

■2.2 皮爾斯振蕩電路

圖4為皮爾斯振蕩電路,其中IB為基準電流,M9與M8、M10共 同 組 成 簡 單MOS 電 流 鏡,M2、M3與M4、M5共同構成低壓的共源共柵電流鏡,該結構的高輸出阻抗更貼近理想電流源,可以為核心放大管M1提供更為穩定的電流,M6、M7柵漏短接構成二極管連接型MOS,其為低壓結構共源共柵電流鏡提供柵極偏置電壓;Cc、Rc、M2A、M1A、M2B、M1B共同構成中頻段的放大器可以有效地檢測到并放大低擺幅的振蕩信號,Cc用于隔離M1漏端的電壓直流信號,Rc、M2A、M1A重新建立輸出電壓的直流工作點,M2B、M1B在快啟時導通,增加輸出幅度。晶體XTAL 以及負載電容C1、C2均設置在芯片外部,由管腳X1、X2 接入芯片,電容C1、C2 與石英晶體XTAL 構成的選頻網絡可以對環路中特定頻率信號進行選頻進而保證輸出頻率的穩定度; 反饋電阻Rf用于建立并保持M1 管的柵漏電壓,使兩端電壓的直流值相等。

圖4 皮爾斯振蕩電路原理圖

■2.3 頻率注入模塊與時序邏輯

2.3.1 頻率注入模塊

頻率注入是通過一個環形振蕩器輸出與晶體本征頻率相近的時鐘信號,該環形振蕩器結構如圖5所示。

圖5 環形振蕩器

圖5為5 級反相延時單元組成的環形振蕩器,其單個延時單元可以產生Td的延時,其時鐘輸出周期為TRO=5*Td,輸出頻率為TRO=1/TRO=1/(5*Td),因此若要產生16MHz的時鐘頻率,可以計算出單個的延時單元需要產生125ns的延時。

2.3.2 頻率注入時序

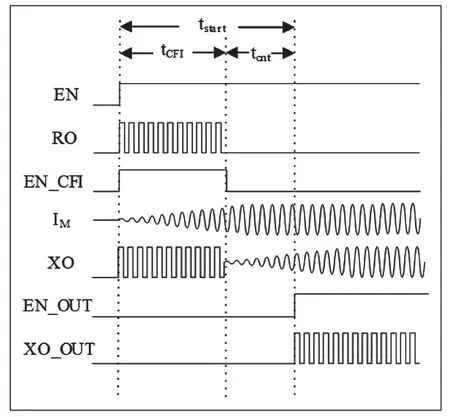

圖6為本設計的工作時序圖,EN 信號為整個系統的使能信號;RO的時鐘信號作為頻率注入的基準源,其為晶體注入本征頻率相近的振蕩信號;EN_CFI 為注入使能,用于控制RO的注入,其注入一段時間后關閉,以減少能耗;IM 和XO 分別為晶體運動支路電流以及晶體的振蕩信號;EN_OUT 用于控制晶體的時鐘輸出。本文設計的快速啟動晶體振蕩器的啟動時間為tstart=tCFI+tcnt,其中tCFI為頻率注入所用時間,tcnt為計數時間。

圖6 頻率注入型晶體振蕩器的工作時序圖

3 電路仿真驗證

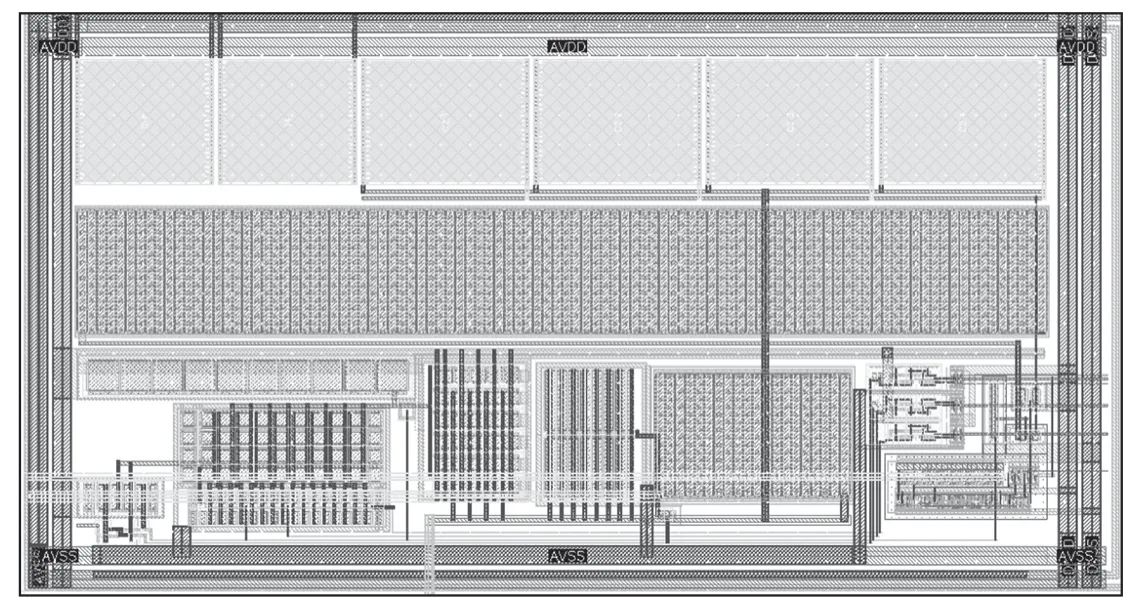

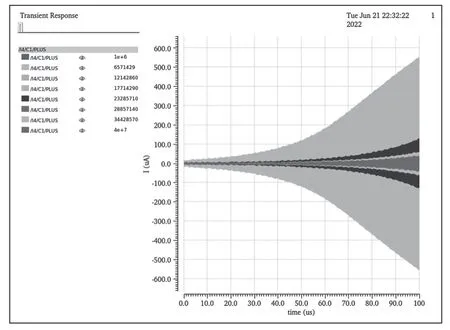

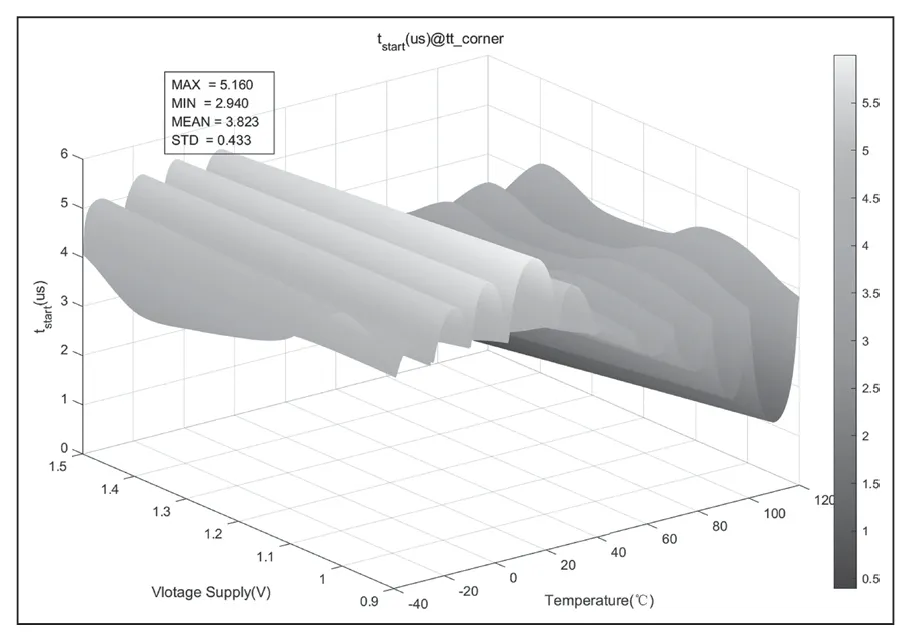

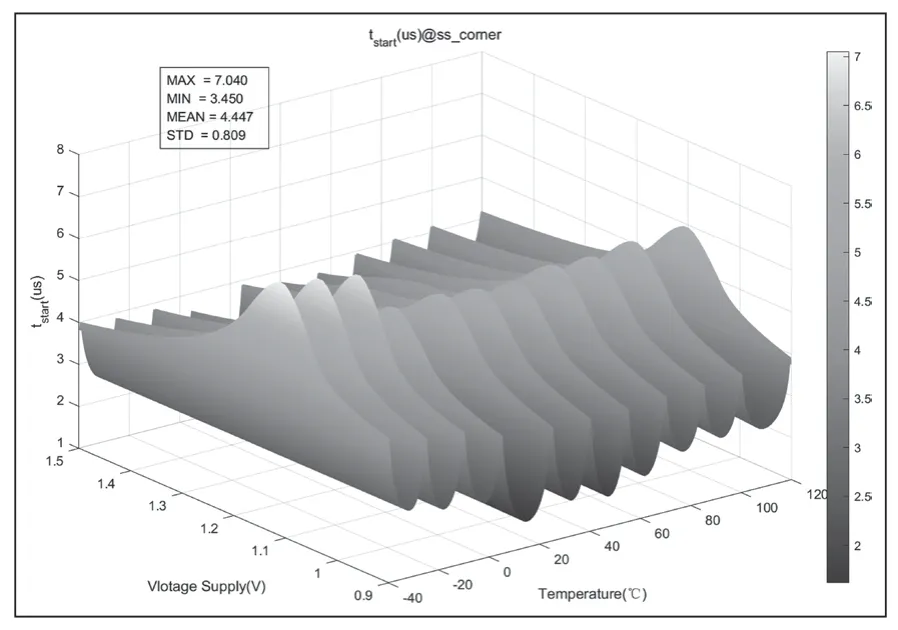

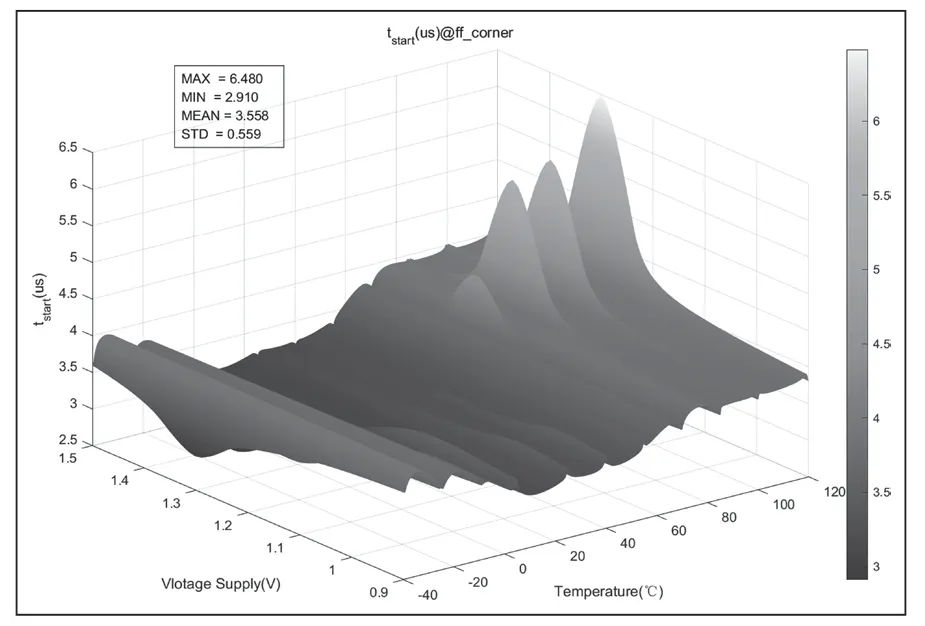

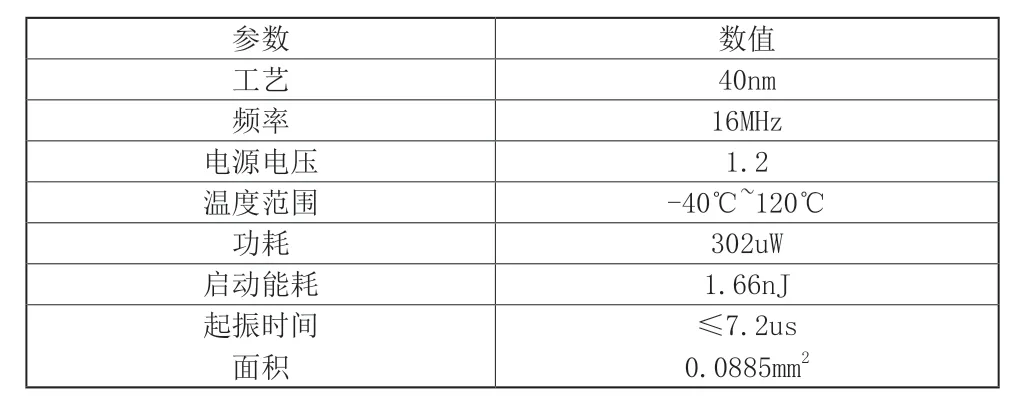

本設計的后仿真驗證結果如下,圖7 為基于頻率注入的快速起振晶體振蕩器版圖;圖8 為不同頻率注入時,晶體RLC 支路電流IM的增長速率;圖9~圖11 分別為tt、ss、ff 工藝下起振時間隨著溫度以及電源電壓變化的情況;表1 為本文快速起振振蕩器的技術指標。

圖7 基于頻率注入的快速起振晶體振蕩器版圖

圖8 不同頻率注入時,晶體RLC 支路電流IM的增長速率

圖9 tt 工藝下的起振時間

圖10 ss 工藝下的起振時間

圖11 ff 工藝下的起振時間

圖8為不同頻率方波注入時晶體的RLC 支路的電流幅度增長的情況,前文已經介紹,晶體振蕩器的起振速度與RLC 支路的初始運動電流大小呈現出正相關性。觀察圖8可知,注入的頻率與晶體的本征頻率越接近,其運動支路的電流幅度增長得越迅速。

圖9~圖11展示了在不同工藝下的該頻率注入型的快速起振晶振的起振時間隨著溫度以及電源電壓的波動情況,本設計在PVT 下總體在7.2μs 內均能完成起振。

表 1 本文快速起振振蕩器的技術指標

4 總結

該方案通過一次頻率注入的設計思路,以RO的振蕩信號對晶體進行注入從而晶體內部RLC 支路電流擺幅迅速增加。隨后通過邏輯控制單元對工作模式進行切換,當注入時間達到設定的閾值后,邏輯控制單元關閉注入加速使能,皮爾斯振蕩器開始工作,由于電流具有較大初始值,起振速度十分快;輸出級利用中頻放大器對小擺幅振蕩信號檢測并放大,產生50%占空比的方波振蕩信號。本設計最終在40nm 工藝下,-40℃~120℃的溫度范圍內,1.2V 工作電壓下,tt、ss、ff、sf、fs 各個工藝下,均可以在7.2μs 內完成起振。