基于硬件邏輯語言的簡單計時器設計

闞子楊 劉蕭鳴 趙鶴煜 涂振華 孫赫陽 姜紹君

關鍵詞:FPGA;Verilog HDL;Quartus II;計時器

中圖分類號:TP311 文獻標識碼:B

文章編號:1009-3044(2023)12-0089-03

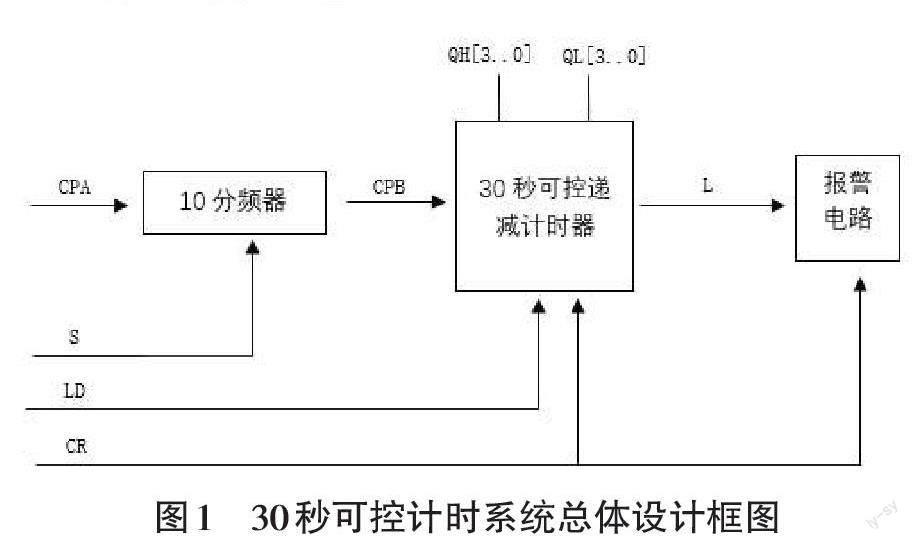

可控計時器在日常生活中有著廣泛的應用,例如交通燈信號控制,競賽倒計時,考試計時器等各個方面,如何快速準確計時,且不出現(xiàn)誤差,就需要通過精確的儀器來計時。基于FPGA的硬件邏輯編程語言實現(xiàn)計時器設計,可以準確地進行30秒的計時功能并顯示,減少人類短時計時的時間誤差。

1 設計

1.1 實現(xiàn)功能

1) 具有30秒計時,顯示功能,計時間隔為1秒。

2) 調整外部開關,控制計時器直接清零,裝數,啟動和保持(暫停)功能。

3) 計時器遞減到0時候顯示器不能滅燈,同時發(fā)出報警信號(報警燈亮起)。

4) 能夠解除警報。

5) 引腳說明:

輸入信號:時鐘CPA、直接清零CR、預置LD及減計數使能S。

輸出信號:QH[3..0]、QL[3..0](余3碼)和報警信號L。

1.2 原理

1.2.1 設計基礎

FPGA(Field Programmable Gate Array) ,完整形式是現(xiàn)場可編程邏輯門陣列,是一種電子設備,用于執(zhí)行任何(數字)邏輯功能或數字電路的硬件實現(xiàn);是在傳統(tǒng)邏輯電路和門陣列PAL、GAL,CPLD等可編程器件的基礎上進一步發(fā)展的產物[1]。FPGA最大的特點是它們是現(xiàn)場可編程的,這意味著它們在制造出來后,可以由客戶根據自己的要求在現(xiàn)場重新編程,優(yōu)點是可重復編程且低功耗。

Verilog HDL 是一種硬件描述語言,語法與C 接近,但Verilog語言是硬件設計語言,與C實質不同,用于多層次的數字系統(tǒng)建模,代碼對應硬件實體[2]。數字系統(tǒng)能夠按層次描述,并可在相同描述中顯式地進行時序建模。

Quartus,是Altera公司推出的綜合性CPLD/FPGA開發(fā)設計軟件,一種……