基于HyperLynx 的LPDDR4 信號完整性分析與優化*

劉躍成 甄國涌 儲成群 單彥虎 石建華

(1.中北大學電子測試技術國家重點實驗室 太原 030051)(2.西安子國微科技有限公司 西安 710065)

1 引言

信號完整性是指信號在傳輸過程中能夠保持穩定不受外界干擾的能力[1]。隨著DDR 的迭代發展,其數據傳輸速率在大幅度增長,根據JEDEC 發布的標準,LPDDR4 信號傳輸速率最高已經可以達到3200MT/s~4266MT/s[2]。DDR 在性能提升的同時,信號傳輸時的過沖、下沖、振鈴等信號產品完整性問題也愈發嚴重,如果在設計時不加注意,很容易造成艦船上相關電子設備的信號傳輸質量無法滿足要求,影響艦船電子設備的正常工作。通過對高速信號的仿真去分析、指導硬件電路的信號完整性設計,可以有效地解決上述問題,提高設計的可靠性[3]。因此,近些年國內外非常重視對信號完整性設計的研究。國外對信號完整性的研究起步較早,Eric Bogatin 博士在2005 年出版的信號完整性分析設計書籍至今仍在全球暢銷[4],國內的李玉山教授后來也對這本書籍進行了翻譯。三星、鎂光、英特爾等公司都具備很成熟的信號完整性設計體系,在信號完整性的研究上走在前列[5]。國內對信號完整性的研究起步較晚,華為、紫光、中興三家公司對信號完整性的研究較為成熟,在國內處于領跑地位。但總體來看,國內對信號完整性的研究設計還有待加強,不少公司還停留在依靠“經驗法則”進行布局布線設計,缺乏足夠的理論支撐[6]。

基于此,通過HyperLynx 電路仿真驗證工具,對傳輸線信號帶寬、耦合線寬、耦合間距等影響LPDDR4 信號完整性的關鍵性因素進行定量仿真分析,根據仿真結果給出提高LPDDR4 信號完整性的優化方法,有效地解決了LPDDR4 高速信號的信號完整性問題,一定程度上為LPDDR4 的應用設計提供了參考依據。

2 理論分析

信號完整性問題是多種因素復合產生的結果,由于現階段工藝水平的限制以及器件內部各種非理想因素的存在,LPDDR4 信號線在高頻狀態不可避免地會出現信號完整性問題,但其主要原因還是在于阻抗不匹配導致的信號反射和信號線間相互串擾的影響。故對反射和串擾的形成機理和影響進行理論分析。

2.1 反射

信號傳輸實際上就是信號從驅動端經傳輸線到達接收端的過程。當驅動端、接收端、傳輸線三者任意位置處出現阻抗不匹配時,就會在阻抗突變處產生局部反射,反射回去的信號和傳輸過去的信號數量由反射系數P所決定[7]。

其中Z2是信號阻抗突變后所在區域的阻抗,Z1是信號阻抗突變前所在區域的阻抗。當阻抗Z2大于Z1時,反射系數為正,信號在傳輸路徑上產生正反射,信號在阻抗突變處產生信號疊加,極限情況為接收端開路時,此時接收端阻抗無窮大時,反射系數P 值接近1,接收端電壓是入射電壓的兩倍。當阻抗Z2小于Z1時,反射系數為負,信號在傳輸路徑上產生負反射,極限情況為接收端短路時,此時接收端阻抗為0,反射系數P 值為-1,接收端電壓為0。

信號的反射會造成信號實際電壓值超過理論設定值。定義信號上升過程中第一個超過設定電壓值的峰值或者下降過程中第一個超過設定電壓值的谷值為過沖,信號上升過程中出現過沖之后的下一個谷值或者下降過程中出現過沖之后的下一個峰值稱為下沖。如果在信號上升沿或者下降沿上出現波形的非單調性,稱之為回溝。如果路徑上有多處阻抗不匹配點,那么反射的能量無法被及時吸收,就會在一個時鐘周期內反復出現電平振蕩,被稱為振鈴。過沖、下沖、回溝、振鈴都是常見的信號完整性問題[8]。

過沖、下沖、回溝、振鈴等信號完整性問題很大程度上是因為信號反射造成的,而減小信號反射的有效途徑就是使得信號驅動端、接收端、傳輸線的阻抗保持一致。信號驅動端和接收端的內部阻抗由芯片制造廠家所設計,傳輸線的特性阻抗由傳輸線線寬、介電常數、傳輸線與參考層的間距等參數所共同決定,通過調整這些參數的值可以使信號線的阻抗值維持在合適的范圍內。通常將傳輸線單端阻抗控制在50Ω左右,差分阻抗控制在100Ω左右。此外,如果傳輸線布線時存在90°以下的拐角,也會很容易導致傳輸線阻抗的改變,所以布局布線時要避免出現銳角走線。同時,信號內層走線時的通孔,信號線上的測試點,多余的線頭,都會由于信號無法繼續向前傳輸而出現Stub 效應導致信號完全反射回來[9],設計時要盡量避免。

2.2 串擾

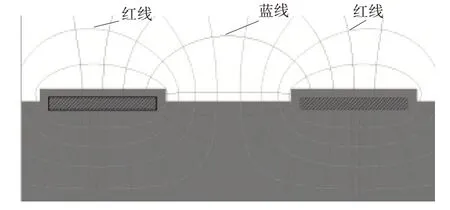

從能量場的角度講,高頻下信號線在信號傳輸時會向外輻射電場和磁場,如圖1 所示,藍色線是相鄰信號線間的電場作用的電場線,紅色線是相鄰信號線間的磁場作用的磁場線。信號線間的電場作用和磁場作用會干擾與之相鄰的信號線,這種干擾稱之為串擾,當信號線距離過近時,串擾會表現的更加明顯,對信號線的特性阻抗和傳輸速度造成影響。

圖1 串擾能量場示意圖

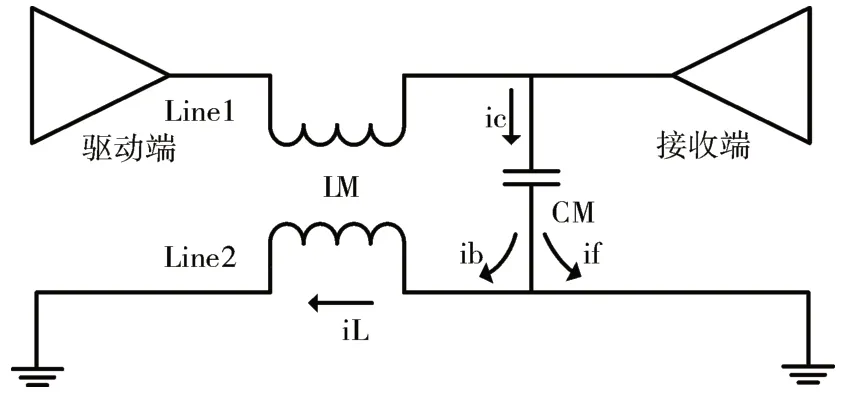

從傳輸線耦合的角度講[10],當傳輸線上有變化的電流通過時,會因為互感作用在另一條信號線上產生電壓。當傳輸線上有電壓變化時,會因為互容作用產生變化的電流。設相鄰導線間的互感系數為LM,互容系數為CM。則由互感引起的串擾電壓[11]。

由互容引起的耦合電流[11]:

如圖2 所示,當Line1 上有從驅動端到接收端的信號通過時,Line2 上由于互感作用產生向后的互感電流iL、由于互容作用產生向前的電流ib和向后的電流if。因此串擾對相鄰傳輸線的兩端都有影響,定義靠近驅動端的傳輸線受到的串擾為近端串擾,遠離驅動端的傳輸線受到的串擾為遠端串擾。

圖2 傳輸線耦合示意圖

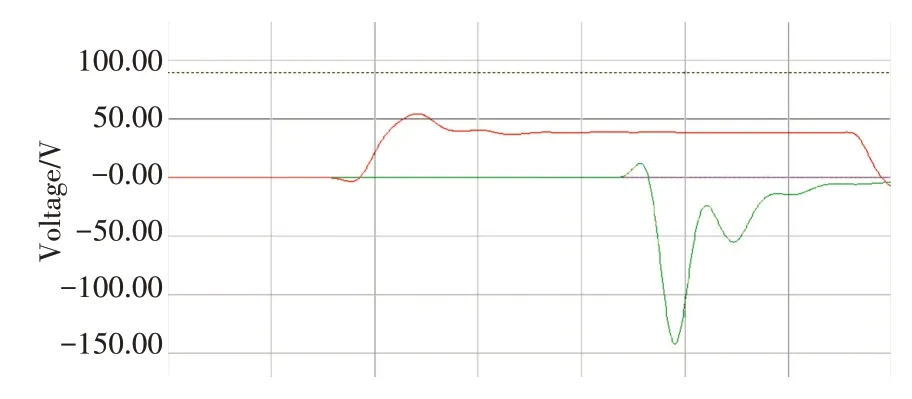

圖3 近端串擾和遠端串擾

遠端串擾的耦合電流流向與Line1電流流向相同,因此Line2 上的前向耦合電流與已經存在的前向耦合電流不斷疊加,最終表現在V/t 信號圖上為幅值較高但持續時間較短的脈沖型干擾。近端串擾的耦合電流流向與Line1 電流流向相反,其在傳輸周期內耦合電流是以恒定的速度流向近端,不會進行疊加,在信號圖上表現出幅值較低、持續時間較長的特點。

3 阻抗匹配方案設計與優化

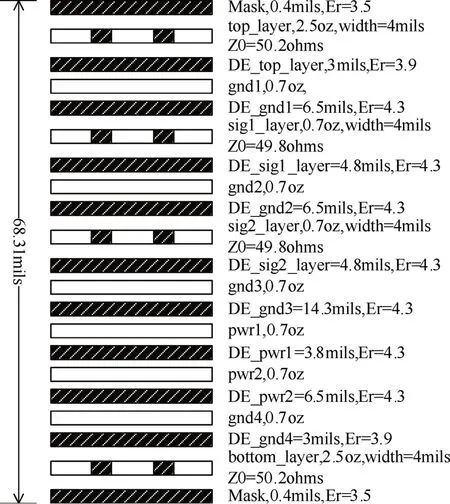

3.1 疊層設置

綜合考慮加工工藝、布局走線、阻抗控制、設計成本等因素,采用如圖4 所示PCB 疊層設計,使信號層單端走線阻抗盡量控制在50Ω左右,差分走線控制在100Ω左右,并使外層信號層有一個地層做信號返回路徑,內層信號層有兩個地層做返回路徑,以保證信號層回流路徑有完整的參考地平面,減少信號間串擾、提高信號完整性。

圖4 LPDDR4 PCB板層疊設置示意圖

3.2 阻抗匹配分析

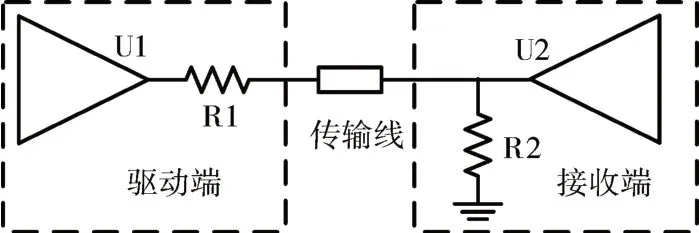

如圖5 所示為主控芯片與LPDDR4 發送數據的簡化電路圖,傳統低速信號驅動端輸出阻抗低,接收端輸入阻抗高,以使信號源的驅動電壓可以最大程度的分擔到接收端上,同時保證驅動端輸出的電流值相對較大。高速信號下為使驅動端、接收端、傳輸線的阻抗匹配,在驅動端和接收端內部集成串聯電阻R1 和并聯電阻R2,通過調節R1、R2 的阻值可以使得驅動端和接收端的阻抗值維持在與傳輸線一致的范圍內[12]。

圖5 主控芯片與LPDDR4發送數據簡化電路圖

LPDDR4 有內部40Ω、48Ω、60Ω、80Ω、120Ω、240Ω 的ODT 端接電阻可選,主控芯片有25Ω、40Ω、60Ω、75Ω、90Ω、132Ω驅動電阻可選,為找到最佳阻抗匹配值,通過控制變量法進行逐步掃描分析比較,分析如下。

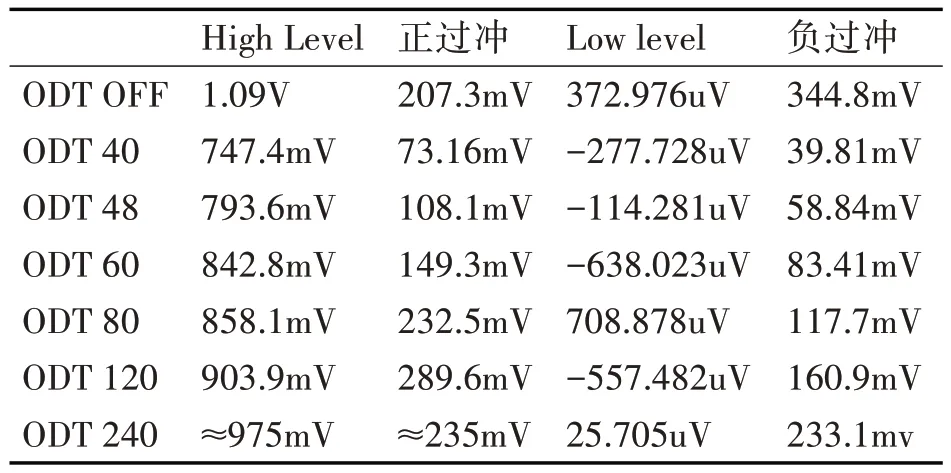

選擇主控芯片驅動電阻為25Ω,施加500MHz&50%占空比的周期激勵、掃描LPDDR4 ODT 電阻為40Ω、48Ω、60Ω、80Ω、120Ω、240Ω時SDQ20 數據線的接收信號,得到圖6 所示波形圖,根據波形圖結合表1 仿真數據關鍵參數可以看出,當ODT端接電阻為40Ω時信號質量最佳,因此可以認為,當ODT 端接電阻為40Ω時,LPDDR4 輸入阻抗與50Ω傳輸線阻抗最為接近。

表1 ODT電阻掃描波形關鍵參數表

圖6 不同ODT電阻掃描波形圖

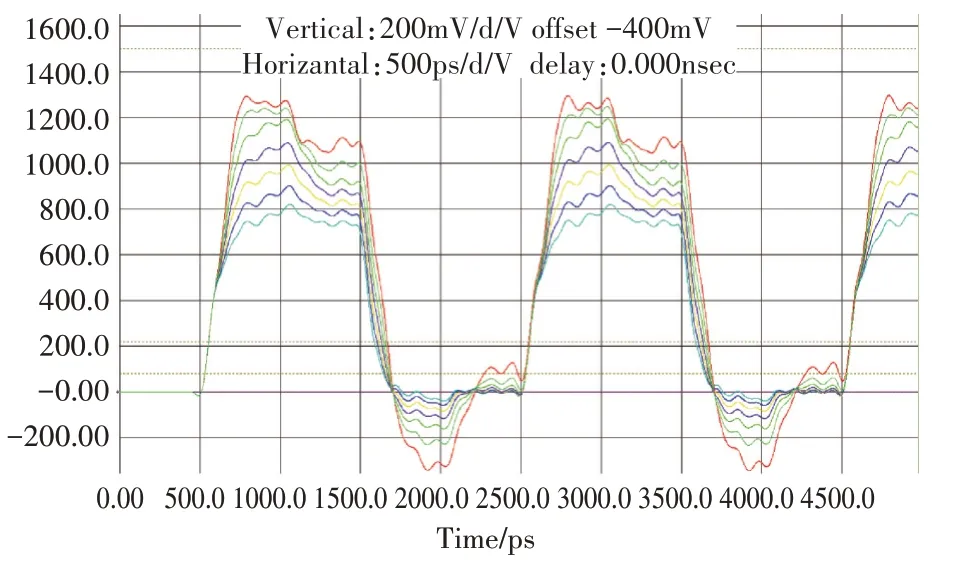

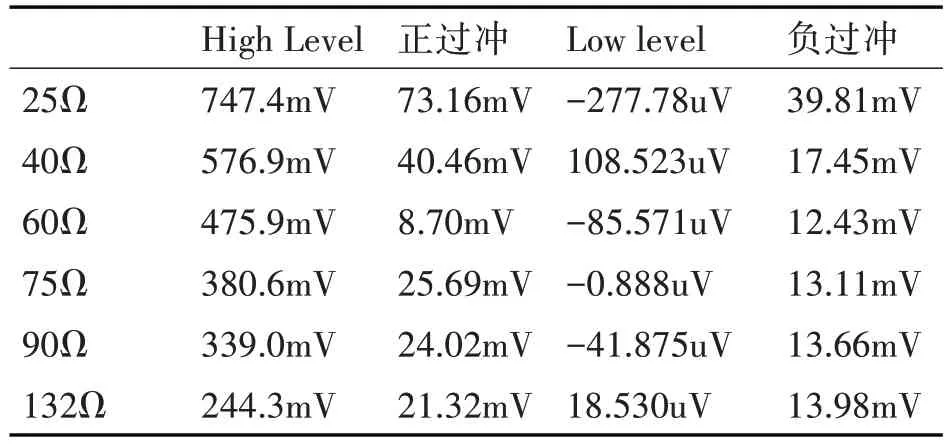

選擇LPDDR4 ODT 電阻為40Ω,施加500MHz&50%占空比的周期激勵、掃描主控芯片驅動電阻為25Ω、40Ω、60Ω、75Ω、90Ω、132Ω時SDQ20 數據線的接收信號,得到圖7所示波形圖。

表2 驅動電阻掃描波形關鍵參數表

由2.1節的理論分析可知,當信號發送端、傳輸線、信號接收端三者中有兩者阻抗匹配時,就可以很大程度地減少信號反射、所以在LPDDR4 ODT電阻為40 歐姆時,主控芯片端接驅動電阻在40Ω、60Ω、75Ω、90Ω、132Ω時SDQ20 數據線的接收信號波形均相對較好,但端接驅動電阻會分走一部分電壓使得LPDDR4 信號接收端High level 值降低,且阻值越大,分走的電壓越多,而過低的High level值會導致“0”和“1”的電平信號不明確,容易造成電平誤判。

綜合考慮以上因素,LPDDR4 ODT 電阻選擇40Ω、主控芯片端接驅動電阻選擇40Ω或者60Ω屬于比較理想的阻抗匹配方案。

4 傳輸線仿真與設計優化

4.1 不同傳輸線間距仿真分析

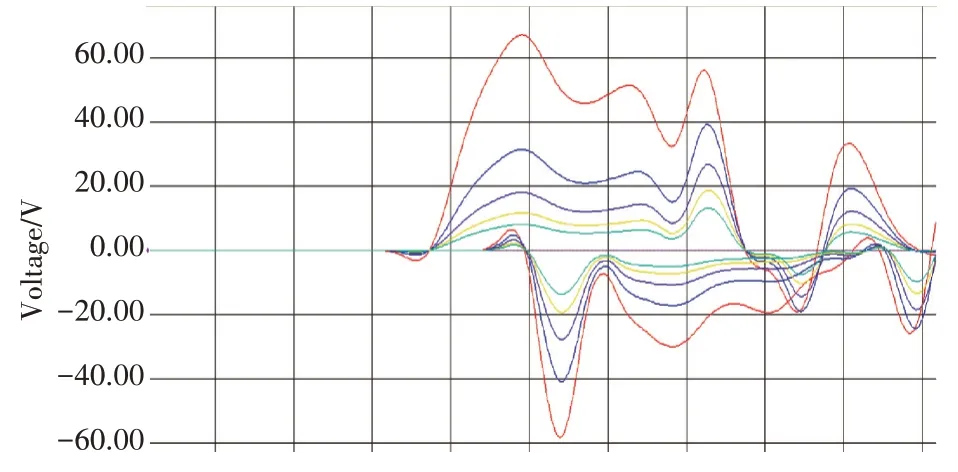

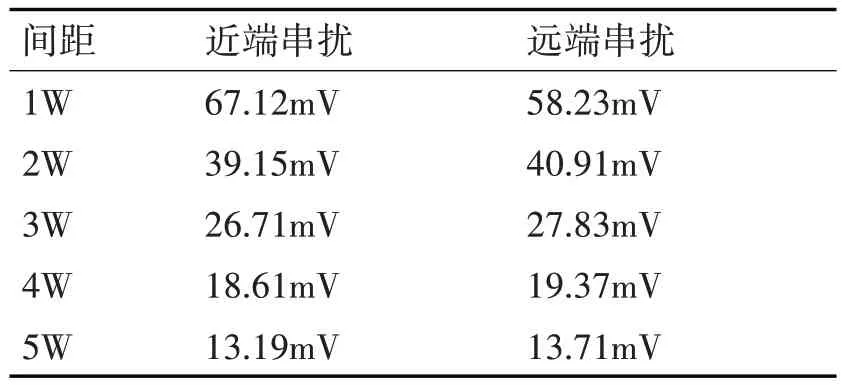

仿真設置:選取TOP 層相鄰傳輸線SDQ1、SDQ2 進行仿真分析、耦合線長取1000mil、傳輸線線寬4mil、TOP 層阻抗50.2ohms、主控芯片驅動電阻選取40Ω、LPDDR4 ODT 電阻選取40Ω,線間距選取1W、2W、3W、4W、5W(W為傳輸線線寬)。

圖8 不同傳輸線間距掃描波形圖

表3 不同傳輸線間距下的近端串擾和遠端串擾

可以看出,串擾值隨著傳輸線間距越大而逐漸越小,增大傳輸線間距可以極大程度減小串擾的影響,這是因為傳輸線間距增大以后傳輸線的互感值減小,串擾也隨之減小,所以傳輸線間距需要盡可能保持在3倍線寬以上。

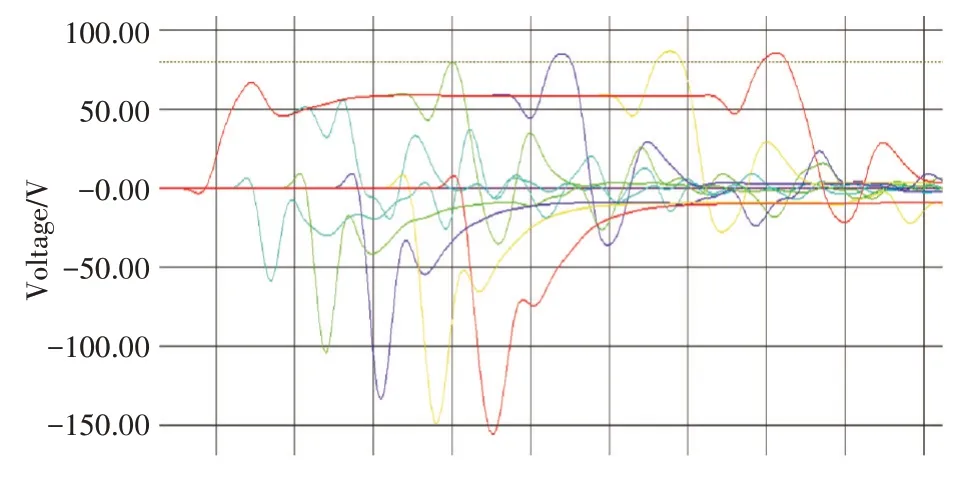

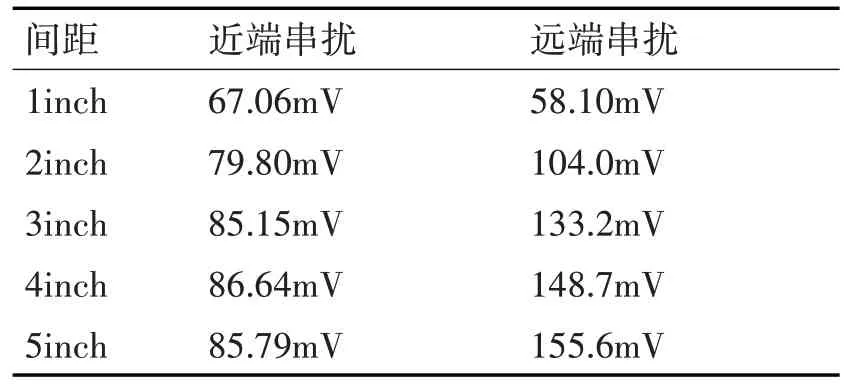

4.2 不同耦合長度仿真分析

仿真設置:選取TOP 層相鄰傳輸線SDQ1、SDQ2 進行仿真分析、傳輸線線寬4mil、傳輸線間距4mil、TOP 層阻抗50.2ohms、主控芯片驅動電阻選取40Ω、LPDDR4 ODT 電阻選取40Ω,耦合長度選取1inch、2inch、3inch、4inch、5inch。

圖9 不同耦合長度掃描波形圖

表4 不同耦合長度下近端串擾和遠端串擾

可以看出,近端串擾值受耦合長度的影響不大,但近端串擾的持續時間會隨著耦合長度的增加而增加。遠端串擾值受耦合長度影響較大,隨著耦合長度增加,遠端串擾值逐漸加大,尤其在1inch到3inch中,串擾影響表現的更加顯著。

4.3 不同傳輸速率仿真分析

仿真設置:選取SDQ20 傳輸線進行仿真分析、傳輸線線寬4mil、TOP 層阻抗50.2ohms、SIG1層阻抗49.8ohms、主控芯片驅動電阻選取40Ω、LPDDR4 ODT 電阻選取40Ω。激勵選擇PRBS(Pseudo Random Binary Sequence)偽隨機二進制序列,傳輸線傳輸速率選擇1Gbps、2Gbps、3Gbps、4Gbps、5Gbps。

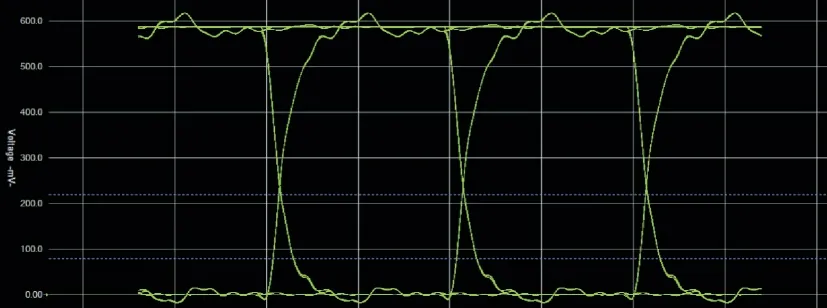

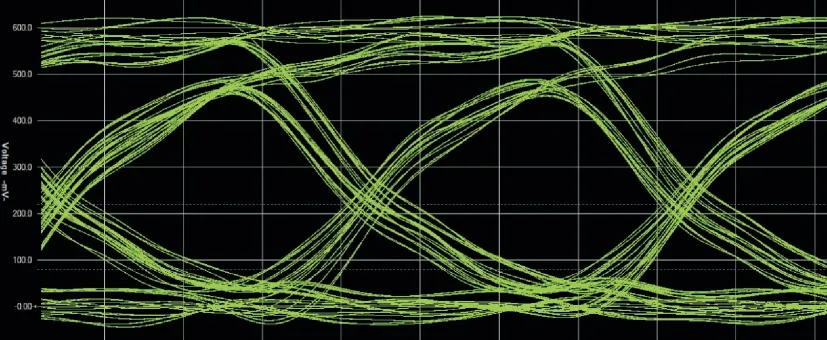

圖10 所示為傳輸速率1Gbps 時SDQ20 傳輸線的眼圖,其眼寬958.750ps,眼高578.2mV,平均高電平值592.7mV,正過沖24.98mV,平均低電平值487.889μV,負過沖17.85mV。

圖10 1Gbps速率下SDQ20信號線眼圖

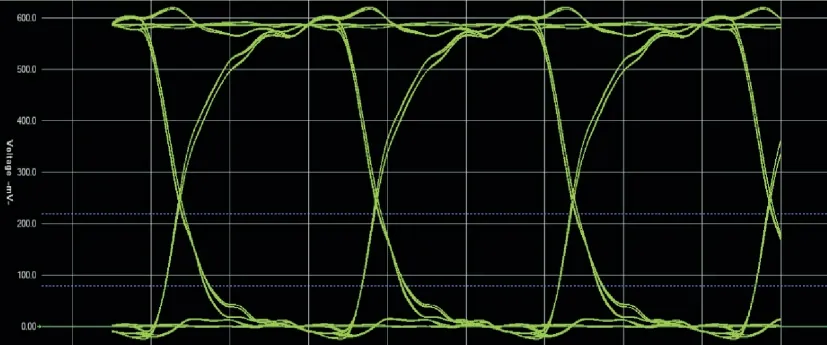

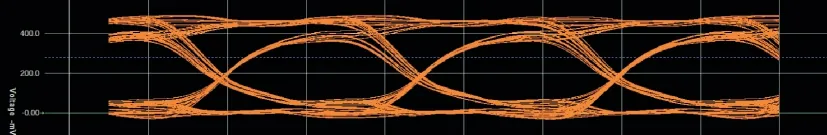

圖11 所示為傳輸速率2Gbps 時SDQ20 傳輸線的眼圖,其眼寬468.226ps,眼高551.3mV,平均高電平值573.6mV,正過沖48.00mV,平均低電平值4.01mV,負過沖28.71mV。

圖11 2Gbps速率下SDQ20信號線眼圖

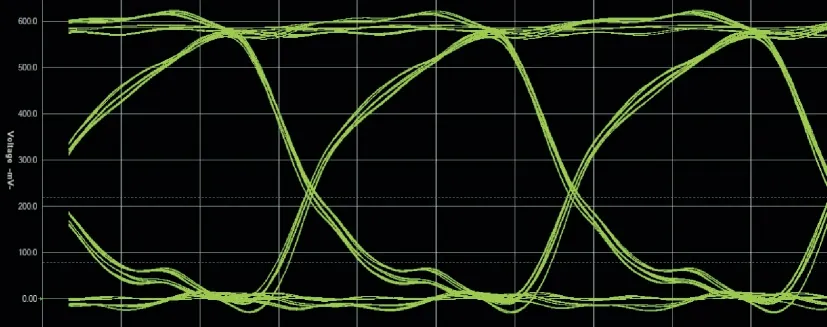

圖12 所示為傳輸線傳輸速率3Gbps 時SDQ20傳輸線的眼圖,其眼寬287.958ps,眼高458.3mV。平均高電平值562.4mV,正過沖61.37mV,平均低電平值19.43mV,負過沖50.46mV。

圖12 3Gbps速率下SDQ20信號線眼圖

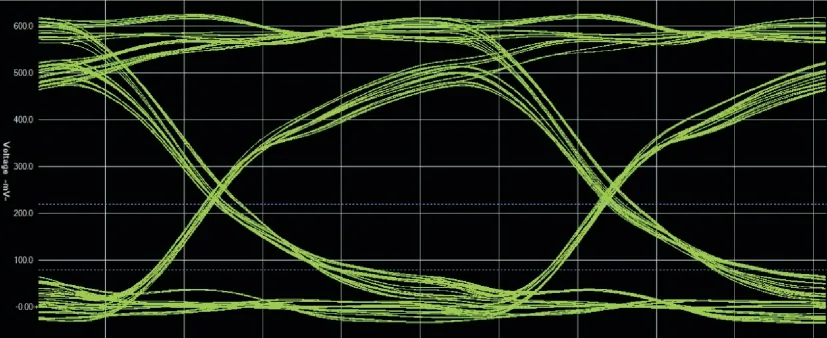

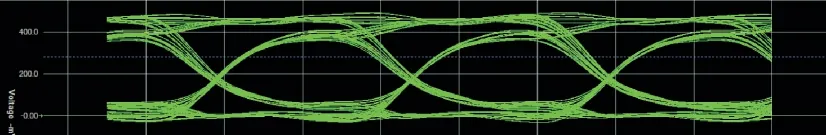

圖13 所示為傳輸線傳輸速率4Gbps 時SDQ20傳輸線的眼圖,其眼寬218.332ps,眼高377.4mV,平均高電平值535.5mV,正過沖90.30mV,平均低電平值19.53mV,負過沖54.38mV。

圖13 4Gbps速率下SDQ20信號線眼圖

圖14 所示為傳輸速率5Gbps 時SDQ20 傳輸線的眼圖,其眼寬138.797ps,眼高361.1mV,平均高電平值520.9mV,正過沖104.7mV,平均低電平值27.21mV,負過沖70.93mV。

圖14 5Gbps速率下SDQ20信號線眼圖

可以看出,隨著傳輸速率增大,眼圖厚度逐漸變厚,眼寬逐漸變窄、眼高逐漸變低、信號裕量逐漸減少、噪聲逐漸增大;但因為滿足阻抗匹配的要求,所以5Gbps 傳輸速率下眼圖仍有一定張開幅度,仍具有比較不錯的信號質量。

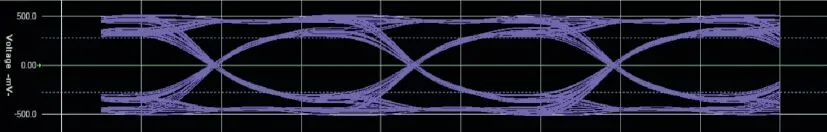

4.4 差分時鐘信號仿真分析

仿真設置:選取SDQS2_P、SDQS2_N 差分時鐘信號進行仿真分析、差分線線寬4mil、差分線間距4mil、TOP 層單端阻抗50.2ohms、SIG1 層單端阻抗49.8ohms、主控芯片驅動電阻選取60Ω、LPDDR4 ODT 電阻選取40Ω。激勵選擇PRBS(Pseudo Random Binary Sequence)偽隨機二進制序列,信號傳輸速率選擇4Gbps。

圖15 4Gbps速率下SDQS2_P信號線眼圖

圖16 4Gbps速率下SDQS2_N信號線眼圖

圖17 4Gbps速率下SDQS2_P&SDQS2_N差分信號線眼圖

在4Gbps 速率下、SDQS2_P 信號線眼寬204.039ps、眼高290.5mV;SDQS2_N 信號線眼寬207.208ps、眼高281.0mV;而其差分信號眼寬237.243ps、眼寬575.7mV。差分信號的眼寬、眼高相比單端信號均有提高,同時,差分時鐘信號眼圖開合較為工整、波形比較光滑,上升沿、下降沿均無回溝現象。可見,差分信號的確可以提升信號的抗干擾能力。

5 結語

文章對反射、串擾的形成機理進行理論分析,通過合理設置層疊參數將LPDDR4 信號線單端阻抗維持在50Ω左右,差分線阻抗維持在100Ω左右,并通過控制變量與參數掃描結合的方法,得到主控芯片與LPDDR4 的理想阻抗匹配方案,極大程度地減少了LPDDR4 的信號反射問題,在此基礎上,對影響LPDDR4 信號完整性的關鍵性因素如傳輸線信號帶寬、耦合線寬、耦合間距等進行定量仿真分析,使得部分傳統的PCB 經驗布線規則在LPDDR4設計上有了明確的分析量化,如3W 布線定則,設計者可以明確通過評估1W、2W、3W、4W、5W 的串擾值來確定走線間距,一定程度上為LPDDR4 的應用設計提供了參考依據。文章的研究思路也能為其他類型的DDR 及高速信號設計提供參考。由于時間關系加上水平有限,文章還有許多沒有分析考慮的因素,比如過孔處的阻抗突變[13],信號的碼間干擾以及電源完整性問題等,仍有進一步的優化改進空間。