雙重圖形拆分技術應用及國產化研究

付 靜

(上海國微芯集成電路有限公司,上海)

引言

長期以來,半導體技術一直遵循摩爾定律,即每18 個月,集成電路芯片晶體管密度翻倍,即:半導體工藝技術節點的關鍵尺寸(Critical Dimension),將以每18 個月,縮小至上一節點的70%左右。比如主流半導體制造商(包括Intel、三星和格羅方德等)的工藝節點,經歷了180 nm、130 nm、90 nm、65 nm、45/40 nm、32/28 nm、20/22 nm 到14 nm 這一系列的高速發展過程[1]。隨著工藝關鍵尺寸縮小,工藝挑戰越來越大。主流的193 nm ArF 浸潤式光刻機已無法直接曝光生產14 nm 工藝中的芯片最小圖形尺寸。半導體制造商引入了自對準雙重圖形化技術(SADP,Self-Aligned Double Patterning)和雙重圖形拆分技術(DPT)來解決該問題;其中DPT 需要EDA 軟件和工藝的完美結合,幫助14 nm 工藝制程順利實現。

1 項目背景

近年來,因國際形勢變化,美國、歐洲和日本等國逐漸加大對中國先進集成電路產業的限制,我國先進半導體技術路線也向雙重或多重圖形拆分技術偏移,以最大化利用深紫外(DUV)光刻機潛力。半導體核心技術的國產化,是破局國外技術禁運的關鍵。半導體制造設備及材料、EDA 是半導體產業鏈上游的三大方向;而DPT 是制造端EDA 的一個細分方向,也是14 nm 等先進工藝必備一環。因此,DPT 軟件國產化至關重要。

2 雙重圖形拆分技術應用及國產化

14 nm 節點的關鍵版圖層使用當前較為先進的深紫外(DUV)193 nm ArF 浸潤式光刻機曝光。基于瑞利判據公式,其分辨率理論極限值在33.6 nm 的半周期(Half Pitch)[3]。實際應用中會略大,特征的全周期(Pitch)分辨率在72 nm 以上。

其中,k1為系統參數,λ 為光源波長,NA 為數值孔徑[3]。

Intel 的14 nm 節點利用DUV 光刻機,可提供鰭層(Fin)全周期42 nm、關鍵金屬層(Metal)52 nm 分辨率的工藝支持[4]。這首先歸功于SADP 和DPT 的應用。工藝中利用SADP 技術,即側墻生成工藝來輔助生成規則圖形,比如鰭層(Fin);對于關鍵金屬層,則利用DPT 技術在軟件層面將單層金屬版圖拆分成兩層,通過兩次光刻工藝來實現更高分辨率。

DPT 軟件有兩大應用場景:

(1)用于14 nm 及更先進節點芯片設計的物理驗證,負責檢查該芯片設計是否滿足雙重圖形拆分硬性要求,圖1 展示了一個奇數環,它表示該處無法滿足硬性規則進行拆分。

圖1 奇數環Odd Loop

(2)芯片制造企業對版圖層進行拆分,既要對違反光刻極限的圖形拆分,也需對工藝不友好區域拆分。

2.1 雙重圖形拆分(DPT)軟件架構與功能開發

2.1.1 嚴格規則拆分檢查和違例反標

嚴格的拆分規則是芯片制造商(Foundry)定義的設計規則(DRC),通常認為滿足一定條件(例如間距<50 nm)區域,必須可被拆分到兩張版圖;否則,這是一個奇數環違例[2]。對于需進行雙重圖形拆分的芯片設計,在芯片物理設計的放置(Place)和繞線(Route)階段,會考慮雙重圖形拆分的嚴格規則;但還無法完全避免奇數環違例發生,這就需要在芯片物理驗證階段,引入雙重圖形拆分軟件中的嚴格規則拆分檢查和違例反標功能。該功能將違例區域反標回芯片原始設計。圖2 為一個奇數環違例,芯片設計工程師可通過繞線(Route)合理修正來規避。

圖2 雙重圖形拆分違例及修正

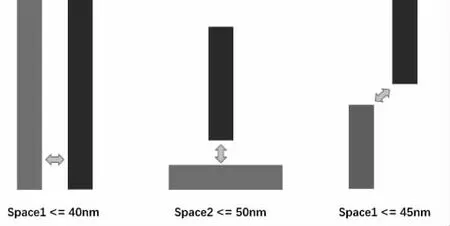

2.1.2 嚴格規則拆分和工藝友好規則拆分

芯片制造商(Foundry)最為看重雙重圖形拆分軟件的拆分功能。在14 nm 等工藝中,foundry 會將需使用雙重光刻工藝(常見為LELE)的版圖層,按一定規則拆分成兩張光掩膜。此規則包含嚴格規則和后續工藝友好規則,這些規則主要與圖形間距、形狀有關。DPT 軟件進行拆分時,首先必須確保滿足嚴格規則條件的區域可被拆分。例如,常見的嚴格規則會包括以下三種[2],見圖3。滿足以下條件的圖形,必須被拆分到兩張不同圖層。

圖3 基于嚴格規則的拆分

除了嚴格規則,foundry 有一整套基于自身工藝特點的工藝友好拆分規則。這些規則通常比嚴格規則寬松,但需要DPT 軟件能夠盡可能多的去實現工藝友好規則拆分。圖4 是針對通孔層(Via)的兩組拆分結果,雖然均滿足最嚴格的規則,但左邊一組實現了應拆盡拆原則,對后續工藝更為友好。

圖4 兩組不同的拆分結果

2.2 雙重圖形拆分(DPT)軟件實際應用與驗證

完成雙重圖形拆分后,版圖層將用EDA 軟件進行光學臨近效應修正(OPC),然后版圖信息會被制造到兩張光掩膜(Mask)。相關工程師會通過OPC 軟件進行光刻工藝仿真,通過結果統計分析,評估雙重圖形拆分結果。DPT 軟件能夠盡可能高的覆蓋并實現工藝友好規則的拆分,后續光刻工藝仿真檢查到的不理想壞點(hotspot)則越少,最終良率越高。

芯片制造企業會通過DPT 軟件拆分技術,來修正不理想的壞點。將壞點幾何環境特征寫入拆分規則,可在更早步驟中,較為徹底的避免該類問題,在實際中也獲得了驗證。例如,對于通孔層(Via)某些冗余Via 帶來的拆分不理想區域,芯片制造商通常會考慮對局部冗余Via 做一定變化,并寫入拆分規則,來解決該問題[5]。

3 難點問題與技術措施

3.1 拆分算法中引入工藝友好軟規則

例如,嚴格拆分規則為邊(Line)與邊(Line)間距<=40 nm、邊(Line)與線端(Line end)間距<=50 nm、線端與線端(有投影重合)間距<=55 nm、點與點間距<=45 nm;工藝友好軟規則見表1;其中優先級1 表示拆分優先度最高,優先級3 表示拆分優先度較低。

表1 工藝友好規則示例

軟規則拆分需要在嚴格拆分規則基礎上再做計算求解。拆分軟件應先確保嚴格拆分完成后,再根據優先級進行軟規則拆分。軟規則拆分時,需引入虛擬奇數環用于后續調整。虛擬奇數環是建立在軟規則基礎上的虛擬拆分違例,這類虛擬拆分違例在滿足預設激發條件時,可對嚴格規則拆分結果重新著色,保證軟規則拆分覆蓋率。

3.2 內存和性能問題

超大規模求解圖形著色問題的計算將會對硬件資源造成極大沖擊,運算量極為巨大。在14 nm 節點的芯片設計中,一個版圖層包含多邊形數量超過十億,更先進節點的大尺寸芯片,數量甚至為百億級。DPT 軟件拆分求解時,內存使用峰值超過2T,運行時間會超過上百小時。

解決內存消耗和計算量問題,將從兩個方面出發:

(1)拆分算法優化。由于軟規則帶來了更多拆分限制,算法工程師需針對該問題進行更多的優化嘗試。

(2)DPT 軟件充分利用分布式運算模式。傳統求解方法是將數據放在內存中利用多線程求解,但單臺服務器內存及計算資源有限。通過對計算任務合理切分(Partition)及分發,利用分布式服務器加速計算,為目前主流EDA 軟件發展趨勢之一。

4 技術創新分析

DPT 軟件開發過程中面臨的諸多瓶頸,需要技術創新加以解決;而按照傳統技術方向,需長時間的開發周期和技術積累,例如西門子EDA(Mentor Graphics)在層次化(Hierarchy)方向技術積累長達20年。

通常DPT 軟件在做拆分求解時,難以充分利用分布式服務器,原因是拆分的求解需考慮全局數據才能給出最優解,局部拆分結果并不完全準確。然而,利用局部結果并引入新算法拆分校正,可迅速生成合理的拆分求解。該算法對于降低內存和運算時間有顯著幫助。

局部數據切分(Partition)方式也直接影響了DPT軟件性能。結合芯片設計特點,采取模塊抽取及一維切分方式,可大幅降低后續模塊計算壓力。此切分方式示例見圖5。

圖5 模塊抽取及一維切分

結束語

基于工業界的實際應用,DPT 技術架構和功能經過了嚴謹論證、詳細布局與高質量驗證,最終產品可解決先進半導體工藝對雙重圖形拆分需求,同時也打破了國外在該細分領域對國內的限制。DPT 對于MPT技術開發的算法、內存管理方面也有許多啟示。