一種搭載FPGA 和AD9361 的軟件無線電平臺實現方法

禹永植,夏澤宇,劉宇

哈爾濱工程大學 信息與通信工程學院,黑龍江 哈爾濱 150001

隨著電子技術的快速發展,無線通信技術也得到了不斷的發展和進步,人們對無線通信的要求也來越高。傳統射頻收發器硬件架構使用低噪聲功率放大器、混頻器、可變增益放大器、數模/模數轉換器、正交調制器和射頻頻率綜合器等大量的分立器件,導致測控設備種類繁多、體積龐大,缺少統一的技術規范,設備管理和維護十分復雜,并且在有新的設計需求時,設備無法重復利用,更新的代價極大。因而小型化、低能耗、多功能、高集成度的無線通信系統成為了未來發展趨勢[1]。為了滿足這些要求,許多新的方案不斷被提出,其中就包括軟件無線電技術。軟件無線電技術是將通信系統中射頻前端電路實現為軟件可控制、硬件可配置和高度芯片化的硬件平臺,可利用更改配置的方式進行多種模式的通信,能夠適用于各種通信方案及通信頻帶。

軟件無線電技術的概念是由美國Joseph Mitola 博士提出的,目的是解決戰爭中的互聯互通問題。1992 年,美國軍方制定并推進了“Speakeasy”項目,目的是為實現電臺之間不同通信協議下的數據交互。此項目獲得階段性成功后,陸續推進了“Speakeasy”項目第二、三期以及聯合戰術無線電系統(joint tactical radio system,JTRS)計劃,把可編程通信領域的發展推向了新的階段。經過了30 年的發展,軟件無線電技術已獲得了長足的進步,不僅應用于軍事領域,也逐漸應用于日常生活的各個領域中。自高性能射頻收發芯片AD9361 推出后,其便經常被用于以軟件無線電概念為基礎的通信平臺中,其中國內的典型應用是姜浩等[2]設計的現場可編程門陣列(field programmable gate arrays,FPGA)+AD9361的軟件無線電平臺以及方良[3]設計的Zedboard開發板+AD9361 的視頻傳輸系統,這2 個平臺均使用AD9361 完成信息數據的無線收發來滿足具體的應用需求,證明了AD9361 芯片具有良好的傳輸性能。

綜上所述,針對如今無線通信系統對設備的體積、能耗以及系統功能多樣性和集成度的要求[4],本文提出了一種搭載FPGA(KINTEX-7)和AD9361 芯片的軟件無線電平臺設計方案。此平臺以FPGA 為系統主控制器,能夠完成外部數據的基帶處理過程,同時搭建MicroBlaze 嵌入式軟核[5]作為處理器對AD9361 進行寄存器配置,使用手動增益控制(manual gain control,MGC)方式對收發通道進行發射功率、接收增益以及頻點的控制,并經過多次更改參數進行收發測試。觀測結果表明,該平臺的通信性能夠滿足高集成度、多功能性的無線通信系統的應用需求。

1 AD9361 介紹

AD9361 是ADI 公司產出的一款高性能射頻捷變收發芯片,芯片內部集成了各2 路接收器和發射器,它們彼此之間相互獨立,每一路接收器或發射器都含有I、Q 這2 個獨立通道,每個I 路或Q 路通道都是1 個直接變頻系統,使用同一個頻率合成器進行正交混頻。對于發射器,其本機振蕩器的工作頻率為47 MHz~6.0 GHz;對于接收器,其本機振蕩器的工作頻率為70 MHz~6.0 GHz[6],AD9361 芯片發射器和接收器的工作頻率范圍涵蓋了大部分常用通信頻段,具有優秀的集成性能和通用性能[7]。AD9361 收發通道支持的帶寬為200 kHz~56 MHz,并且具有較強的可編程性,可以根據具體工程配置芯片的工作頻點和通道帶寬[8?9]。

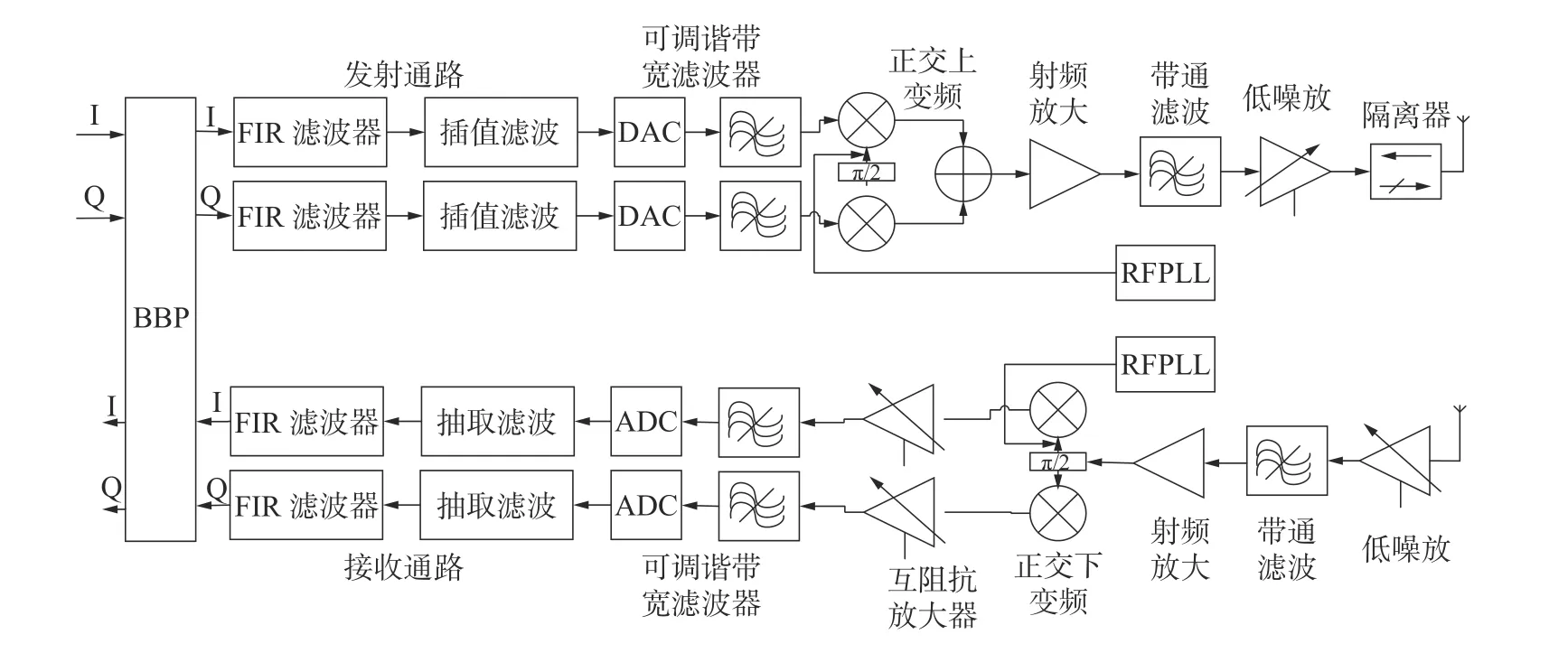

AD9361 芯片內部集成的發射子系統和接收子系統均具有自動增益控制功能[10],對于發射子系統,2 個獨立的發射通道都具有數字濾波的功能,數字信號經有限沖擊響應(finite impulse response,FIR)濾波、插值濾波后,送入芯片內部集成的12 位數模轉換器(digital to analog converter,DAC),完成數字信號的模擬化,最終完成正交上變頻并將I、Q 這2 路數據合并為1 路進行發射。對于接收通道,在對接收信號進行帶通濾波及正交下變頻等處理后,芯片內部集成的12 位模數轉換器(analog to digital converter,ADC)將接收的模擬信號數字化,隨后將信號通過抽取濾波和FIR 濾波后提供至基帶處理模塊[11],AD9361 內部數據處理如圖1 所示。此外,AD9361 芯片具有手動增益控制功能,可對發射通道的發射衰減和接收通道的接收增益進行調節,開發者和使用者可借助此功能對通信系統的信噪比進行調整。

圖1 AD9361 內部數據處理框圖

2 搭載KINTEX-7 和AD9361 的軟件無線電平臺設計

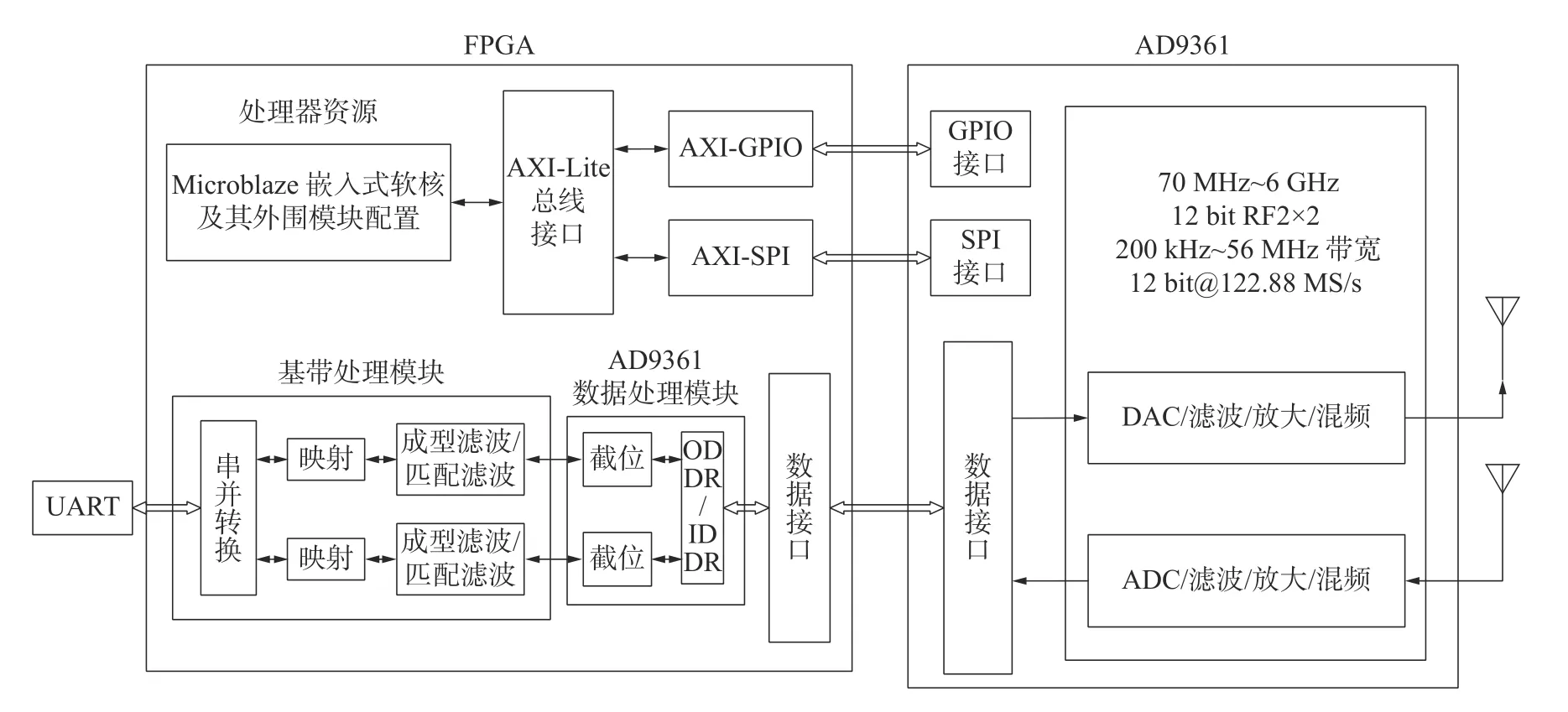

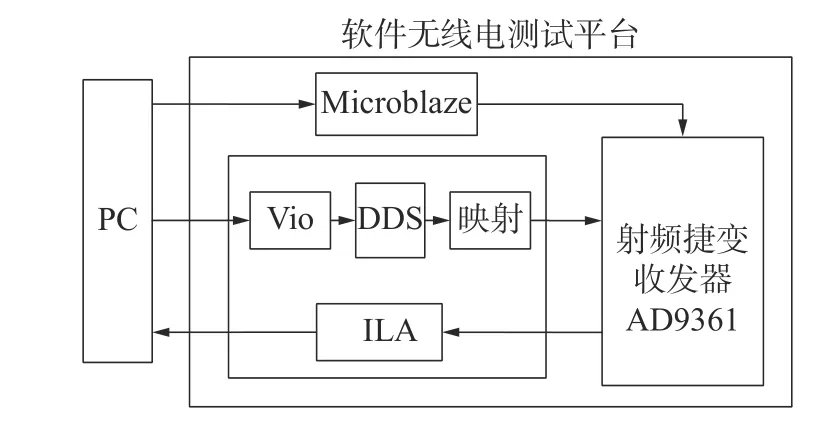

本文基于KINTEX-7 和AD9361 實現通用軟件無線電平臺的設計,其中KINTEX-7 作為主控芯片,通過嵌入式微處理器MicroBlaze IP 核在FPGA 內部實現微處理器的構建,使FPGA 具有執行相應匯編和C 語言指令的功能,能夠對AD9361 芯片進行各種收發通道參數的設置,并且能夠實現AD9361 芯片與FPGA 基帶數據處理模塊之間的數據互通,實現了高集成度、高靈活性、可移植性強、多功能的無線通信設備的設計,軟件無線電平臺的系統框架如圖2 所示。此軟件無線電平臺的設計指標如下:基帶數據傳輸速率為200 Kb/s~10 Mb/s,可調諧通道帶寬為200 kHz~56 MHz,通信頻點可調工作范圍為200 MHz~5 GHz,發射衰減支持范圍為20~50 dB,接收增益支持范圍為30~76 dB。

圖2 軟件無線電平臺系統框架

軟件無線電平臺具有軟件、硬件可編程性以及I/O 接口的可編程性,基于C 語言完成軟件無線電平臺正常工作所需的參數配置,并且能夠使用高級可擴展接口(advanced extensible interface,AXI)總線完成MicroBlaze 軟核處理器[12?13]和FPGA 之間的數據交互和邏輯功能互聯[14]。

AD9361 芯片的數字接口有3 種,分別是串行外設接口(serial peripheral interface,SPI)、通用輸入輸出(general purpose inputoutput,GPIO)接口和高速數字接口,其中SPI 接口用于傳輸控制信息,GPIO 接口用于讀取AD9361 的工作狀態并對AD9361進行狀態控制,高速數字接口用于和FPGA 之間傳輸基帶數據。使用FPGA 的邏輯資源將GPIO、SPI 等各個功能模塊組裝成帶有AXI 總線的知識產權(intellectual property,IP)核,并通過FPGA 的I/O 接口完成與AD9361 射頻芯片之間信息數據的交互。

在發送階段,數據源使用串口傳輸的方式在FPGA 的驅動下注入到基帶處理模塊,基帶處理模塊根據相應需求將數據進行串并轉換、映射以及成型濾波等一系列操作,生成的基帶信號通過高速數字接口傳輸至AD9361 芯片,AD9361 內部集成的DAC 將基帶處理模塊輸出的信號轉換為模擬信號,隨后進行濾波、放大等操作,最后與預設頻點對應的載波信號進行混頻,將混頻后的信號合并成1 路,通過天線進行發射。在接收階段,外部天線接收的無線數據通過AD9361 內部集成的ADC 轉換為數字信號,經混頻、濾波、放大等操作后,將數字信號送入基帶處理模塊,基帶處理模塊對信號進行映射、并串轉換,還原出信息數據。

3 開發流程

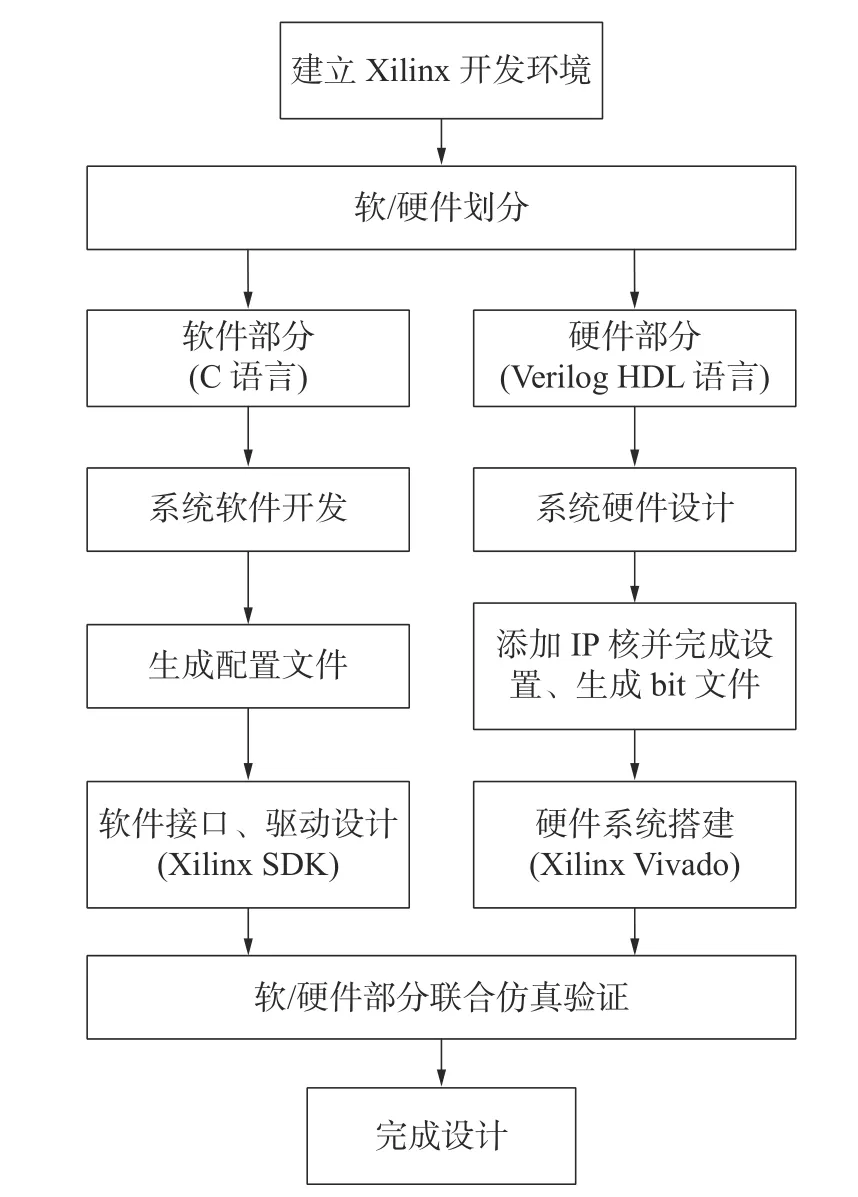

搭載KINTEX-7 和AD9361 的通用軟件無線電平臺的開發分為軟件部分和硬件部分,2 部分分別使用C 語言和Verilog 語言進行設計和開發,并使用FPGA 作為主控芯片,進行軟硬件部分的集成,最終完成軟件無線電平臺整個系統的搭建并進行仿真驗證與邏輯優化,設計流程如圖3所示。

圖3 平臺設計流程

軟件無線電平臺的軟件部分主要由FPGA 內部集成的嵌入式軟核MicroBalze 來完成,通過配置MicroBlaze IP 核完成軟件部分處理平臺的搭建,使用AD9361 Evaluation Software 2.1.3 軟件生成AD9361 配置文件,并通過此嵌入式軟核執行配置文件中相應的C 語言指令,完成對AD9361射頻芯片的狀態控制和參數配置。

軟件無線電平臺硬件開發的部分主要是對FPGA 芯片邏輯資源的使用,包括MicroBlaze 外圍各IP 核的配置、基帶數字信號處理模塊的設計和開發以及AD9361 數據處理模塊的設計和配置。根據FPGA 型號(KINTEX-7)對應的硬件資源對GPIO、SPI 和通用異步收發器(universal asynchronous receiver/transm-itter,UART)等Xilinx的IP 核進行開發,并根據AD9361 的接口類型將邏輯資源封裝成帶AXI 總線的功能IP。其中,帶AXI 總線的GPIO 核完成AD9361 的狀態控制,SPI 核完成寄存器配置,UART IP 核預留,用于后續功能的開發。由于AD9361 芯片的數據接口位寬為12 bit,因此在本平臺的開發過程中,在FPGA 內部搭建AD9361 數字處理模塊對數據進行截位處理,將數字基帶處理模塊輸出的16 bit數據截取低12 bit,隨后進行速率轉換并輸出至AD9361 完成軟件無線電平臺的射頻功能。

4 功能驗證

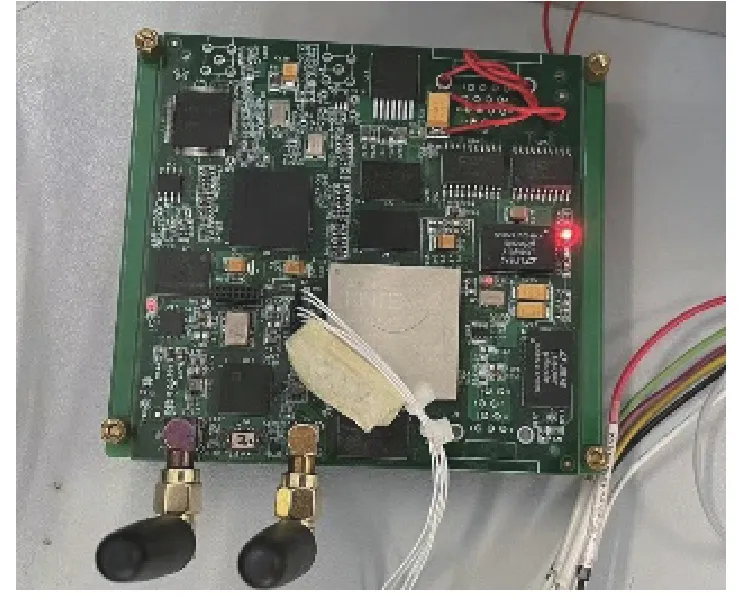

搭載KINTEX7 和AD9361 的通用軟件無線電平臺在方案設計上采用軟硬件部分各自開發、協同調試的方式。在功能測試和驗證過程中,可將平臺的軟件部分和硬件部分看作2 個獨立設計,修改其中一個部分不會影響另外一個部分的正常工作,僅是改變了系統的基帶處理類型或參數配置狀況。例如,需要更改信息數據的處理方式時,僅需要修改硬件部分基帶處理模塊的編譯文件,將需求的調制框架添加到系統中即可,無需更改其他模塊的設計與處理流程;若需要更改AD9361 的參數配置狀況,僅需修改軟件開發套件(software development kit,SDK)平臺下的配置文件,通過C 語言的編譯即可達到更改AD9361 收發通道參數的目標,無需更改FPGA 邏輯資源的設計與使用。由于本設計軟件、硬件部分的獨立性和復用性,使得無線電平臺具有高度的可編程性,在根據需要更改調制方式或參數配置時更加靈活、易操作,能夠適應各種應用場景,圖4 為搭載FPGA 和AD9361 的通用軟件無線電平臺。

圖4 軟件無線電平臺

數字調制技術是現代通信的重要方法,其中相移鍵控(phase shift keying,PSK)將不同的碼元用不同的載波相位來表示,是一種用相位表達信息的調制方式[15]。而正交相移鍵控(quadrature phase shift keying,QPSK)是多進制調制技術中比較常用的,它將每2 個信息比特組合成一個碼元,可以看作是I、Q 這2 路正交的BPSK 調制信號相加之后得到的,在相同傳輸速率下,QPSK 調制系統的頻帶利用率更高。QPSK 信號可表示為

式中:g(t)為碼元的時域信號波形,Ts為碼元寬度,ωc為調制載波角頻率, φn為第n個碼元的基帶信號代表的相位。若I、Q 這2 路正交信號分別表示為則有:

本文為驗證軟件無線電平臺的功能是否滿足設計要求,搭建功能驗證平臺框架。在PC 端使用AD9361 Evaluation Software 2.1.3 軟件對AD9361進行硬件配置,選取類型為典型的LTE 5 MHz 標準,增益控制類型為MGC,生成配置文件,使用MicroBlaze 軟核執行相應的指令,完成AD9361 的寄存器配置。同時,在PC 端通過Vivado 平臺完成基帶處理模塊的設計及程序編譯,使用Vio IP 核配置虛擬IO 接口進行頻率控制字的寫入,并通過DDS IP 核[16]產生載波信號。在本文功能驗證過程中使用QPSK 調制方式生成I、Q 這2 路正交波形,經截位、速率轉換處理后輸出至AD9361 芯片,完成調制信號的自回環收發測試,并使用Vivado 平臺的集成邏輯分析儀(integrated logic analyzer,ILA)抓取接收信號,并在PC 端進行信號的觀測。功能驗證平臺框架如圖5 所示。

圖5 功能驗證框架

在功能驗證流程中,系統的參數初始值設置如下。DDS 頻率控制字:028F[H];基帶通信標準:LTE 5 MHz;基帶傳輸速率:7.68 MHz;通信頻點:200 MHz;發射衰減:30 dB;接收增益:50 dB。

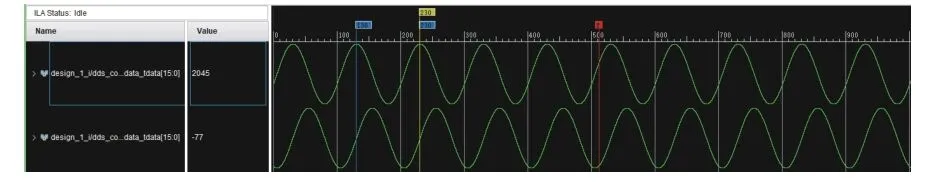

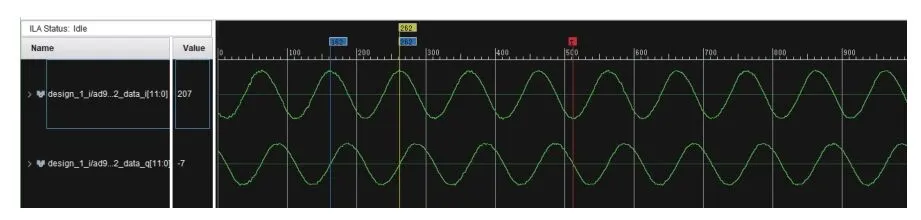

圖6為數字基帶處理部分輸出的I、Q 這2 路波形信號觀測圖,圖7 為經AD9361 發射并接收的信號波形觀測圖。

圖6 輸出波形

圖7 接收波形

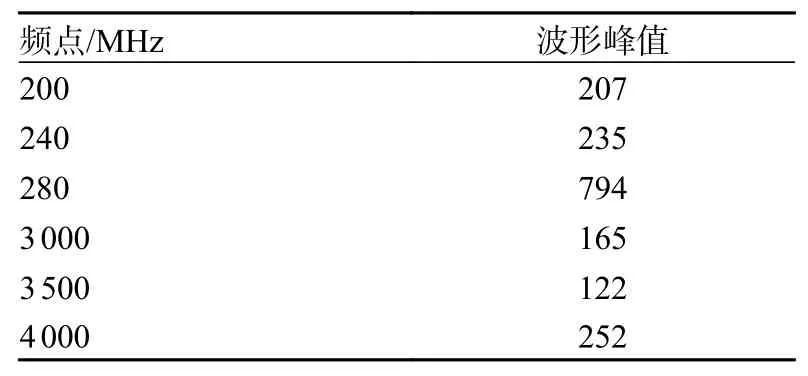

由信號觀測圖可以看出,本文設計的軟件無線電平臺具有良好的收發性能,接收信號的波形平滑,無明顯毛刺出現,且峰值和谷值處無畸變,能夠滿足系統要求。為進一步驗證系統性能,對不同工作頻點進行多次收發測試,測試結果如表1所示。

表1 不同頻點下的測試結果

AD9361 射頻收發芯片收發通道的數據接口位寬均為12 bit,因此能夠表示的數值范圍為?2 048~2 047。根據測試結果可以看出,相對于發射信號,接收數據波形的峰值有所下降,這會對調制信號的解調產生負面影響。

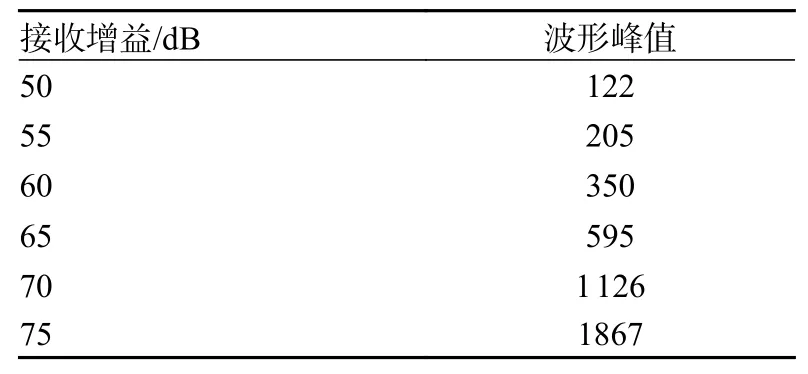

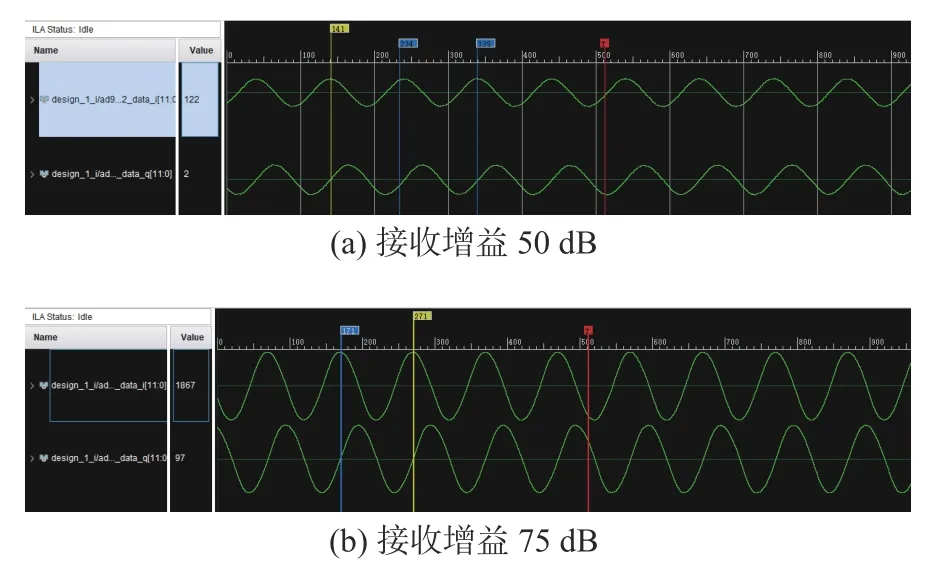

針對接收信號的峰值性能較差的問題,使用MGC 的方式更改收發通道參數進行測試。以3.5 GHz 頻點為例,在發射衰減為30 dB、接收增益為50 dB 的參數下,接收信號波形的峰值性能較差。現固定發射衰減,更改接收增益的大小并觀測結果,如表2 所示。

表2 3.5 GHz 頻點下不同接收增益的測試結果

固定通信頻點為3.5 GHz、發射衰減為30 dB的條件下,圖8 為不同接收增益下的接收波形。能夠看出,通過增大接收增益,接收信號的峰值有較大增加,在75 dB 下峰值能達到1867,達到發射通道信號峰值的90%以上,對系統傳輸性能有較大提高。

圖8 通信頻點3.5 GHz 時不同接收增益下的接收信號波形

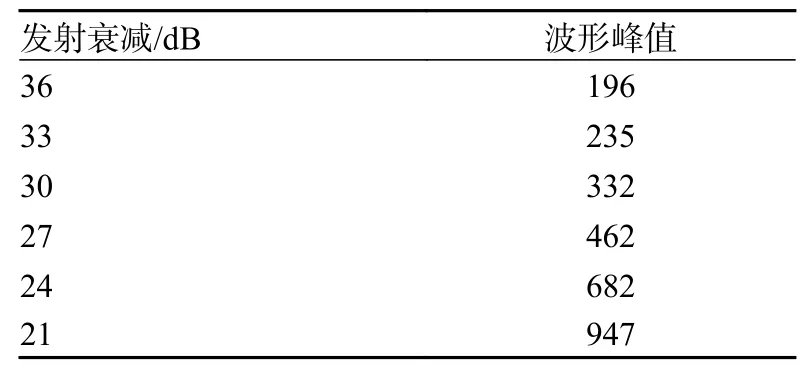

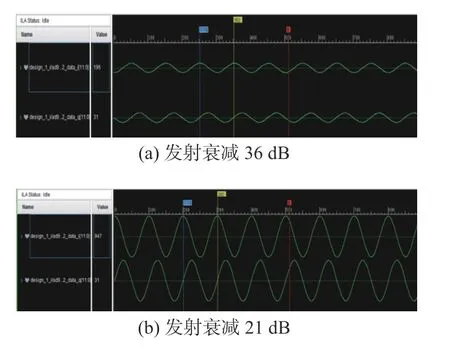

同樣,以4.5 GHz 頻點為例,在發射衰減為36 dB、接收增益為65 dB 的參數下,接收信號波形的峰值性能較差。固定接收增益,更改發射衰減數值并觀測接收結果,如表3 所示。

表3 4.5 GHz 頻點下不同發射衰減的測試結果

固定通信頻點為4.5 GHz、接收增益為65 dB,圖9 為不同發射衰減下的接收信號波形。能夠看出,通過減小發射衰減,接收信號的峰值有較大增加,在發射衰減為21 dB 下,接收信號峰值能達到947。

圖9 通信頻點4.5 GHz 時不同發射衰減下的接收信號波形

綜上,通過更改系統的收發通道參數,使得接收信號波形的峰值性有了較大改善,更加有利于接收數據的后續解調、譯碼等操作。

5 結束語

本文提出了一種搭載KINTEX-7 和AD9361的通用軟件無線電平臺的設計方法并進行了功能驗證。該平臺采用軟硬件部分各自開發、協同調試的方式,使用MicroBlaze 嵌入式軟核完成對AD9361 的狀態控制和參數配置,并通過對FPGA內部邏輯資源的開發完成基帶數據的處理,有效地減小了系統的電路體積。相較于傳統的通信設備,本平臺具有多功能、高靈活性等優勢。此外,本文在功能測試階段,通過MGC 方式調整收發通道的參數,進一步提高了通信性能,并為此平臺后續的開發提供了數據支持。