一種寬電壓范圍高瞬態響應LDO的設計與實現

戴 瀾 栗 元

(北方工業大學,北京 100144)

0 引言

降壓式DC-DC 是在一個較寬的電源電壓下工作的,這就要求LDO 有一個很寬的電源電壓范圍。目前,常用兩級降壓方案來解決這個問題,即用一級預穩壓方式將電源電壓降到合理范圍內[1],但這會導致電路復雜度大幅度增加。此外,LDO 不僅對帶有驅動器電源管理芯片的芯片電路進行供電,還對外部開關驅動管柵極電容進行充放電,這就要求LDO 有很高的瞬態響應。為了保證在頻繁的負載跳變中保持LDO的穩定輸出,要設計額外的擺率增強電路[2-6],同時在輸出端外接一個很大的電容(μF級)。當輸出電容很大時,傳統的米勒補償也要有很大內部的補償電容[7-8],而大的補償電容會浪費很多版圖面積。所以,在保證良好負載瞬態響應的同時,減小補償環路的電容是非常重要的。

針對上述問題,本研究提出一種帶有高壓管的Cascode 電流鏡,其中,低壓管用于鏡像電流,高壓管承載高壓。在不增加電路負載度的前提下,擴大電路的工作電壓范圍。針對大負載電容,使用一種帶源極跟隨器的Ahuja 補償結構[4],提高電路對電容負載的驅動能力,從而保證LDO的瞬態響應。

1 電路設計和原理分析

1.1 LDO的系統結構

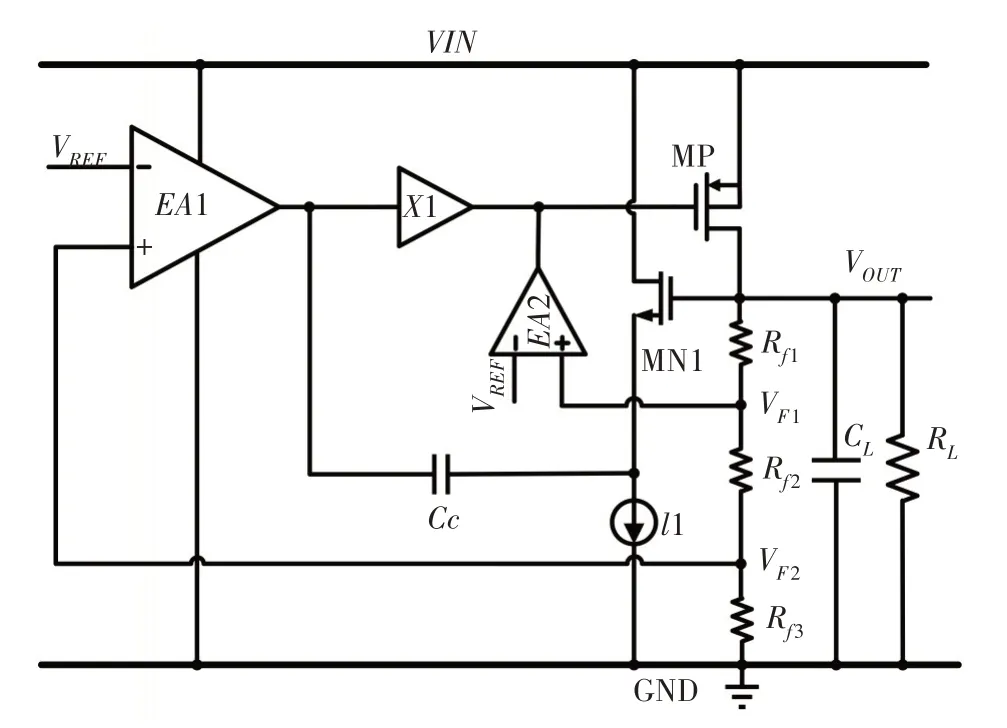

本研究提出的寬電壓范圍高瞬態響應LDO 的系統框架如圖1 所示,包括6 個部分,即誤差放大器、Buffer、功率管MP、電壓反饋網絡、頻率補償網絡及快響應環路上的運算誤差放大器。其中,誤差放大器采用對稱OTA,對其使用的高電源電壓進行特殊處理,可滿足電路工作要求。采用帶源極跟隨器的Ahuja 補償結構來保證環路穩定性,同時能減小補償電容,而快速響應環路保證負載突變時的穩定輸出。

圖1 寬電壓范圍高瞬態響應LDO的系統框架

1.2 寬電壓范圍偏置電流源與誤差放大器

為滿足電路較寬的工作電壓范圍要求,本研究設計出一種高壓Cascode 電流源與高電源電壓誤差放大器,如圖2、圖3所示。

圖2 寬電壓范圍Cascode偏置

圖3 寬電壓范圍誤差放大器

在進行電壓偏置時,利用帶隙基準產生1.2 V電壓,經Q1與Q2三極管組成的電流鏡,根據比例將電流鏡像到各個支路。其中,Q1的電流表示見式(1)。

式中:IQ1為三極管Q1的電流;VREF為基準電壓;VBE1為Q1的基極與發射極二極管導通電壓,約為0.6 V;R為電流配置電阻。

與Cascode 不同的是,在寬電壓范圍偏置中,以24 V 的高壓MOS管來替換普通的共柵管(見圖2中的MP7、MP8、MN8)。這是因為在Cascode 電流鏡像中,起到主要電流鏡像作用的是共源管,其可用來增加電流鏡的輸出阻抗。同時,由于高壓管的匹配性較差,不將其作為共源管。所以,帶有高壓共柵管的結構既保證電流鏡的精準復制,又提高偏置的電壓范圍,使LDO能在一個較高的電源電壓范圍內工作。

誤差放大器采用的是對稱式OTA 架構,MP1~MP6、MN1~MN4 為低壓管,MN5、MN6 與三路電流鏡中的cascode 管(與M7、M10 組成的結果一致)為高壓管,這樣才能確保誤差放大器在一個較寬的電源電壓范圍中工作。誤差放大器的第一級輸入為源極跟隨器,以源極跟隨器來進行輸入,可增加誤差放大器的輸入阻抗,使輸入信號產生電平位移,保證電路始終在一個合適的靜態工作點上工作;第二級由對稱式運算放大器構成,其中MN5、MN6 及電流鏡中的共柵管為高壓管。相較于普通結構,對稱式OTA具有更好的失調和CMRR特性。

在圖3中,對稱式OTA開環增益AV表示見式(2)。

式中:gm和ro分別為晶體管Mi的跨導和輸出電阻;N為MN1 與MN2 組成電流鏡的比例。為了便于分析,將N管與P管的跨導近似相等。

在OTA 中,只有輸出節點為高阻節點,其他節點都在1/gm左右。所以其是一個單極放大器,該OTA主極點的表示見式(3)。

式中:CL為負載電容。

聯立式(2)、式(3),OTA 增益帶寬積GBW的表示見式(4)。

由式(4)可知,電流鏡的比例會影響OTA 的GBW,但不能無休止地增加N,這是因為MN2 的柵極存在寄生電容(假設寄生電容大小為Cn),會產生第二極點fnd,見式(5)。

其中,Cn的表示見式(6)。

將式(6)帶入式(5)中,整理后得式(7)。

由式(7)可知,非主極點的頻率由轉角頻率fT和電流鏡比例N共同決定,N越大,非主極點頻率就越低,所以限定了N的最大值。

1.3 第二(快速反饋)環路誤差放大器

本研究采用的是快反饋環路中的第二誤差放大器(EA2),如圖4所示。由于反饋路徑較短,反應速度要快于主環路。次級反饋環路在啟動及負載發生大幅波動時會產生作用,從而保證電路的啟動速度,并優化電路的響應能力。

圖4 第二環路誤差放大器電路

第二誤差放大器以雙極型晶體管為輸入對管,這是因為電路要有比較快的反應速度,才能有比主環路更快的響應速度,但為了保證整體環路的穩定性,將次級環路的整體增益保持在一個較低的水平。

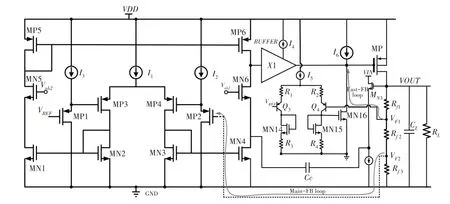

1.4 寬電壓范圍快速響應LDO

本研究設計的寬電壓范圍快速響應LDO 的整體電路如圖5 所示,其主要由兩個環路構成,兩個環路的誤差放大器分別為由高工作電壓范圍OTA構成的主反饋環路和以三極管為輸入對管的快速反饋環路。由于兩個環路反饋的分壓值不同(VF1<VF2),所以要依靠主環路才能使電路正常工作,這是因為主環路的環路增益被設置為一個更高的值。當電路發生異常情況時,負反饋環路工作。在電路啟動時,兩者的電壓均低于VREF,此時兩個環路都會進入工作狀態;當電路負載急劇變化時,可能會導致輸出電壓變換過大,此時快反饋環路也會工作。由于將LDO 應用于DC-DC 開關管驅動部分,負載跳變是一個常見狀態,所以增加一個快速環路是非常有必要的。考慮到電路的負載特性,LDO 主要用于驅動大電容負載,在功率管輸出電流不同時,傳統米勒補償會造成電路主次極點靠近,甚至交換。若要保持穩定,就會大幅增加補償電容的容值。與此同時,電容的前向通路也會帶來一個右半平面零點,進一步降低環路的穩定性。所以,本研究使用帶源極負反饋的Ahuja電容補償來進一步增強電路驅動電容的能力,能有效消除右半平面零點的影響,減小補償電容。

圖5 寬電壓范圍高瞬態響應LDO電路

2 性能分析

2.1 LDO瞬態分析

將本研究提出的LDO應用于實際場景中,即大輸入電壓、負載急速切換及大負載電容(見圖5)。在大信號方面,快反饋環路是在電路啟動時,因輸入電源電壓未達到VOUT時,VF1與VF2均低于VREF,此時主反饋環路與負反饋環路都在工作,從而提高電路的啟動速度。在負載迅速切換過程中,由于快速反饋環路的反饋路徑較短,第二反饋環路能比主環路更早起作用,從而降低由負載突變帶來的過沖或下沖。

2.2 LDO環路穩定性分析

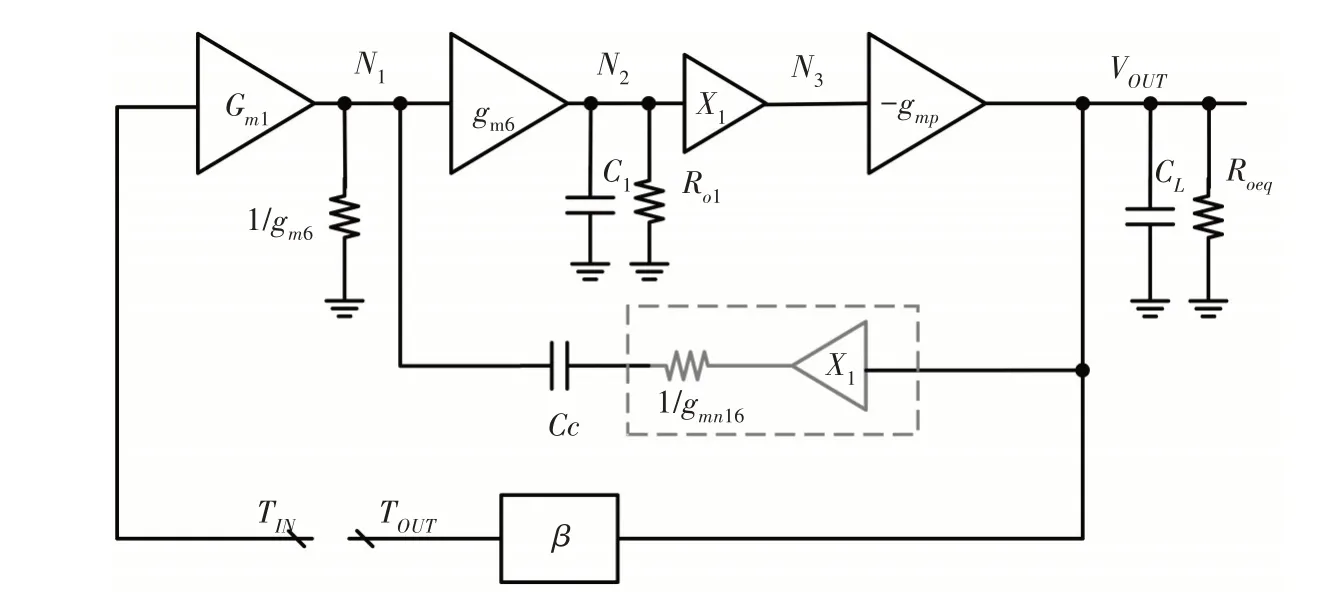

為便于分析系統的穩定性,在不影響分析結果的前提下,忽略高頻極點,且只考慮單位增益帶寬內和附近的極點,可降低傳遞函數的復雜程度。LDO等效小信號如圖6所示。

圖6 LDO等效小信號

整個環路大致可分為三級,將第一級的跨導記為Gm1,誤差放大器的等效輸出電阻與電容分別記為Ro1、C1,反饋電容跨接MOS 管MN6 跨導記為gm6,Buffer 的放大倍數為1,gmp為功率管跨導,β為反饋系數,CL與Roeq分別為等效負載電容與電阻,gm4與CC分別為源極跟隨MOS管跨導與補償電容。

基于圖中N1、N2、N3、VOUT節點電流方程,整理得LDO的小信號傳遞函數,見式(8)。

此外,韓國還編撰了各種學術道德普及型教材。如2006年韓國教育部編撰的《學術道德簡介》與2007年科學技術部編撰出版的《實踐學術道德》。這些教材的主要內容包括:研究的共同價值、研究計劃、研究的展開、研究報告與檢測、研究環境的重要性,利益沖突與利益分配,同事互相檢測,制定學術道德真實性檢測制度,學術不端行為的范圍界定,調查體系及展開過程,保護舉報者的措施等。

其中,a、b、c的表示見式(9)到式(11)。

根據LDO傳遞函數來區分其輕載與重載。

式中:p-3dB為主極點;pnd為次極點。

此時,電路主極點由輸出電容和輸出電路等效阻抗組成,次極點出現在EA1 的高阻抗輸出節點。使用Buffer 來隔離誤差放大器和功率管MP 柵極的寄生電容,所以C1是一個較小值。

由式(13)可知,在高負載情況下,電路同樣存在兩個極點,即1/gmp Ro1CC Roeq和gmp CC/C1CL。在大電流負載時,環路增益傳遞函數的最大單位增益帶寬頻率為ωu,max=Gm/Cc,相對于負載電流的變化,其是固定的。由于次級點的頻率總大于單位增益帶寬[9],所以主環路單位增益頻率內只有一個極點。此外,次極點隨著負載電流的增加而增加,這意味著LDO 的相位裕度和穩定性會隨著負載電流的增加而提高。

根據式(12)和式(13)可將LDO 簡化為一個二階系統,LDO的傳遞函數可簡寫為式(14)。

由式(12)得到LDO 在不同負載電流下的最穩定情況,確保補償電容Cc的設計值能使LDO 在整個負載電流范圍內都保持穩定。對二階系統來說,相位裕度最小處的穩定性最差。本電路的相位裕度表示為式(15)。

式中:ωu為單位增益帶寬,ωu/pnd越小,系統的PM就越大,系統就越穩定。

建立一個描述系統相位裕度的函數,見式(16)。

將式(12)中的主極點代入式(14)中,系統相位裕度函數見式(17)。

對式(17)求極值,得最小相位裕度的函數表達,見式(18)。

將式(18)代入式(15),得到最小相位裕度的函數表達,見式(19)。

可推導出最小相位裕度時的補償電容CC表示,見式(20)。

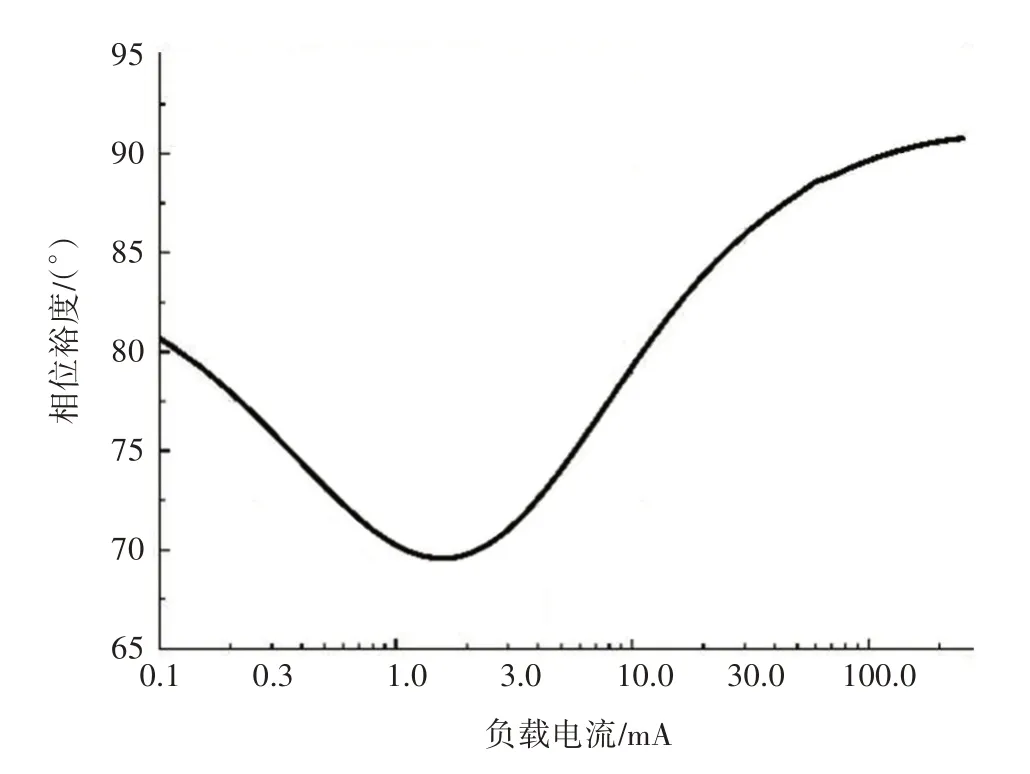

由此可知,補償電容與EA1輸出點的寄生電容有關。在EA1 輸出點與功率管柵極之間加入Buffer,能減小輸出點的寄生電容。全電流范圍內的電路相位裕度如圖7 所示,僅使用約10 pF 補償電容就可使電路在全電流范圍內保持穩定。

圖7 全電流范圍相位裕度

3 仿真結果

本研究設計的LDO 是基于華虹0.35 μm BCD工藝來完成電路設計的,采用Cadence 軟件對其進行仿真驗證。LDO的輸入電壓(VIN)為3~24 V、輸出電壓為5.4 V(VIN>5.8 V)、負載電流為0~260 mA、片外電容為1 μF。

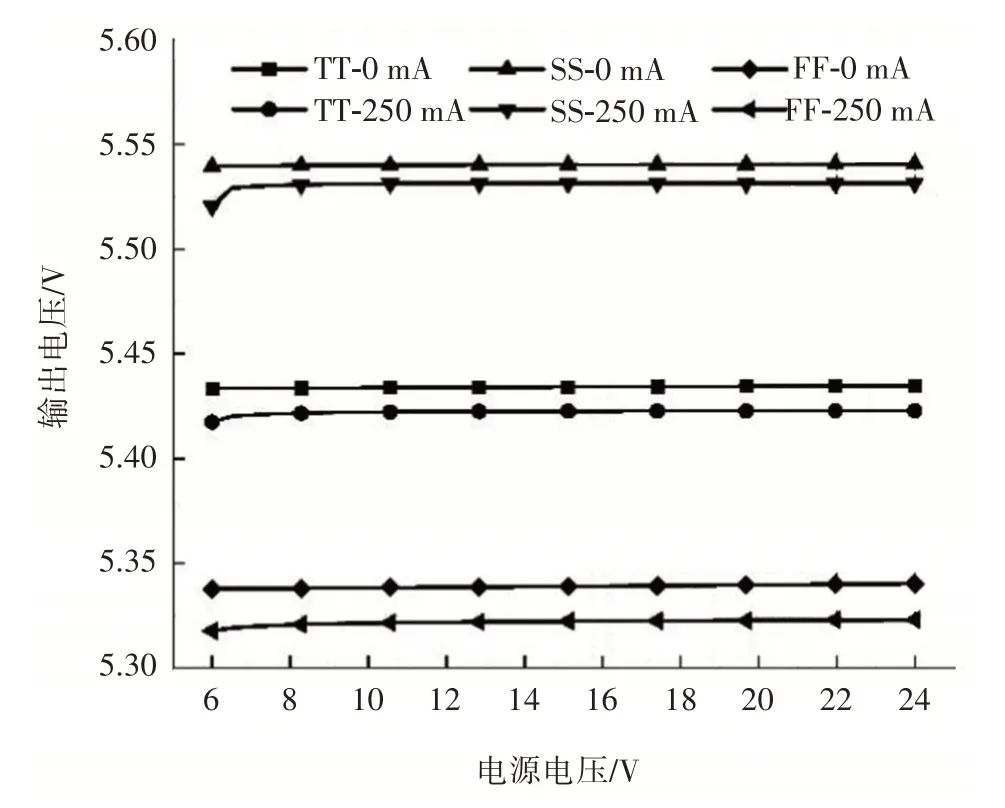

在不同工藝角下,分析輸出電壓隨輸入電壓的變化情況,分別在空載、10 mA、250 mA 負載條件下進行測試,結果如圖8 所示,最差的情況出現在SS最大負載電流為250 mA 時,此時的電源電壓調整率為0.61 mV/V。

圖8 輸出電壓隨電源電壓變化曲線

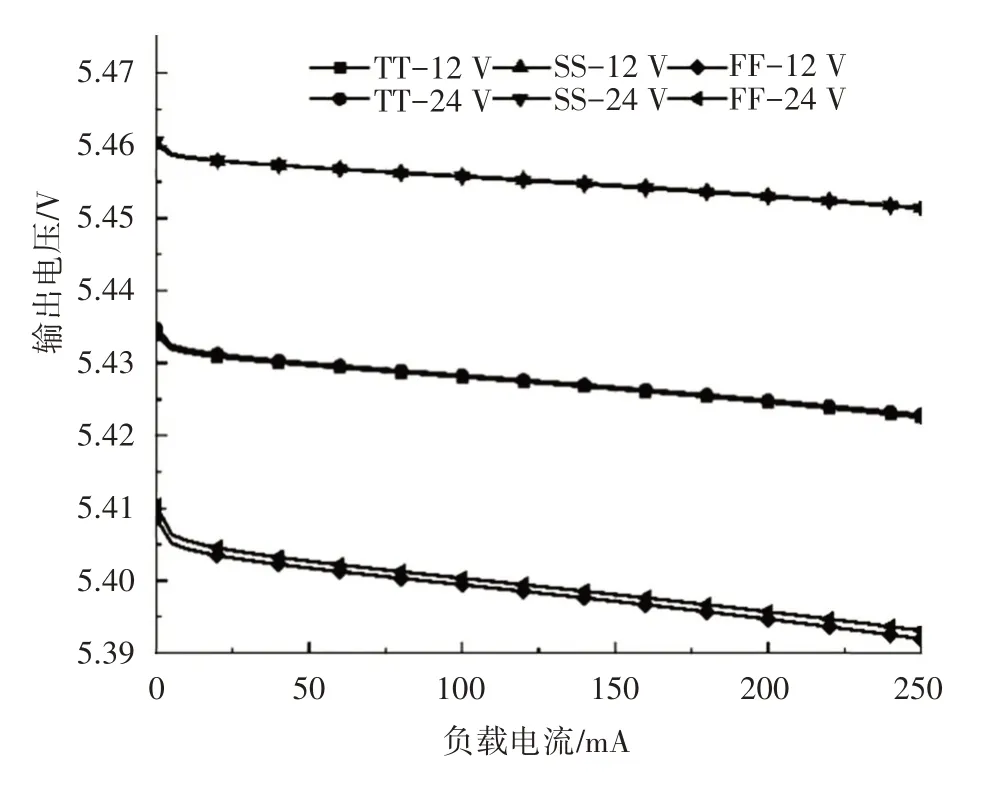

在不同工藝角下,測試LDO輸出隨負載的變化情況,分別在12 V、24 V 負載條件下進行測試,結果如圖9 所示,最差情況為FF12 V,負載調整率為60 μV/mA。

圖9 輸出電壓隨負載電流變化曲線

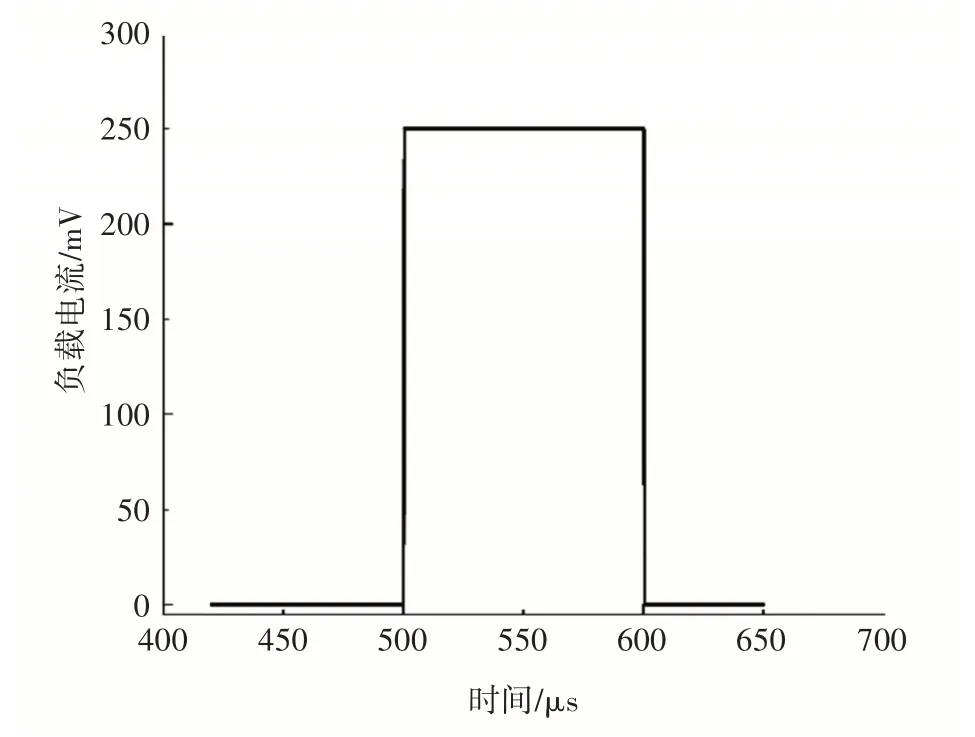

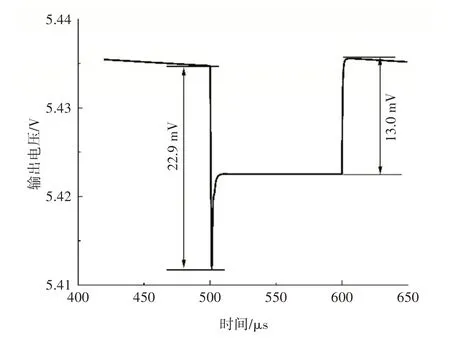

為驗證負載的瞬態響應特性,設置負載電流為0~250 mA、時間跳變為0.5 μs,結果如圖10 所示,LDO 瞬態特性仿真結果如圖11 所示。輸出下沖電壓為22.9 mV、過沖電壓為13.0 mV。穩定時間均在3 μs左右,LDO具有較好的瞬態響應特性。

圖10 負載跳變

圖11 LDO瞬態響應

將設計的LDO電路應用于一款電壓模PWM控制器中,LDO 電路的整體版圖如圖12 所示,版圖大小為1 167 μm×608 μm,滿足整體電路的面積要求。

圖12 LDO版圖

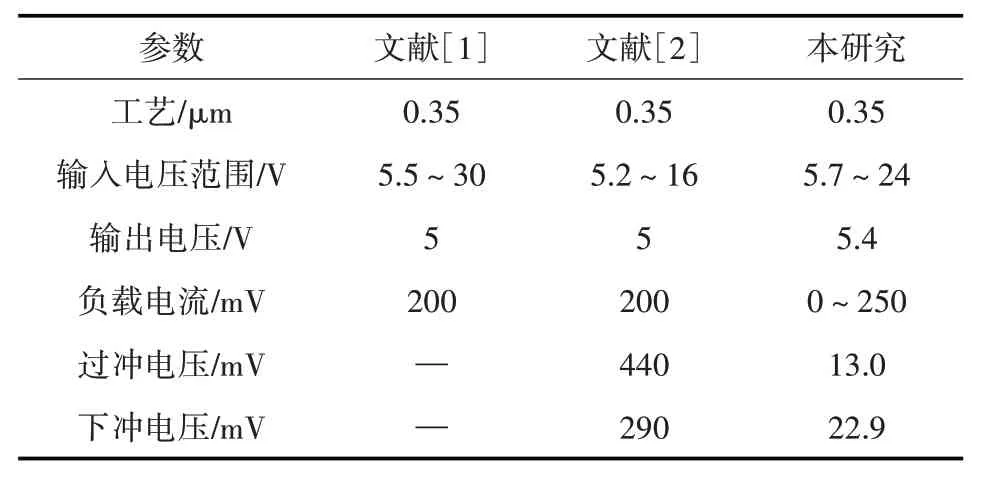

本研究設計的LDO 與其他已發表文獻中設計的LDO 主要參數對比見表1。由表1 可知,本研究提出的LDO采用寬電壓范圍偏置,擁有較寬的輸入電源范圍(6~24V),這得益于雙環路在更大范圍的負載波動情況下擁有較好的瞬態響應,過沖電源僅為13.0 mV。

表1 與其他文獻中LDO的性能對比

4 結語

本研究基于華虹0.35 μm BCD 工藝,設計出一款用于DC-DC 電源管理芯片的寬電壓范圍快速瞬態響應的低壓差線性穩壓器。針對DC-DC 電源管理芯片的特殊應用環境,使用寬電源電壓偏置與誤差放大器,確保整個LDO 工作在6~24 V 的電源電壓范圍內。為應對負載的頻繁快速變化,使用雙環路結構來提升系統的瞬態響應,而Ahuja 補償結構使電路在大電容負載條件下將相位裕度在全電流范圍內保持在60°以上。經仿真驗證,LDO 的電源電壓調整率為0.61 mV/V、負載調整率為60 μV/mA,且在電流從0 mA 突變到250 mA 時,輸出電壓過沖與下沖均小于35 mV,達到快速響應的要求,整個LDO 版圖面積為1 167 μm×608 μm,符合整體架構所分配的面積要求。