波動動態差分邏輯RISC-V CPU芯核的功耗抑制技術研究

崔小樂 李修遠 李 浩 張 興*

①(北京大學深圳研究生院集成微系統重點實驗室 深圳 518055)

②(鵬城實驗室 深圳 518055)

1 引言

側信道攻擊能夠從設備的側信道信號中提取加密操作使用的密鑰,給加密系統帶來了嚴重的威脅。差分功耗分析 (Differential Power Analysis,DPA)是側信道攻擊方法之一。它通過大量收集電路的功耗跡線,利用加密算法的中間值和設備運行過程中泄露的功耗信息之間的關系來獲取密鑰[1]。DPA是一種非侵入式的攻擊方法,因此相對而言容易實施。

密碼算法功能可基于硬件形式和軟件形式實現。硬件形式即在專用硬件電路上實現密碼算法功能,而軟件形式則是將密碼算法作為軟件程序運行在通用處理器上。目前研究表明,許多密碼硬件已經被DPA成功攻擊。例如,文獻[2,3]成功攻擊了AES (Advanced Encryption Standard)專用加密電路,Den Boer等人[4]成功攻擊了RSA (Rivset-Shamir-Adleman)硬件電路,Fan等人[5]成功破解了ECC (Elliptic Curve Cryptography)電路。另一方面,DPA攻擊對運行在通用處理器上的加密程序同樣具有威脅。Mpalane等人[6]對運行AES程序的PIC MCU成功進行了比特級的DPA攻擊,Petrvalsky等人[7,8]分別攻擊了運行在8 051 MCU和ARM核心上的AES軟件。對于基于開源指令集RISC-V的各種處理器,DPA攻擊也具有嚴重的威脅[9]。

因此,針對DPA攻擊的防御措施引起了學術界和工業界的極大關注。目前研究者提出的DPA防御措施主要分為兩類:掩蔽和隱藏。掩蔽措施對密碼算法的中間值進行混淆。例如,Akkar等人[10]將掩碼應用于AES和DES專用加密電路上。他使用一個固定的掩碼對明文進行XOR操作,從而實現了對這兩種加密電路的保護。Lu等人[11]在SM4電路加密的每一輪中注入一個隨機狀態來混淆中間值,從而達到抵抗DPA的目的。隱藏措施的基本思想與掩蔽措施不同,該類技術是通過改變電路運行期間的功耗或時序等特性,從而減少泄露信息。隱藏措施中較為常見的是構造安全的邏輯單元門,例如,Tiri等人[12]提出了WDDL (Wave Dynamic Differential Logic),Bucci等人[13]提出了TDPL(Three-phase Dual-rail Precharge Logic),Bellizia等人[14]進一步提出了SC-DDPL (Standard-Cell Delay based Dual-rail Precharge Logic)來抵抗DPA攻擊。

近年來,面向CPU的可抵抗DPA攻擊的防御技術也是研究熱點。Bayrak等人[15]通過隨機化處理器中獨立指令的執行順序和隨機化指令的調度來抵抗DPA攻擊。Bruguier等人[16]的工作中,將中間值進行掩碼操作的同時加入隨機延時,通過產生隨機噪聲來保護通用處理器。針對RISC-V指令集的處理器芯核,研究人員也提出了一些抵抗DPA攻擊的措施。例如,De Mulder等人[9]應用了基于掩碼閾值實現的掩蔽技術來保護RISC-V CPU芯核。Dao等人[17]提出了一種隨機動態頻率縮放(Random Dynamic Frequency Scaling, RDFS)技術,在每次加密/解密后隨機改變AES協處理器的時鐘頻率,從而在提高了RISC-V SOC的DPA防御能力的同時保持了較低的功耗。Antognazza等人[18]提出了代碼變形方法。該方法依賴于指令語義將密碼算法的源碼進行動態重編譯,從而產生一組相同語義的指令片段。在程序運行期間隨機選擇指令片段代替原來的指令進行運行。Leplus等人[19]提出了一種隨機插入偽指令來增加隨機延遲的方法。該偽指令的構造依據于處理器中運行的真實指令,因此攻擊者不易區分該指令與真實指令。Stangherlin等人[20]設計了一個位串行的RISC-V微處理器。它在邏輯級別上使用布爾掩碼將所有的數據進行保護,并且在晶體管級上使用動態多米諾邏輯有效地防御DPA攻擊。

掩蔽措施雖然在一定程度上可以提高硬件的抗DPA攻擊能力,但是由于大部分掩碼方法需要考慮密碼算法的具體實現方式,因此許多掩碼方案不具有普適性。當多個算法集成在通用處理器中時,每個掩蔽措施的代價將會累加在一起,造成處理器性能的大幅下降。而隱藏措施中的抗DPA邏輯單元改變了電路運行時的功耗特性,因此從根本上阻斷了功耗信息的泄露窗口,并且與算法的實現形式無關,所以相比于掩蔽措施來說,隱藏措施更加通用。文獻[21]中比較了不同的抗DPA邏輯單元。有些邏輯單元雖然抗DPA的能力更好,但是需要在晶體管級進行全定制的設計,不適用于處理器之類的大規模集成電路設計。同時邏輯單元在保證一定安全性的前提下,面積和功耗的開銷要盡可能的小。基于以上的考慮,本文選擇波動動態差分邏輯(Wave Dynamic Differential Logic, WDDL)應用在處理器的芯核上。

WDDL由Tiri在2004年提出,是經典的雙軌預充電(Dual-Rail Precharge, DRP)邏輯[12]。它能夠在不同的電路輸入下使加密電路的功耗跡線平坦化,從而防止信息的泄露。WDDL是支持標準單元庫的DRP邏輯,可以使用EDA工具進行自動化設計,更適合應用于大規模集成電路設計中。但是WDDL的預充電行為會帶來更多的功耗開銷。為了能使基于WDDL的防御措施更具有實用性,本文針對基于WDDL的抗DPA攻擊的RISC-V處理器芯核提出兩種功耗抑制技術。

本文的剩余部分安排如下:第2節回顧了WDDL邏輯電路的基本特征,并介紹了基于WDDL單元的RISC-V處理器芯核。第3節提出了兩種輕量級的電路功耗抑制的方法:隨機預充電使能技術和預充電使能指令技術。第4節討論仿真結果,第5節得出論文結論。

2 基于WDDL-ALU的Rocket處理器芯核

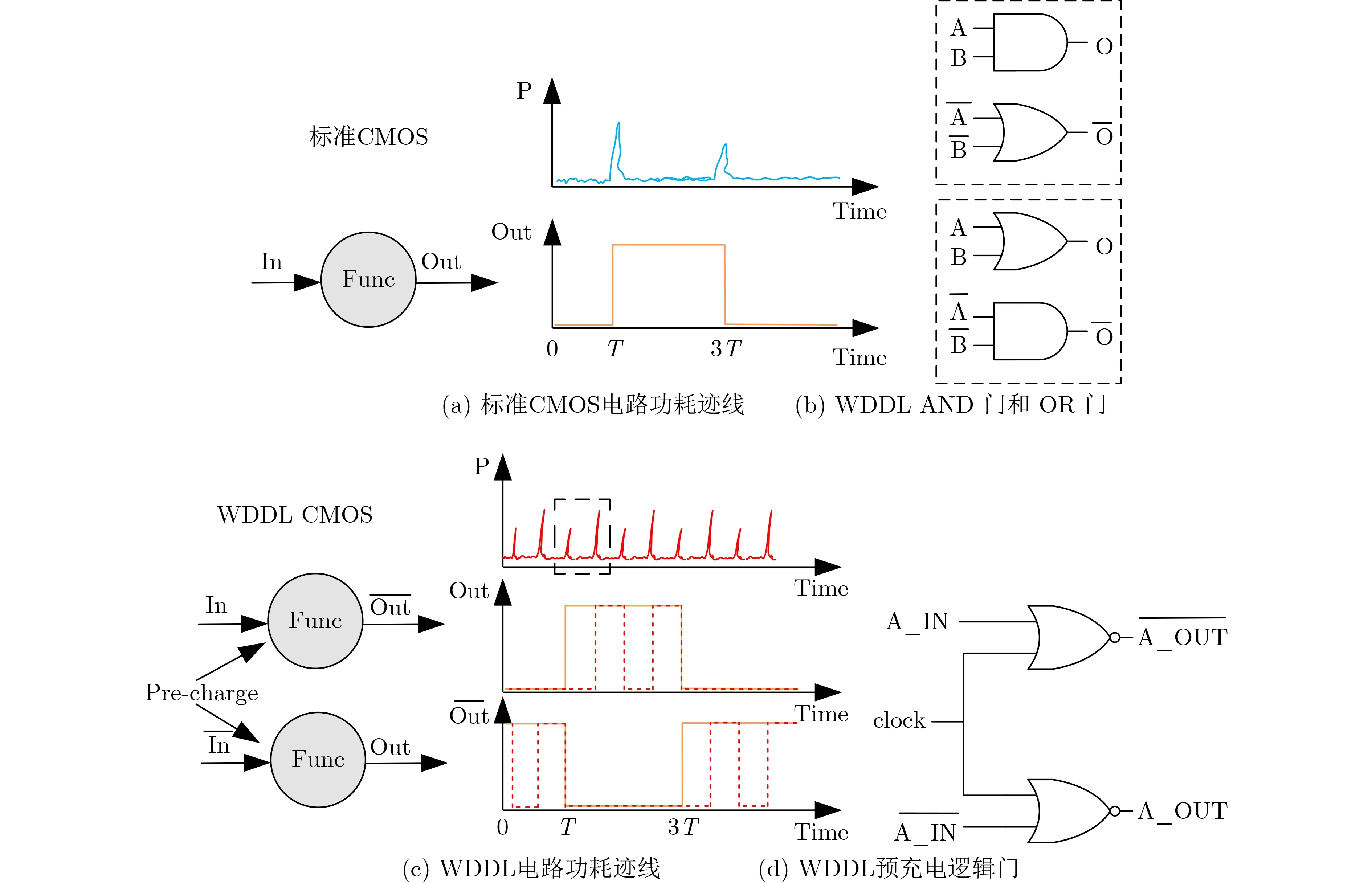

圖1(a)顯示了一個標準CMOS電路的輸出信號和其功耗跡線之間的關系。當輸出端信號的翻轉情況不同時,該電路的功耗信息也不同,因此可以根據功耗的變化來分辨輸出信號的翻轉情況。而WDDL邏輯的基本思想是通過預充電-求值的動態操作,使電路在每個周期內的功耗均勻化。圖1(b)為WDDL邏輯的與/或門結構示意圖。一個WDDL單元由原始邏輯門和其互補邏輯門組成。WDDL中使用的預充電邏輯門如圖1(d)所示。使用時鐘信號clock作為預充電控制信號,可以保證在每次求值操作前都進行預充電。在圖1(c)中,每個周期內電路的功耗分為預充電功耗和求值功耗。WDDL單元保證了在不同的信號翻轉情況下電路每周期的總功耗保持相同。WDDL單元被證明能夠有效地防御DPA攻擊。

圖1 標準CMOS電路與WDDL電路單元對比

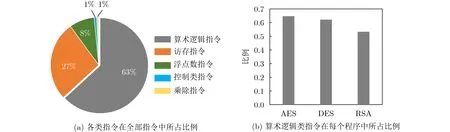

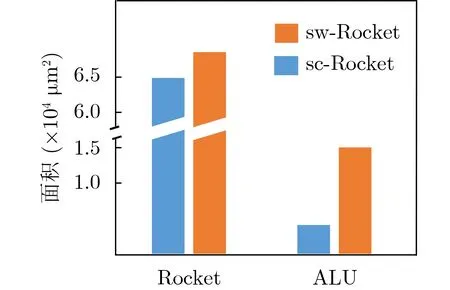

Rocket Core是加州大學伯克利分校開發的一款開源RISC-V處理器芯核,本文配置了一款支持RV64G指令集的64位Rocket芯核作為實驗對象。該芯核由5個模塊組成:ALU, BreakpointUnit,CSRFile, Ibuf和MulDiv。ALU模塊實現算術運算和邏輯運算功能;BreakpointUnit模塊實現硬件斷點功能;CSRFile模塊實現控制和狀態寄存器組;Ibuf模塊實現讀取/緩存執行指令;MulDIV模塊實現乘法除法功能。對于AES, DES, RSA等加密程序,圖2統計了程序主函數中各類指令的數目。從圖2(a)中得出,在3個程序的全部指令中,邏輯算術類指令所占比例最大,超過了60%;而從圖2(b)中可知,對于每個程序,邏輯算術類指令所占比例均超過50%。圖2表明這些加密程序所使用的主要指令屬于邏輯算術類,這些指令都是由Rocket芯核的ALU模塊處理的。WDDL電路相比于標準CMOS電路具有更大的功耗和面積開銷,把整個Rocket芯核都替換為WDDL單元的成本非常高,因此本文只將ALU模塊的CMOS單元替換為WDDL單元。本文將使用了WDDL-ALU的Rocket芯核稱為“sw-Rocket”,把所有模塊都用標準CMOS單元綜合的Rocket芯核稱為“sc-Rocket”。圖3顯示,WDDLALU模塊的面積比標準CMOS-ALU模塊增加了2.7倍;而與sc-Rocket芯核相比,sw-Rocket芯核的整體面積增加了15%。

圖2 密碼程序的匯編指令比例分析

圖3 sw-Rocket芯核的面積開銷

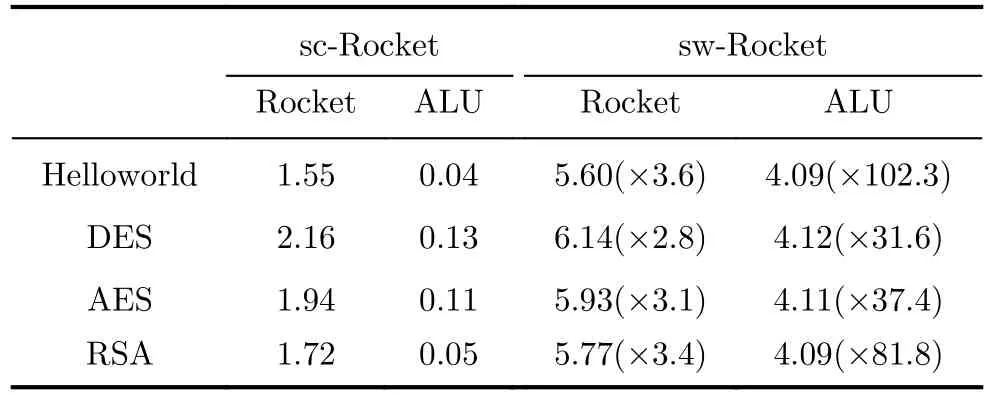

本文使用這兩種芯核進行了Helloworld, AES,DES和RSA等程序的仿真,并進行了功耗分析,結果如表1所示。在運行AES加密程序時, WDDLALU模塊的功耗是CMOS-ALU模塊的37.4倍,并且sw-Rocket芯核的整體功耗是sc-Rocket芯核的3.1倍。這是因為預充電-求值機制使得所有WDDL單元在每個時鐘周期內都產生兩次信號翻轉,然而CMOS單元在每個周期內最多產生1次翻轉。此外,sc-Rocket內部的CMOS-ALU模塊只有當被程序調用時才會產生動態功耗,然而sw-Rocket內部的WDDL-ALU模塊則在從上電到斷電的完整運行時間內均在產生動態功耗。因此,需要功耗抑制技術來使sw-Rocket芯核更具有實用性。

表1 不同程序的功耗比較(mW)

3 功耗抑制技術

WDDL的預充電行為帶來了大量的功耗開銷,本節提出了兩種技術對其進行控制從而降低功耗。

3.1 隨機預充電使能技術

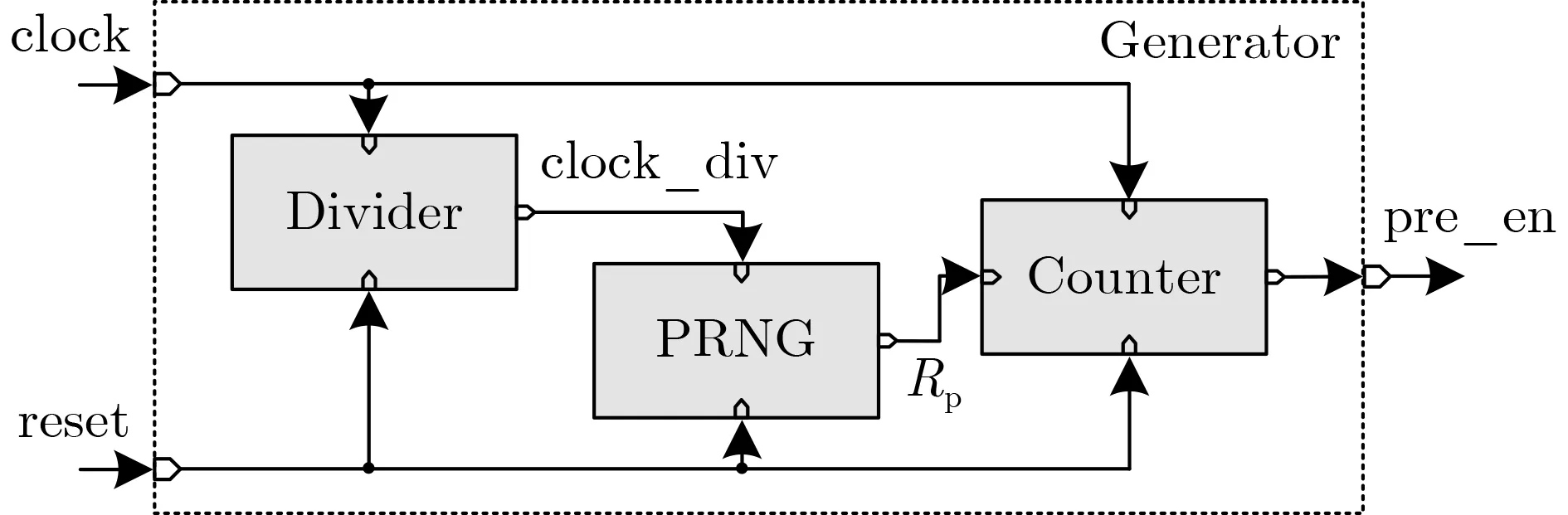

基于預充電行為的隨機化思想,可通過一個隨機預充電使能發生模塊來控制預充電的行為。隨機預充電使能發生器模塊的結構如圖4所示。它由分頻器Divider、偽隨機數發生器(Pseudo Random Number Generator, PRNG)和預充電信號產生器Counter等3個子模塊組成。分頻器的兩個輸入信號分別為Rocket芯核的全局時鐘信號和全局復位信號。該分頻器可根據配置參數NC的取值,產生1個周期是clock的NC倍的新的時鐘信號clock_div,以驅動下一級子模塊PRNG。如圖5所示,PRNG子模塊主要由LFSR(Linear Feedback Shift Register)和值偏置電路組成。該LFSR每周期可以生成1個16 bit的偽隨機數Rd。值偏置電路通過取模和加法操作,可對原始隨機數Rd進行計算處理,從而得到最終輸出Rp。該隨機數會發送到PRNG子模塊的輸出端口rand_val。Rd和Rp之間滿足關系式(1)

圖4 隨機預充電使能發生器電路結構示意圖

圖5 PRNG電路示意圖

其中NC和PC為配置參數,NC和PC共同決定了隨機數的范圍為[NC-PC-1,NC-1]。

預充電信號發生器是一個由全局時鐘驅動的循環計數器,計數范圍為[0,NC-1]。在每個周期內,計數值都會與輸入信號rand_val進行比較。如果計數值大于或等于rand_val,則將輸出信號pre_en置為1,否則置為0。

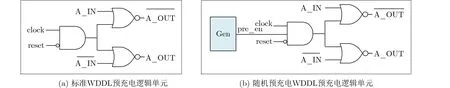

引入隨機化前后的預充電邏輯如圖6所示。圖6(a)是加入隨機化前的原始預充電邏輯,圖6(b)則是加入了隨機化的預充電邏輯,隨機預充電使能發生模塊的輸出和時鐘信號、復位信號共同控制預充電的行為,從而驅動sw-Rocket芯核內部的WDDL單元工作。隨機化的預充電使能信號可減少WDDL-ALU模塊的預充電行為數量,從而降低了它的功耗。

圖6 預充電邏輯單元電路結構

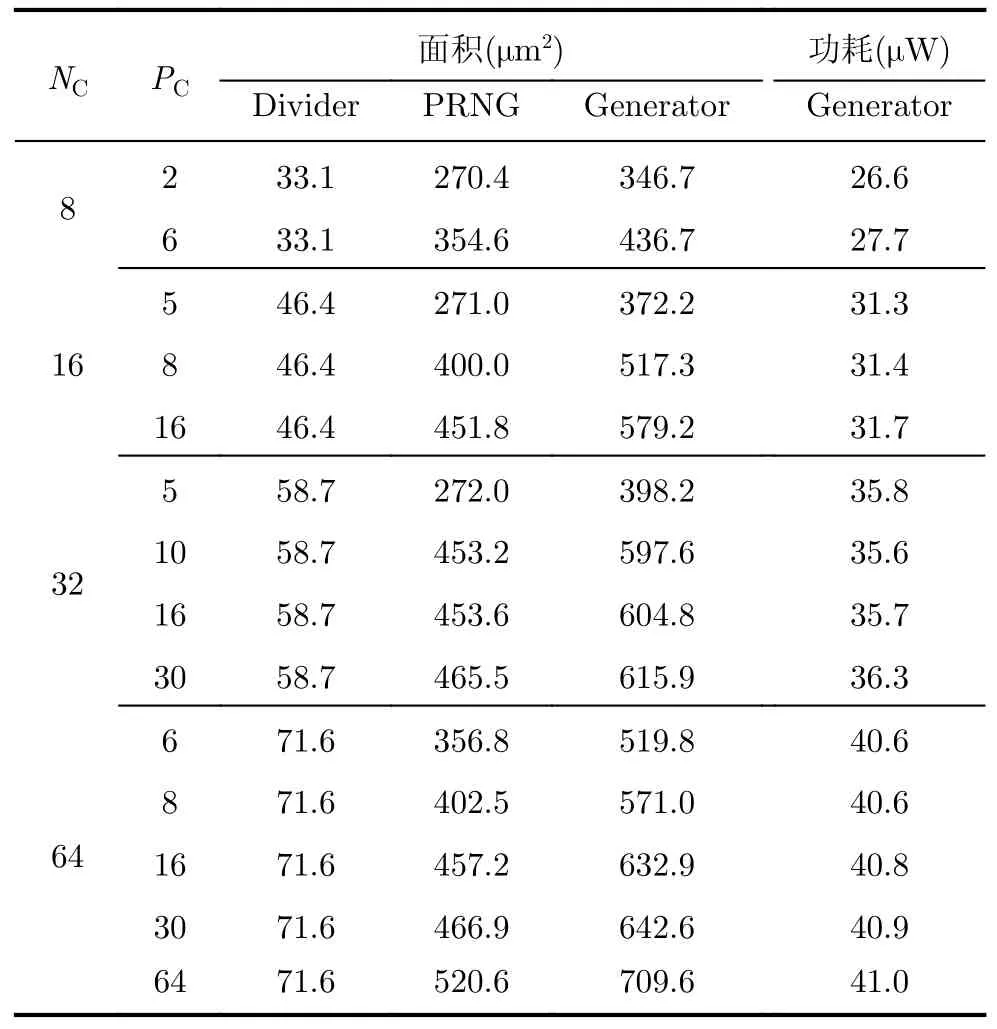

本文提出的隨機預充電使能發生器的兩個參數(NC,PC)均是可以配置的。本文對不同配置情況下的隨機預充電使能發生器的面積開銷和功耗開銷進行了分析,結果如表2所示。表2的第3~5列分別列出了分頻器Divider,隨機數發生器PRNG和隨機預充電使能發生器的頂層模塊Generator的面積開銷。從表中可以發現,3個模塊的面積都隨著NC的增加而增加,而只有PRNG和counter的面積隨著PC的增加而增加。在表2中最大面積開銷由最大配置參數對(NC,PC)=(64, 64)帶來。在此配置下,頂層模塊隨機預充電使能發生器的面積開銷為709.6 μm2,該面積僅為WDDL-ALU面積的4.6%。表2的第6列是隨機預充電使能發生器在不同配置下的功耗開銷。從表中可以發現,電路的功耗隨著NC,PC的增加輕微地上升。隨機預充電使能發生器所帶來的功耗僅在μW量級,而WDDL-ALU的功耗為mW量級。這意味著本文所提出的預充電使能技術是一個輕量級的解決方法,并且這種技術在不同架構的CPU中均有應用潛力。

表2 隨機預充電發生器的面積和功耗開銷

3.2 預充電使能指令技術

RISC-V指令集允許使用者進行自定義指令的擴展,它啟發我們設計新的指令來控制WDDL-ALU的預充電行為。RISC-V指令集支持的指令擴展方式主要有兩種:第1種是使用操作碼opcode在自定義空間(custom空間)進行指令拓展。例如Rocket芯核會將custom指令通過Rocket自定義協處理器接口發送到協處理器中進行處理,協處理器處理完成后會將結果返回Rocket核心內部。然而,這個方法不適用于預充電控制,因為WDDL-ALU模塊位于Rocket芯核內部,而不是作為協處理器掛載在其外部。第2種指令的拓展方法是使用操作碼opcode的保留空間(reserved空間)來定義全新的指令。此拓展方法需要修改硬件的每一級流水線來實現該新指令所定義的功能,同時還需要修改編譯器來支持該新指令,實現十分不便。

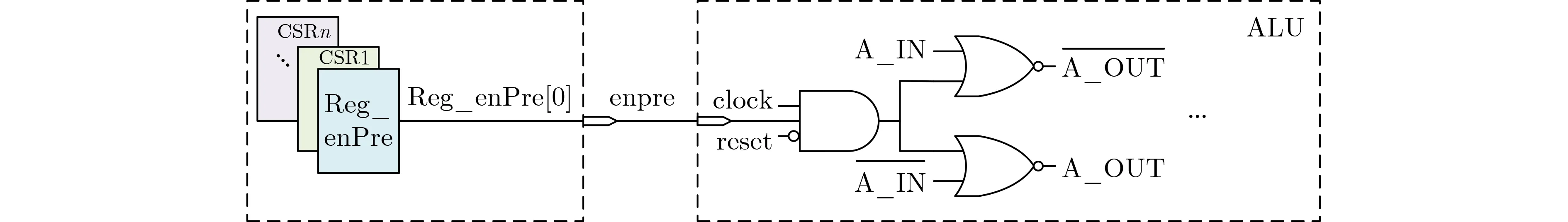

本文提出一種自定義指令擴展方法,該方法利用了RISC-V基本指令集中的CSR類指令。這一類指令提供了一個軟件和控制狀態寄存器(Control and Status Register, CSR)之間交互的接口。通過CSR指令,軟件可以控制和觀察CSR寄存器的狀態。RISC-V指令集架構規定地址空間0x000-0xFFF為控制狀態寄存器的地址空間,同時支持設計者在允許的地址空間內擴展新的CSR寄存器。本文首先在地址0x800處擴展了一個預充電使能CSR寄存器Reg_enPre,該地址被允許進行自定義讀寫操作。擴展CSR寄存器后,硬件的預充電行為可由Reg_enPre寄存器直接控制。此時預充電行為如圖7所示。使能信號enpre,即CSR寄存器Reg_enPre的第0 bit,控制WDDL-ALU預充電的開啟和關斷:當調用指令“csrwi 0x800, 0x1”將1寫入Reg_enPre時,會使ALU開啟預充電;當調用指令“csrwi 0x800,0x0”將0寫入Reg_enPre時,會使ALU關閉預充電。該寄存器Reg_enPre的位寬與Rokcet處理器芯核的通用寄存器位寬相同,都是64 bit,因此若有需求,可以使寄存器的每一位來控制不同模塊預充電的開啟和關閉。

圖7 預充電使能指令通過CSR Reg_enPre控制預充電

通過擴展CSR寄存器的實例和調用csrwi指令,對擴展后CSR寄存器狀態的控制相當于擴展了自定義的預充電使能指令,從而可達到由指令直接控制硬件預充電行為的目的。Rocket處理器芯核的流水線不需要修改。由于CSR指令已經是RISC-V指令集的標準指令,編譯器也不需要修改。以“csrwi addr, value”形式實現的預充電使能指令可以在匯編程序的任意位置調用,因此該指令理論上可以控制密碼算法程序的任意代碼段。在UMC 55 nm的工藝庫下,新擴展的CSR寄存器的面積僅有631.8 μm2,面積開銷幾乎可以忽略。只有當CSR中的數據發生翻轉時,該新擴展的CSR寄存器才會產生動態功耗,因此功耗開銷也可以忽略不計。

4 仿真和討論

4.1 仿真工具與流程

本文使用Design Compiler工具在UMC 55 nm工藝庫下對Rocket芯核的源碼進行綜合。得到網表后,使用VCS將Rocket門級網表和相關接口文件編譯,得到基于VCS的Rocket硬件仿真器。然后使用該硬件仿真器運行AES加密程序的可執行文件,得到波形文件。最后使用PrimeTimePX在time_based模式下對波形文件進行功耗分析,得到功耗跡線。具體流程如圖8所示。

圖8 功能仿真及功耗分析流程

4.2 實驗結果

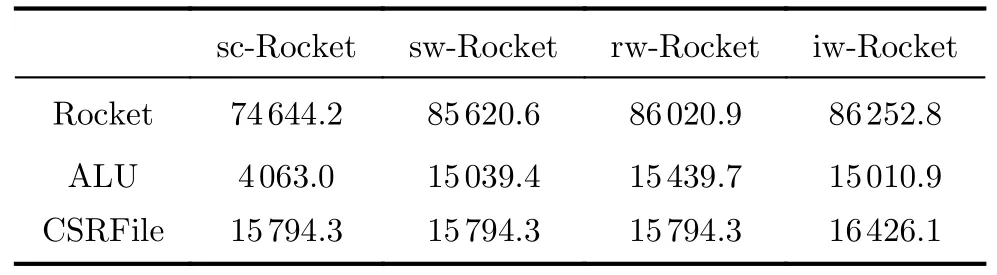

本文將第3節提出的兩種功耗抑制技術應用在不同的Rocket處理器芯核上進行仿真并分析結果。應用了隨機預充電使能技術的Rocket芯核稱為rw-Rocket (random based WDDL-ALU Rocket),而應用了預充電使能指令技術的Rocket芯核稱為iw-Rocket (instruction based WDDL-ALU Rocket)。對于rw-Rocket芯核,根據表2中各參數配置下隨機預充電使能發生器的面積和功耗開銷,選擇了參數對(NC,PC)=(32,5)進行配置以獲得平均水平。表3比較了不同Rocket芯核的面積開銷。與sw-Rocket芯核相比,rw-Rocket和iw-Rocket的面積分別只增加了0.5%和0.7%左右。

表3 不同Rocket核心的面積開銷(μm2)

用C語言編寫的AES-128加密程序分別運行在不同的Rocket芯核上。AES-128的密鑰長16 Byte,它每次只加密16 Byte長度的明文。對于在iw-Rocket芯核上運行的AES-128程序,需要在程序源碼中插入預充電使能指令。由于riscv-gcc內聯匯編的支持,可以直接在C語言代碼中插入“asm volatile (“csrwi 0x800, 0x1”)”和“asm volatile(“csrwi 0x800, 0x0”)”來控制預充電的開啟和關閉。文獻[8]對ARM核心的DPA攻擊是在AES-128算法的字節替換過程中進行的。因此本文以最易受到攻擊的字節替換代碼段為示例,在該程序段開始時開啟硬件預充電,當字節替換結束時關閉硬件預充電。

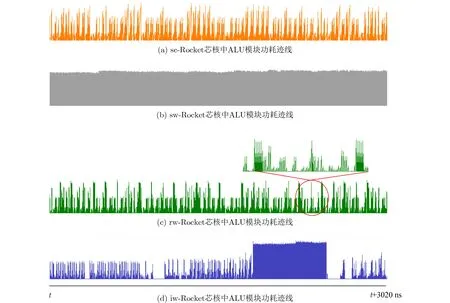

圖9顯示了不同的Rocket芯核運行AES-128程序時的ALU模塊功耗跡線。圖9(a)是sc-Rocket芯核中的ALU模塊功耗跡線。圖9(b)是sw-Rocket芯核中ALU模塊的功耗跡線。它表明在運行AES-128程序時,WDDL-ALU模塊的功耗在每個周期內幾乎相同。

圖9 AES-128程序運行在不同的Rocket芯核上ALU模塊部分功耗跡線

圖9(c)是rw-Rocket芯核的內部ALU模塊功耗跡線。隨機預充電使能技術已經把功耗跡線隨機化,并且破壞了AES算法的中間值和實時功耗之間的相關性。由于時間分辨率的原因,在圖9(c)的功耗跡線中所表現出的預充電行為并不明顯。但是放大其中的一段后可以發現,ALU模塊中的預充電行為已經由使能信號進行了隨機化控制。在使能信號有效期間,ALU模塊在進行預充電操作,硬件得到了功耗平均化方式的保護。而實際上,rw-Rocket芯核的抗DPA能力歸因于預充電的隨機性。根據式(1),參數NC越 大隨機性越好,因為NC決定了產生的隨機數Rp的上限;而參數PC越接近NC時隨機性越好。因為在NC一定時,PC決定了隨機數Rp的下限。也就是說,當NC越大,且PC越接近NC時,隨機數Rp的范圍越寬,從而可使預充電使能信號的隨機性越好。

圖9(d)是iw-Rocket芯核中ALU模塊的功耗跡線。預充電使能指令應用于字節替換程序段。從圖9(d)可以看出預充電的行為準確地發生在了字節替換的操作過程中,并且ALU模塊的功耗在AES-128程序的字節替換過程中始終保持相同。

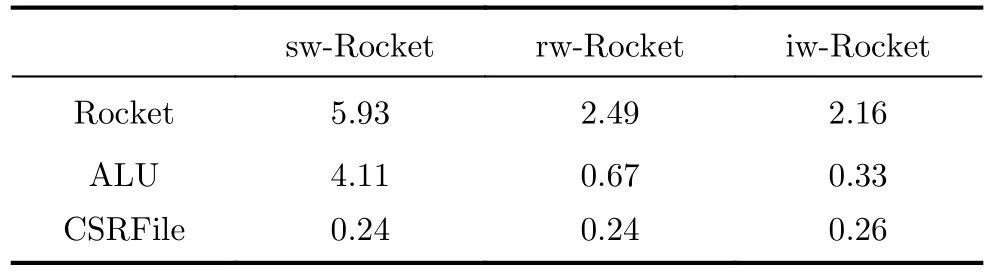

表4列出了AES-128程序運行在不同Rocket芯核上的功耗。rw-Rocket芯核中ALU模塊的功耗約為sw-Rocket芯核中ALU功耗的16%,而整個rw-Rocket芯核的功耗是sw-Rocket功耗的42%。iw-Rocket核心中ALU模塊的功耗只有sw-Rocket芯核中ALU功耗的8%,整個iw-Rocket芯核的功耗是sw-Rocket功耗的36.4%。這表明提出的兩種技術都能夠抑制使用了WDDL-ALU的Rocket芯核的功耗。

表4 不同Rocket核心運行AES-128程序的功耗開銷(mW)

在rw-Rocket芯核和iw-Rocket芯核上運行AES-128程序的功耗分別為2.49 mW和2.16 mW,相比于sc-Rocket的功耗分別上升了28.3%和11.3%。但是,在可接受的電路功耗開銷下,RISC-V處理器芯核防御DPA攻擊的能力得到了明顯增強。

4.3 優勢與不足

本文提出隨機預充電使能技術和預充電使能指令技術具有兩大明顯的優勢。其一是對任意加密算法都具有通用性。應用了隨機預充電使能技術的rw-Rocket芯核和應用了預充電使能指令技術的iw-Rocket芯核理論上可以對所有加密算法提供抗DPA攻擊的保護。當使用rw-Rocket芯核時,密碼算法的源碼完全不需要修改;當使用iw-Rocket芯核時,可以在源碼中插入自定義的預充電使能指令來精確地保護關鍵的程序段。相比于文獻[17]中使用的僅對AES算法提供保護的協處理器方案,本文提出的兩種方法對密碼算法具有通用性。本文方法的另一大優勢在于較高的安全性。文獻[16]中使用插入隨機延時的方法。但是由于彈性對齊算法和機器學習的引入,DPA攻擊也可以對非對齊的功耗跡線產生威脅。因此該方案存在被攻破的風險。而文獻[9]中曾使用了掩碼的方案來防御DPA攻擊,但是該方案只能防御一階的DPA攻擊。高階的DPA攻擊可以對多個采樣點進行聯合分析,從而破解掩碼的作用。本文提出的兩種方案都是基于安全的邏輯單元WDDL,它從根本上改變了電路運行時的功耗特征,從而阻斷了信息泄露的途徑。因此本方案能夠有效地防御使用了彈性對齊算法的DPA攻擊以及高階的DPA攻擊,具有較高的安全性。

同時本文也存在一些不足之處。用WDDL邏輯單元將ALU模塊的CMOS單元替換后會增加關鍵路徑的延時,從而降低處理器的性能。但是從仿真結果來看,在可接受的性能開銷范圍內,處理器防御DPA攻擊的能力得到了明顯增強。目前我們針對兩種方案的安全性驗證都是基于實驗原理以及仿真結果的,未能在流片后的芯片上進行DPA攻擊。后續我們將在條件允許的情況下進一步完善這方面的工作。

5 結束語

本文針對基于WDDL-ALU的抗DPA攻擊的RISC-V處理器芯核提出了兩種功耗抑制方法。隨機預充電使能技術與CPU架構無關,它通過隨機化預充電的行為改善了RISC-V芯核的抗DPA攻擊能力。預充電信號的隨機性由隨機預充電使能產生器的參數對(NC,PC)共同控制。預充電使能指令技術使用了一種新的指令拓展方法,它不需要對處理器的硬件以及編譯器進行修改。這個方法也是通過控制WDDL預充電的行為來保護RISC-V芯核。該方法的靈活性在于它是通過重用CSR指令來實現的,而且新的預充電控制指令可以在程序的任何地方調用。仿真結果表明,本文提出的兩種技術都能夠保護RISC-V芯核免受DPA攻擊。在本文的AES-128程序仿真中,隨機預充電使能技術和預充電使能指令技術分別把rw-Rocket和iw-Rocket中ALU模塊的功耗降低到了sw-Rocket芯核中ALU模塊功耗的16%和8%,rw-Rocket芯核和iw-Rocket芯核的整體功耗分別降低至sw-Rocket芯核功耗的42%和36.4%。這兩種技術都是輕量級的解決方案,因為功耗和面積開銷相比基于WDDL-ALU的Rocket芯核只略有增加。這兩種技術使WDDL成為RISCV芯核抵抗DPA攻擊的實用方法,因為與原始的RISC-V芯核相比,其功耗只分別增加了28.3%和11.3%。