應用于CMOS圖像傳感器的高速全差分兩步式ADC設計方法

郭仲杰 王楊樂 許睿明 劉綏陽

(西安理工大學 西安 710048)

1 引言

CMOS圖像傳感器(CMOS Image Sensor,CIS)由于其高集成度、低成本以及低功耗的優點,在人工視覺和航天領域等應用場景下,占據了大規模的市場并越來越不可替代。目前限制CIS曝光速度的處理都落在了讀出信號處理部分,而模數轉換器(Analog-to-Digital Converter, ADC)又是CIS讀出電路的重要組成部分,是CIS性能提高的關鍵。近年來對于應用于CIS領域ADC的研究,涉及了大量不同的ADC拓撲結構,例如流水線型ADC[1]、循環型ADC[2]、σ-δ型ADC[3]、逐次逼近型ADC[4]、單斜式ADC(Single-Slope ADC, SS ADC)[5]以及基于上述ADC架構的各種組合等。但考慮到功耗、面積和速度的折中關系,并非每一種ADC架構都能在CIS中得到有效應用。

SS ADC主要由比較器、數字邏輯控制單元、計數器以及被所有列電路共享的斜坡信號發生器構成,相較于以上其他類型的ADC具有更好的面積和功耗優勢,同時也相對容易地保證列之間的一致性,從而使列固定模式噪聲(Fixed Pattern Noise,FPN)最小化,因此創新和發展出更快速的SS ADC架構已成為目前CIS領域主流的研究方向[6–10]。由于SS ADC特有的轉換速率與轉換精度之間呈指數型相關的量化方式,目前對SS ADC的研究,主要集中在如何在保證同等量化精度的前提下,創新出能打破速度瓶頸的量化模式。目前的前沿研究進展如串行兩步式SS ADC,將整個量化過程分為在時間上串行的A bit粗量化與B bit細量化,將完成一次模數轉換所需的2(A+B)個量化周期拆解為了2A和2B量化周期的和,節省了部分時間;全并行兩步式SS ADC,將整個量化過程分為在時間上并行的A bit粗量化B bit與細量化,由于時間上的并行原理,完成一次模數轉換將只需要MAX(2A,2B)個時鐘周期;以時間數字轉換(Time-to-Digital Conversion,TDC)技術為依托的SS ADC等,然而目前對于高幀頻CIS的研究仍存在較大的瓶頸,在ADC研究進展仍有較大的速度提升空間[11–15]。

本文在傳統兩步式SS ADC的基礎上,提出了一種應用于CIS的高速全差分兩步式ADC結構,在保證SS ADC的功耗和面積優勢的前提下,以將差動量化嵌套在兩步式的思想,完成更高速量化。另外在ADC中引入基于電平編碼的TDC技術,在ADC量化的最后一個時鐘周期,以不犧牲動態功耗為前提,完成更高速的量化,從而實現高速的兩步式量化過程。本文著重分析了該兩步式ADC設計思想,并在實驗平臺進行了電路搭建和全面的參數測試。

2 CIS系統架構研究

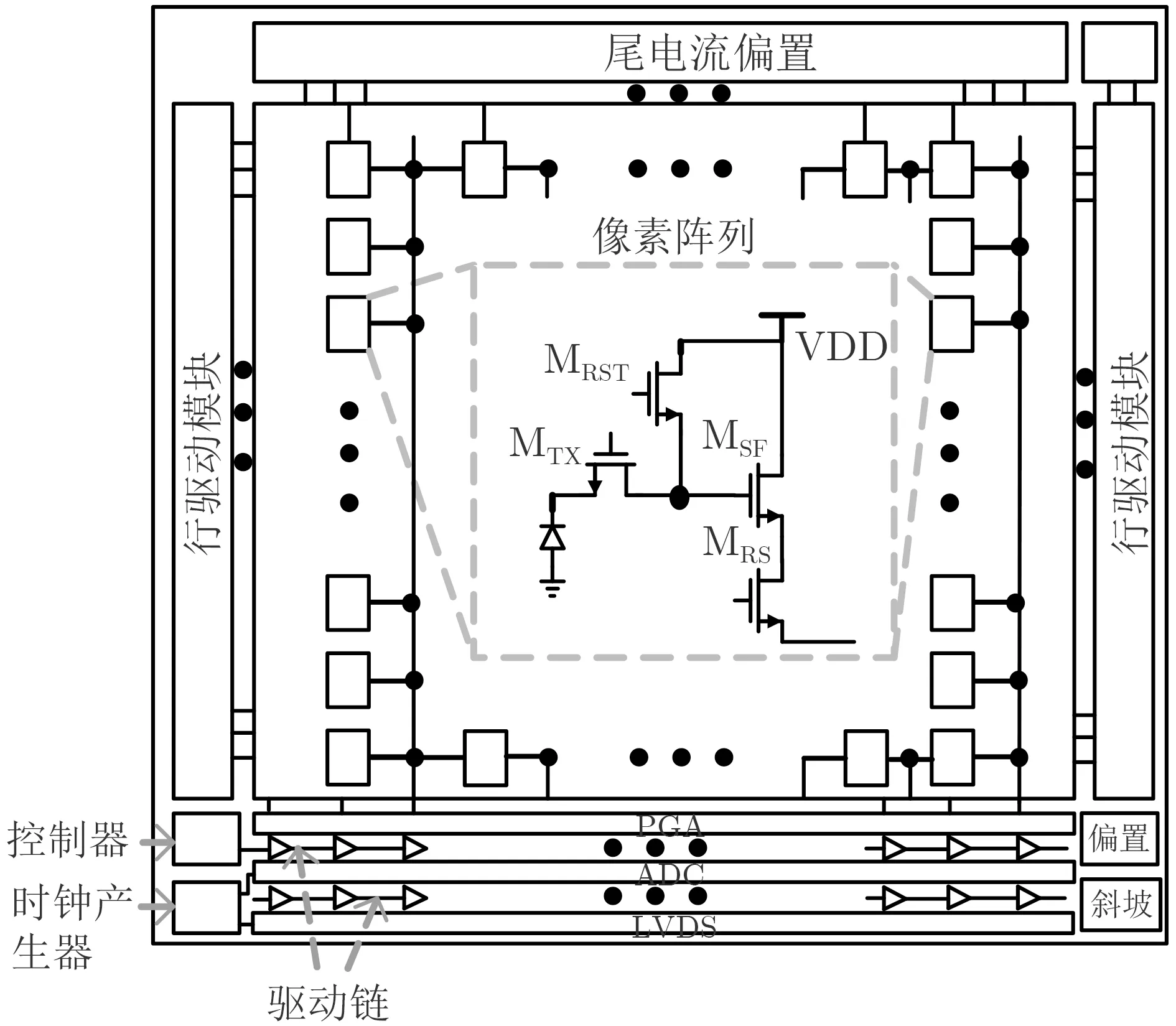

CIS的整體架構如圖1所示:包括尺寸規格M×N的像素單元、列偏置模塊、行驅動模塊、控制器、讀出電路、時鐘信號產生電路以及各個模塊的信號驅動電路。其中像素單元完成光信號到電信號的轉換過程,由讀出電路將得到的電信號進行采樣、放大、量化過程,時鐘信號產生電路和控制器以及列偏置模塊、行驅動模塊為像素單元和讀出電路提供時序控制和模擬偏置,共同完成圖像的處理和讀出[16–20]。

圖1 CMOS圖像傳感器系統框架示意圖

不論是目前CIS主流的全局曝光模式還是卷簾曝光模式,目前對曝光速度的限制均落在了電信號的讀出量化階段,而ADC又是約束信號量化處理的關鍵一環。因而為了保證較高的幀率,需要較高的ADC采樣率;同時為了保證成像的質量,又必須保證較高的ADC精度[15,21–24]。因此在CIS的逐行讀出下,列級ADC的轉換時間則成為像素信號讀出的最大限制,式(1)展示了幀頻與列級ADC的轉換時間的關系

其中,f為幀頻,T為列級ADC量化一行所需要的時間,R為像素行數。

SS ADC系本身的量化方式,每提高1 bit的轉換精度,其速度將以指數形式進行衰退,因此提升單斜式AD轉換技術的核心主要集中在結構的優化創新,并且將會是CIS后續發展的一個突破方向。

3 高速全差分兩步精度擴展式ADC設計思想

系SS ADC本身的量化速度存在的缺陷,目前對應用于大幀頻CIS高速SS ADC研究歷程由串行量化向并行量化方向的拓展,這種時間并行的思想,將是打破速度瓶頸的關鍵。而目前對于SS ADC并行量化的最新研究動態,其時間并行的效率并不顯著,有且僅有33%[24]。而本文提出的全差分兩步式設計思想,在時間上的并行利用率達到了50%,為高幀頻CIS的實現提供了切實可行的理論基礎和實現方案。

對于全差分兩步式SS ADC的量化過程,總共分為兩個步驟:(1) 模擬時間轉換(Analog-to-Time Conversion, ATC);(2) 時間數字轉換。在本文全差分的電路架構中,該結構在整個動態范圍下能識別的最小電壓值是一個時鐘周期內斜坡信號的變量。如果將斜坡比作一把標尺,斜坡上產生的變量就是這把標尺的分度值。因此,可以將斜坡信號等效為對斜坡信號增量或者減量求和產生的等效上升斜坡Vra1或等效下降斜坡Vra2。從ATC的角度分析,比較器會直接將輸入信號在斜坡信號上時間關系映射出來,完成模擬信號到時間信號的轉變。從TDC的角度分析,比較器之后的數字計數邏輯會把這段時間關系映射出來,完成時間信號到數字信號的轉變。

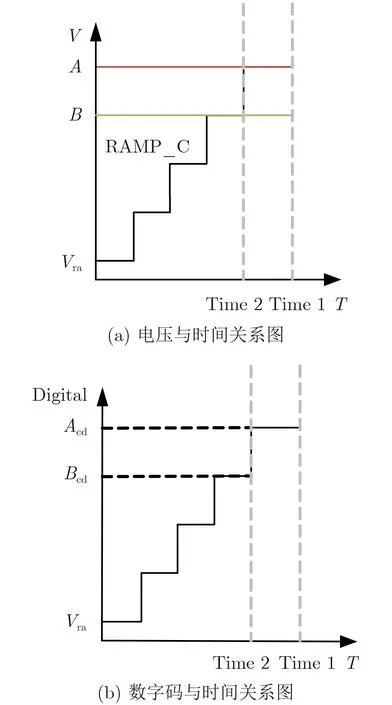

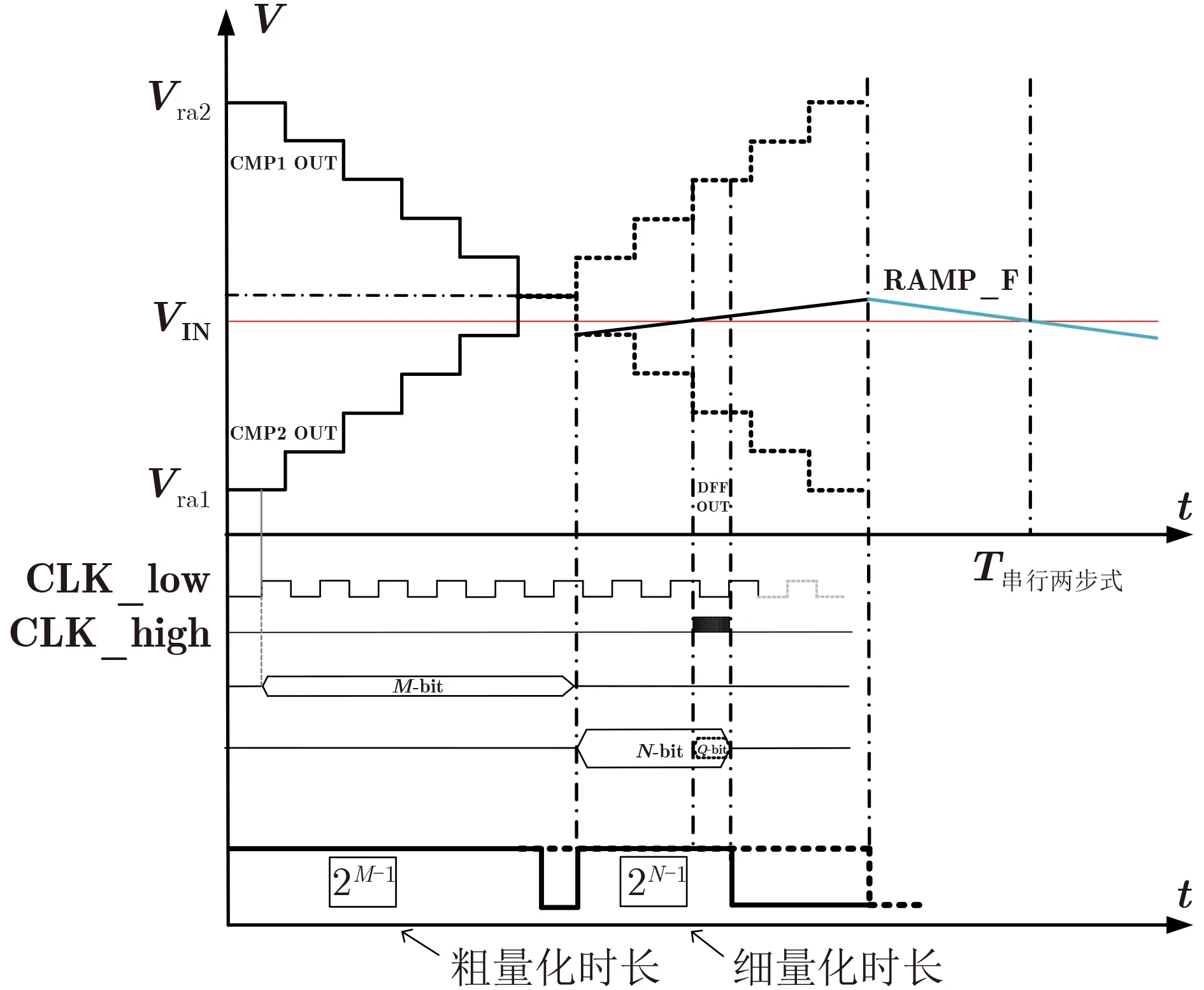

圖2為兩步式SS ADC正常量化示意圖,每個輸入斜坡臺階值與數字計數邏輯一一對應,具體到M bit的粗量化而言,分為2M個粗臺階,每個粗臺階的量化時間對應一個時鐘周期TCLK,所以完成粗量化需要的時間為

圖2 兩步式SS ADC量化示意圖

由于差動粗斜坡的引入,每個粗臺階的量化時間仍然為TCLK,不同的是,粗量化的動態范圍被一分為二,此時一半的粗量化時間變成了冗余時間,最終完成粗量化所需要的時間為

值得說明的是,對于細量化而言,必須使用在粗量化中觸發的相同比較器。因此,細相位僅使用單比較器。這意味細量化將使用全斜坡擺動。就N bit細量化而言,RAMP_F被劃分為2N個步長。 每個細量化步驟的轉換時間對應于一個時鐘周期TCLK,因此,完成細轉換所需的時間為

考慮到一般情況,完成一次嵌套差動斜坡的兩步式量化,假設有M bit的粗量化和N bit的細量化,最終完成一般兩步式粗細量化所需要的時間為

本文將全差分的思想引入兩步式SS ADC的實際量化中,在某種程度上類似于時間交織技術,將粗斜坡和細斜坡的量化時間作完全并行處理,由此進行時間共享,將串行的量化模式改進為并行量化模式,大大提高了時間利用率,達到高速量化的目的。由于SS ADC的轉換時間依托轉換精度是以指數倍衰減,所以這種量化機制在精度越高的情況下,速度收益越明顯。這是本文對于速度提升做出的第一個創新。

本文提出的全差分兩步式量化模式帶來的有益效果是:(1) 形成了區別于串行量化的并行量化模式,同時由于差動斜坡的存在,保證了系統的一致性和魯棒性。(2) 相較于傳統兩步式SS ADC該結構帶來50%以上的速度收益,且這種速度收益在越高精度量化過程中越明顯。

4 低功耗電平編碼TDC設計方法

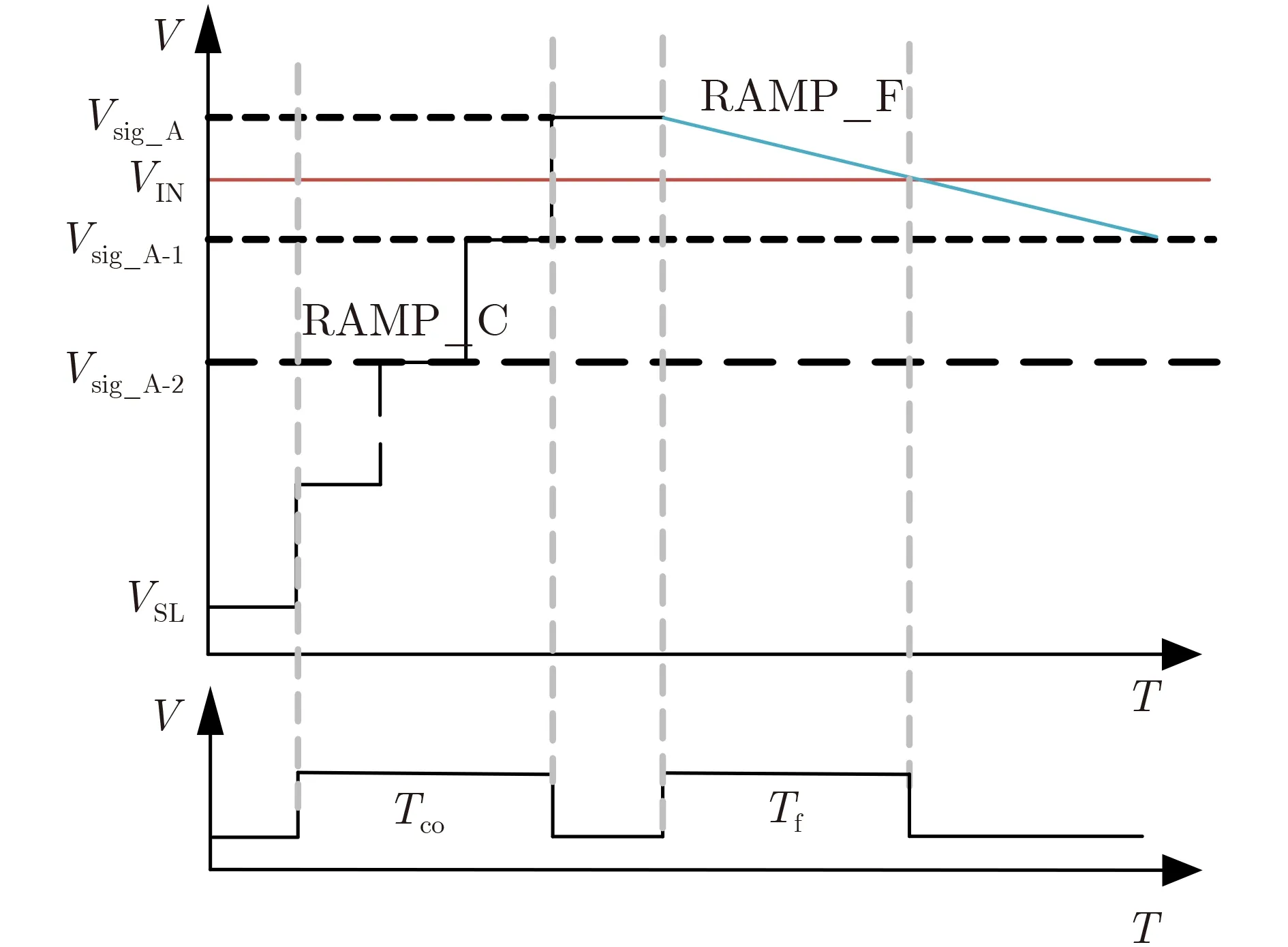

如圖3所示,兩個待轉換的模擬信號A和B展示了一種邊界量化情況,在分辨率的制約下,輸入信號A和B之間形成了具有相同數字輸出的模擬信號區間:若待測信號大于待轉換模擬電壓B,則ADC的數字輸出會增加一個單位;若待測信號小于待轉換模擬電壓A,則ADC的數字輸出會減少一個單位;當待測信號處于AB的信號區間內,要想得到更高精度的量化結果,一種方法是全局范圍內采用更高頻率的時鐘以此縮短ADC的單次量化時間范圍;另一種方法是在局部使用更精確的量化,即在信號所在的時鐘周期內,利用更高精度的時間數字轉換器量化該信號與Time2的時間差值,即TDC。由于在ATC時利用了比較器判別了輸入信號在斜坡信號上的時間尺度,在TDC時又利用更高精度的時間數字轉換器衡量了比較器翻轉時刻與當前時鐘周期結束時刻的時間尺度,最終得到的時間信號都將通過數字計數邏輯整合得到理想的數字碼。在此基礎上,就需要著重考慮ATC與TDC的匹配性問題[15,25,26]。

圖3 時間差值量化示意圖

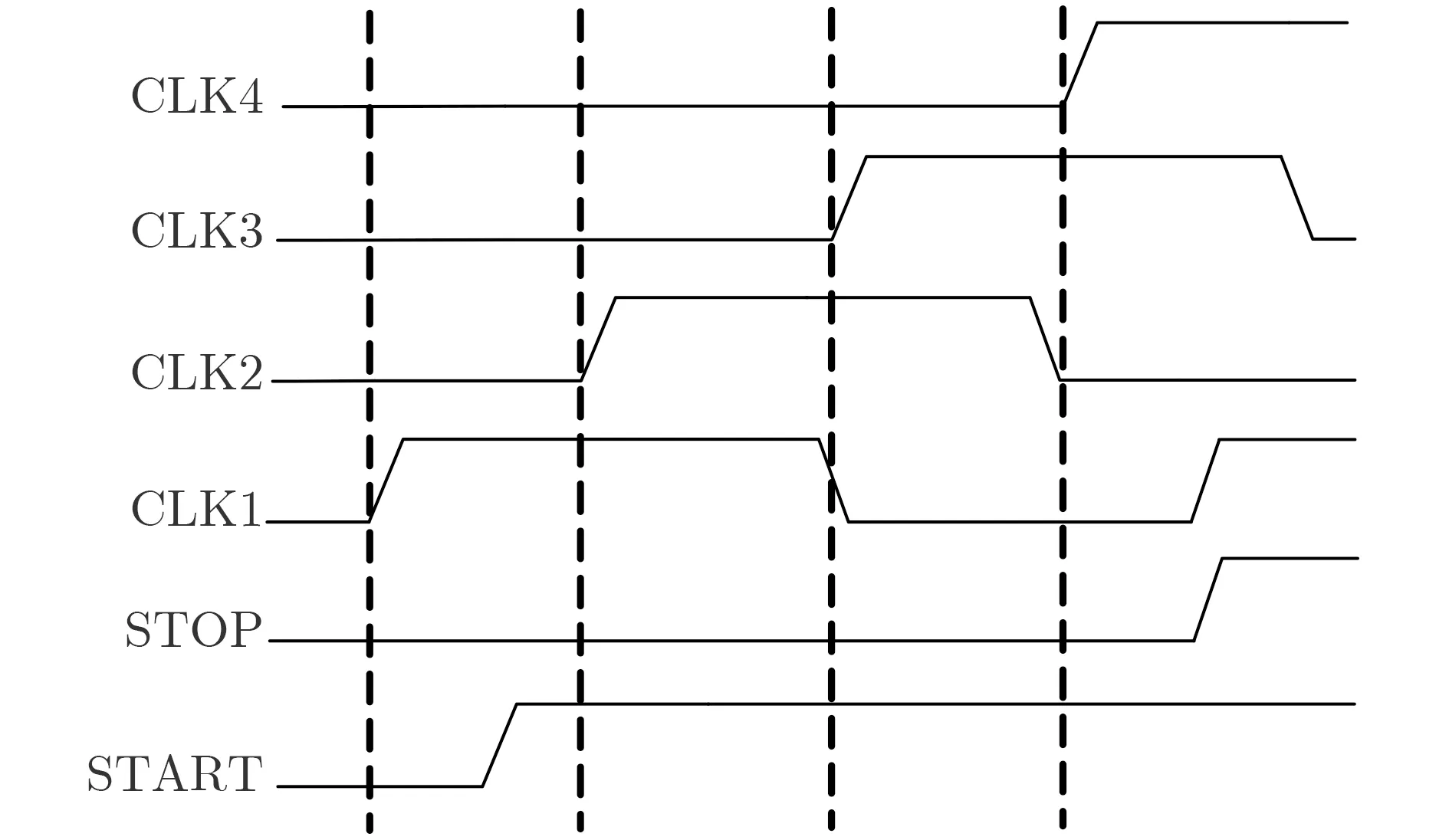

傳統TDC的編碼方式如圖4所示。在這種編碼邏輯下,隨著4相時鐘的依次到來,時鐘對應的4個觸發器依次觸發,在CLK1~CLK4時鐘沿到來的不同時刻,觸發器的輸出對應一一翻轉,從而通過這種沿觸發的方式,產生不同的輸出結果,再通過編碼器對不同的輸出結果進行編碼,得到00~11的2 bit二進制數字轉換結果。

圖4 傳統時鐘壓縮型TDC編碼原理示意圖

這種技術的TDC通過D觸發器特有的沿觸發方式來進行編碼,若要完成2 bit的時間數字轉換功能需要延遲鎖相環(Delay phase-Locked Loop,DLL)配備嚴格的4相時鐘,由于DLL的壓控延遲鏈需要通過反饋的方式來產生穩定且具有相關性的4相時鐘,但是由于非理想因素會導致的時鐘抖動問題,在四相時鐘下會表現的更加明顯且不可控[27]。這種模式下的TDC會使得ADC量化的精度和速度都大幅度下降,實際轉換效果并不理想。

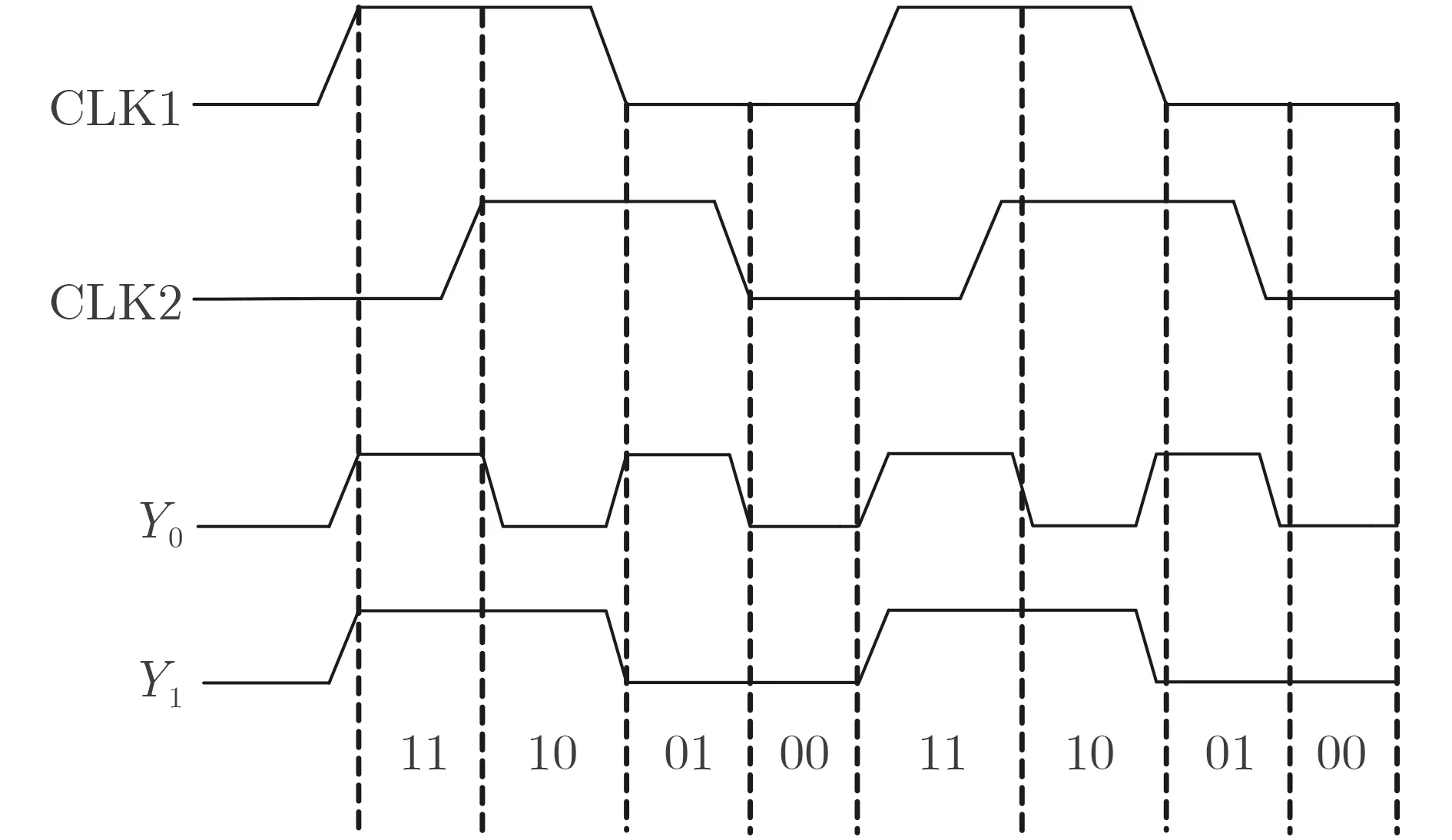

本文提出的電平編碼原理如圖5所示。由DLL提供兩項時鐘CLK1和CLK2,利用這兩項時鐘的相位差,在一個時鐘周期內的不同量化時刻,CLK1和CLK2對應有不同的高低電平組合,再通過D觸發器和基本邏輯門組成的電平編碼電路進行編碼,在1個時鐘周期內,輸出00~11的2 bit二進制數字轉換結果Y0和Y1。

圖5 本文TDC電平編碼原理示意圖

通過TDC的編碼器將延DLL產生的多相時鐘信號進行編碼后,再通過D觸發器(由于是沿觸發的特性),將比較器的翻轉判定時間同時作為TDC的START信號,最后將2 bit TDC輸出的00~11的低2位數字碼與計數器數字碼進行整合,將ATC和TDC完成最終的匹配。

由于差動斜坡架構并不能將時間的利用率提高到極致,基于以上的工作,不難發現,SS ADC的轉換時間還受到時鐘頻率的影響,在ADC的數字邏輯模塊,做有計數器模塊,是通過時鐘沿觸發來進行計數的。這并不能說時鐘頻率越快越好,因為系ADC的模擬電路部分,ADC對高頻時鐘的耐受度也會有限制,A/D轉換的最后一位數字碼的讀出靠時鐘沿來控制,這也就是說,在比較器完成輸入信號與斜坡信號判決之后,并不能馬上完成數字碼的輸出,還需要等待下一個時鐘沿的到來。因此,本文將利用這段時間差,將TDC技術插入于ADC中,進一步提高時間的利用率,在與兩步式ADC相同的量化精度下,TDC將完成更高精度的模擬值逼近,本文設計了2 bit的TDC精度,將速度提升對時間的指數衰減降低2 bit,所以這也是本文對于速度提升做出的第2個創新。

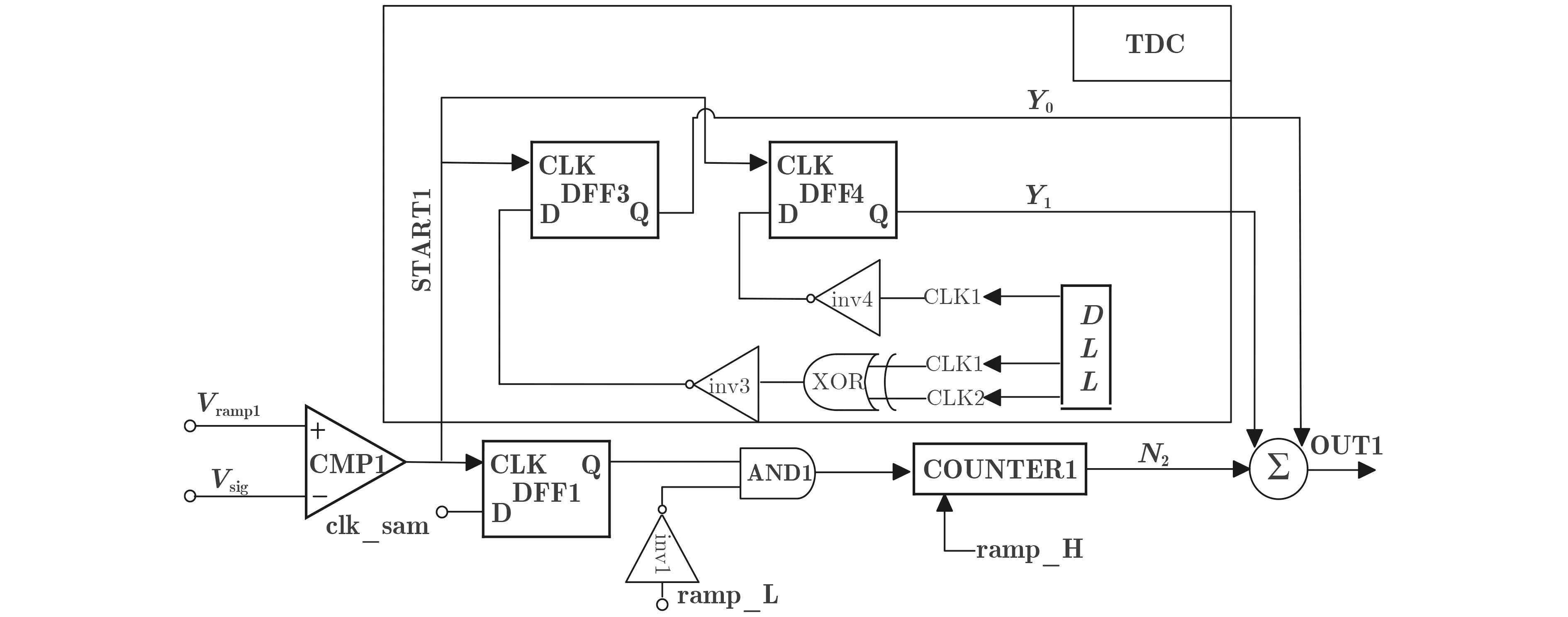

基于單斜式與電平編碼TDC電路結構示意圖如圖6所示,該電路帶來的有益效果如下:

圖6 基于單斜式與電平編碼TDC電路結構示意圖

(1)該結構只需要DLL提供兩項時鐘,利用兩項時鐘的電平進行數字編碼,在這種編碼方式下,更有效地釋放了TDC對DLL的需求,同時改善了DLL的時鐘抖動造成量化精度不高的問題。

(2)傳統的沿編碼需要復雜的編碼邏輯,而本文提出的TDC結構編碼方式較為簡單,這種簡單的編碼結構降低了ADC數字模塊的動態功耗,這在大面陣CIS的應用中顯得尤為顯著。

(3)待轉換信號輸入到達輸出的延遲更小,量化速度更快。可以在保證量化精度的同時,完成時間-數字的高速轉換過程,為打破SS ADC的速度瓶頸提供了有效的解決方案。

5 12 bit模數轉換器詳細設計

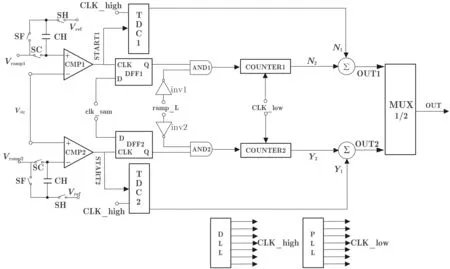

本文將全差分的并行量化思想與以電平編碼為依托的TDC技術相結合,提出了高速全差分兩步式SS ADC。如圖7所示,將12 bit模數轉換的量化過程拆解為了5 bit粗量化、5 bit細量化以及2 bit TDC量化過程。

圖7 基于差動斜坡與TDC的ADC結構示意圖

該電路由全差分形式的采樣電路、比較器、TDC以及數字計數邏輯組成,最終由數據選擇器來完成轉換結果的輸出。其中數字計數邏輯所采用的低頻時鐘由鎖相環(Phase-Locked Loop, PLL)提供,TDC所采用的等效高頻時鐘由DLL提供。斜坡發生器產生差分形式的斜坡信號Vra1和Vra2以及光電轉換信號Vsig從采樣電路完成系統輸入。本文實現差動斜坡并行的架構,“差動”的思想也是模擬設計很重要的一環,對于差動的電路設計,在對匹配性方面可以做到更好,這在CMOS圖像傳感器中,無論是版圖匹配性還是ADC的穩定性方面,都能得到更好的體現。

先進行粗量化,在開關電容控制電路中,控制開關SC和SH為導通狀態,此時Vra1和Vra2為差動形式的粗斜坡電壓,從初始值開始,步進到粗斜坡電壓的滿擺幅電壓VFS,每一次的步進值為粗斜坡電壓的一個臺階值ΔC。比較器對斜坡輸入信號和待量化信號Vsig進行比較,粗斜坡電壓每步進增加ΔC,比較器便會比較1次,若經過m次步進,比較器的輸出變為高電平,則表明輸入信號為

在這個粗量化區間內,就找到了Vsig所在的粗量化區間,此時關斷開關SH,電容CH就存儲了此時的粗斜坡電壓值(m+1)ΔC,電容CH的上下極板電壓差為(m+1)ΔC–Vref,Vref為一固定電平。粗斜坡電壓步進到滿擺幅電壓VFS之后,開關SC關斷,粗量化過程結束。

然后進行細量化操作,此時在開關電容電路中,開關SF為導通狀態,Vra1和Vra2此時為差動形式的細斜坡電壓,定義為VR,接到開關電容電路中電容CH的下極板,由于電容CH存儲了之前的粗斜坡電壓值(m+1)ΔC,則比較器的斜坡輸入端電壓值VC為VR+(m+1)ΔC,細斜坡電壓VR從–ΔC步進變化到Vref,每一次的步進值為細斜坡電壓的一個臺階值ΔF。VC就從mΔC變化到(m+1)ΔC,即對VIN所在的粗量化區間進行細量化。比較器對VC和待量化信號Vsig進行比較,若細斜坡電壓VR經過n次步進,比較器的輸出變為高電平,則表明輸入信號為

最后進行2 bit的TDC過程,細量化的結束信號作為TDC的開始信號,此時的細斜坡計數器的低頻時鐘的時鐘沿作為TDC的結束信號,通過周期性的編碼過程,完成可配置在SS ADC中的可循環式的編碼,TDC編碼所需要的等效高頻時鐘由DLL提供。同時為了具備較強的調整空間,計數器采用簡單的鏈式結構,底層觸發器采取同步可復位及置位的D觸發器,設計復位權重高于置位,配合與非門電路實現初值可配的計數器設計。緊接著,通過將初值置為–1,將省去細量化計數結果減去TDC計數結果這一過程,而實際的計數變為了粗細量化的計數結果作為高10 bit位數字碼,而將TDC的反碼直接作為低2 bit位數字碼,直接完成12 bit的模數轉換結果,使得列級ADC電路省去了減法器電路的面積和功耗開銷。

最終,在這個細量化區間內,1個完整的量化周期結束。

對于本文的并行量化模式,類似時間交織的形式,對于粗量化而言,差動雙斜坡在時間上同步進行,比較器CMP1和CMP2同時開始工作,通過時序的整合,在兩步式的基礎上,將時間的利用率提高了50%,在SS ADC本身速度與精度呈現指數衰減的情況下,將并行引入在兩步式的量化過程中,所以并行模式才是本文設計的核心思想之一。

基于差動斜坡與TDC的ADC電路工作時序如圖8所示,回歸一般情況,差動斜坡為M bit粗斜坡與N bit細斜坡組成,TDC為Q bit,在保證總的量化精度為(M+N+Q) bit的前提下,最終的實際量化時間僅為2M–1+2N,相較于上述傳統兩步式ADC而言,可以完成更高速的量化,為高幀頻大面陣的CMOS圖像傳感器實現提供了有效的解決方案。

圖8 基于差動斜坡與TDC的ADC電路工作時序圖

6 驗證結果與數據分析

本文基于55 nm 1P4M CMOS工藝,完成了基于差動斜坡與TDC技術的高速全差分兩步式ADC的具體電路設計與物理版圖實現,并成功應用于一款6 400萬像素的讀出電路芯片,如圖9所示為全芯片的實際照片。其中,ADC量化精度為12 bit,模擬和數字電源分別為3.3 V和1.2 V,時鐘信號頻率100 MHz。為了充分驗證本文所提方法的先進性和可行性,本次設計面向8 192×8 192規模的CMOS圖像傳感器的驗證平臺進行了性能參數測試和數據分析。

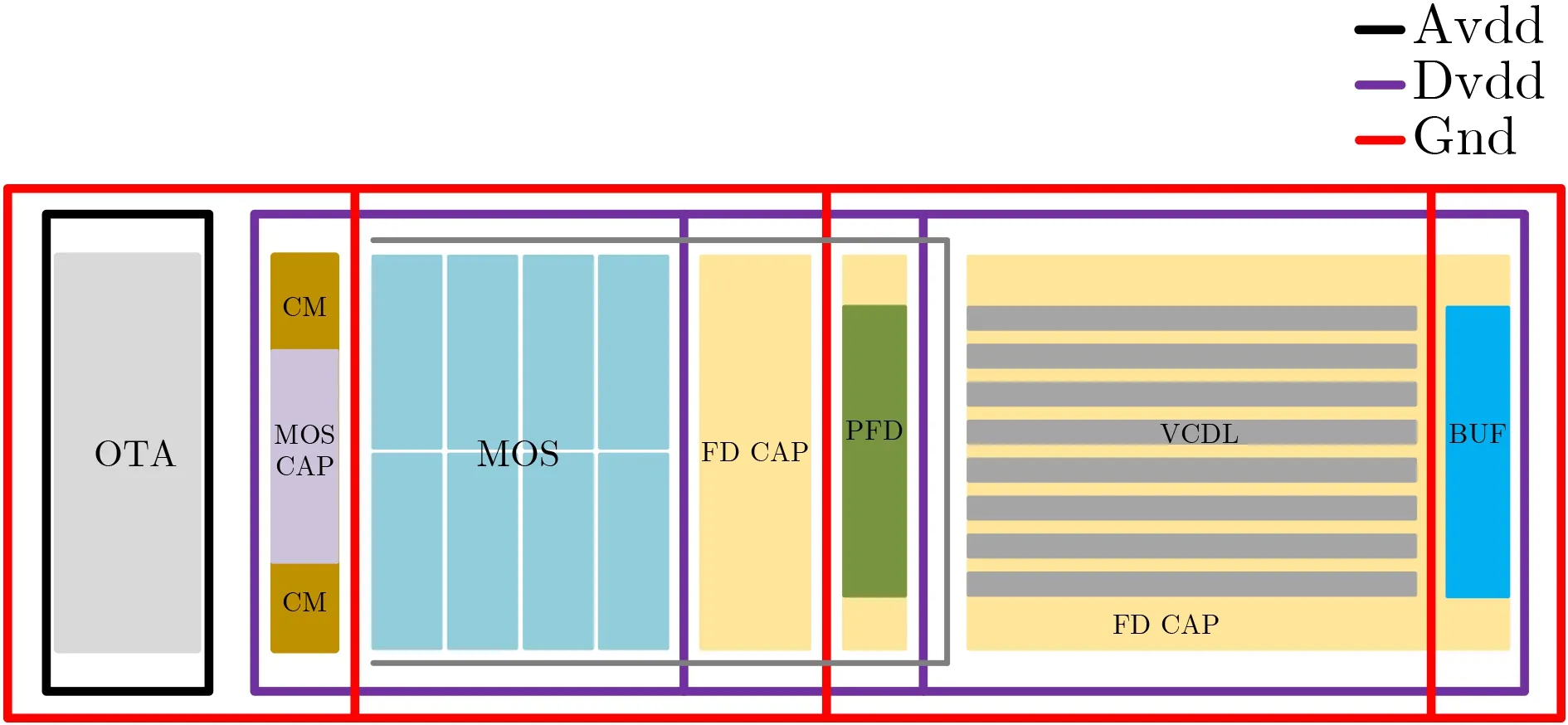

模擬和數字單元組成的各功能電路拼接得到的列復用單元如圖10所示,模擬模塊與數字模塊采用組格式分別向各單元供電,在縱向空隙設置了大量FD電容保證電源對數字噪聲的抵抗能力,數字電路與模擬電路采用分離設計與獨立襯底的設計方式,避免數字噪聲的串擾。

圖10 ADC整體版圖設計

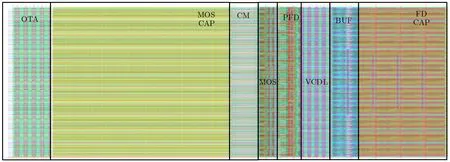

考慮到實際應用情況,本文版圖的設計面向8 192列大面陣CIS的應用。由于復用的設計特性,其信號傳輸路徑與接口信息均與復用單元保持一致。模擬偏置信號經由預留的布線通道向面陣內所有列電路提供偏置,除電流偏置采用每個復用單元獨立設置的方式外,其余模擬信號均由列電路共用。電流偏置通道與模擬信號通道采用分離設計,利用8 192路電路線獨立的向每一個復用單元提供偏置。所有數字信號通過復用單元內設計的驅動單元構成面陣級驅動鏈,向所有列電路提供控制信號。信號在驅動鏈內的延遲約為10 ps,遠小于系統時鐘周期。由于TDC所需的2相時鐘在陣列傳遞中與時鐘信號具有相似的傳遞路徑,依然能保證TDC過程中利用多相時鐘對固定時鐘周期的區間劃分。且ADC的每一功能電路均受到時鐘信號的約束。因此在8 192級規模的信號延遲下。ADC陣列的任一列的控制信號均具有對時鐘信號的一致性。基于該設計原理下的ADC陣列,對于控制信號的延遲具有較高的寬容性。由于復用的設計特性,1 024陣列的各項性能均與列復用單元存在一致性,ADC整體版圖如圖11。

圖11 ADC整體版圖

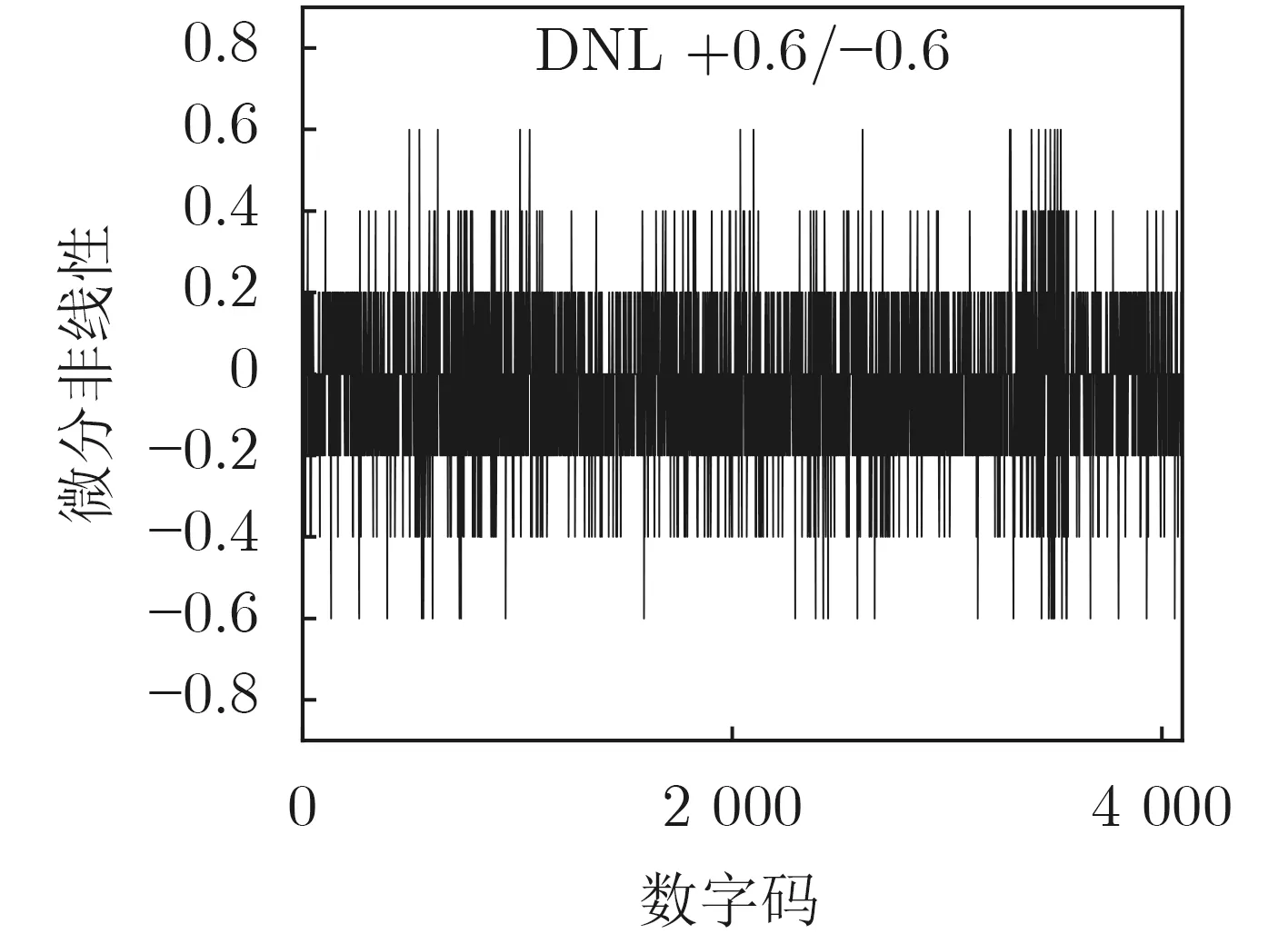

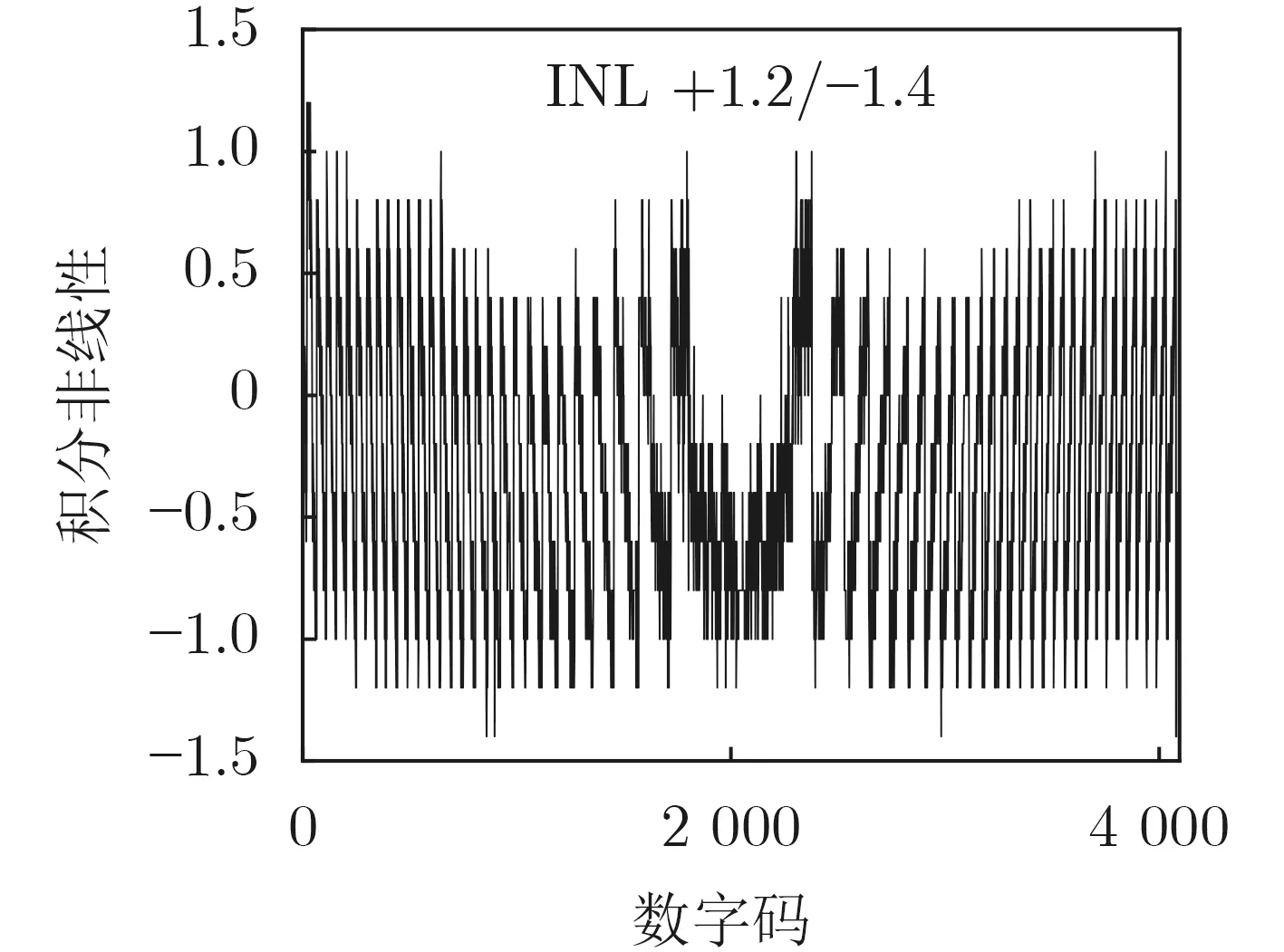

圖12和圖13為本實驗靜態仿真測試結果,以0.2LSB觀測精度進行測試,得到的微分非線性(Differential NonLinearity, DNL)如圖12所示;積分非線性(Integral NonLinearity, INL)如圖13所示:DNL為+0.6/–0.6, INL為+1.2/–1.4。

圖12 微分非線性(DNL)測試結果

圖13 積分非線性(INL)測試結果

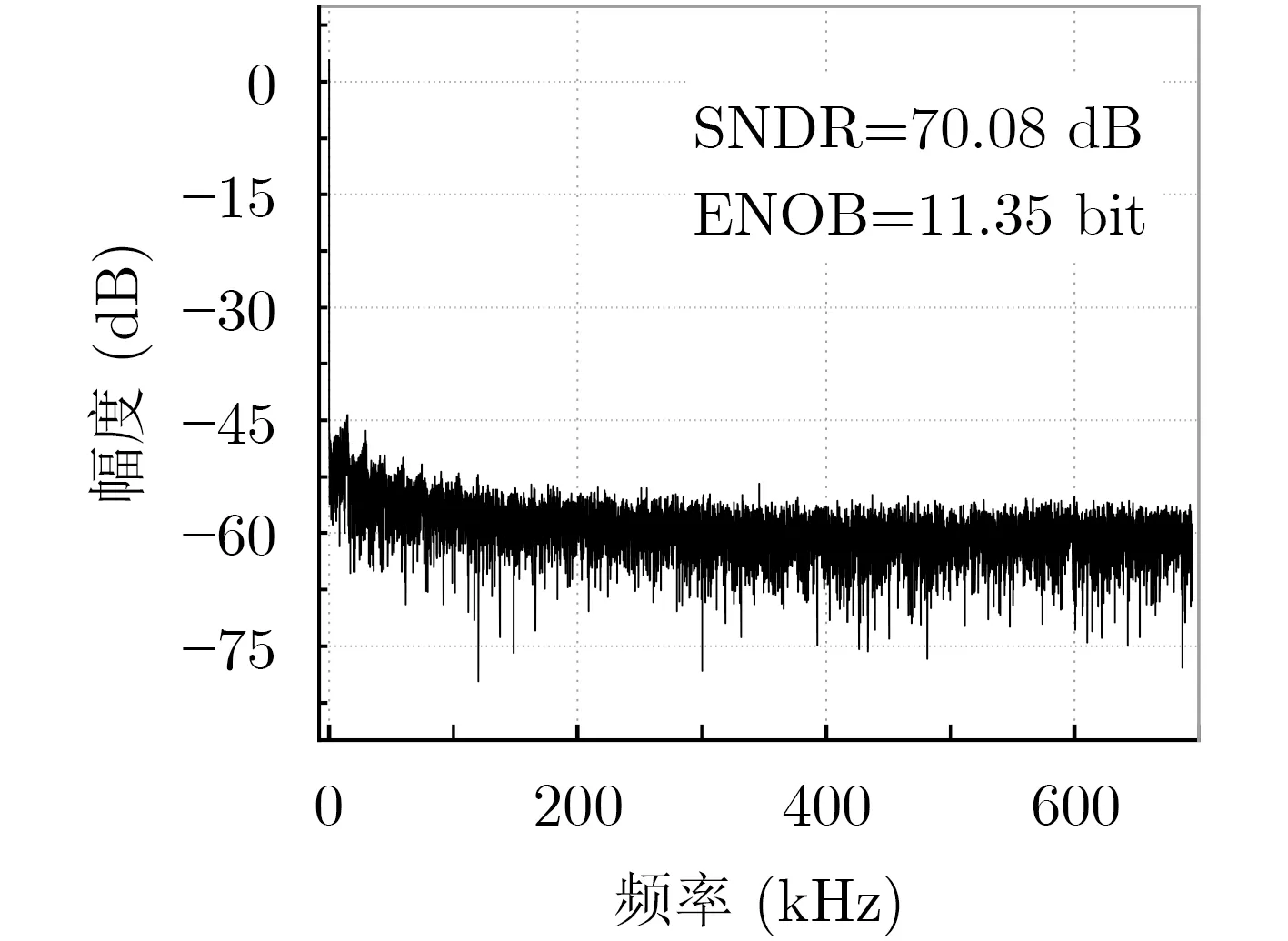

以1.21 MHz的采樣頻率對147.964 Hz信號采樣8 192組數據進行FFT分析結果如圖14所示。本文設計的ADC信噪失真比(Signal Noise Distortion Ratio, SNDR)為70.08 dB,有效位數(Effective Number Of Bits, ENOB)為11.35 bit,列級功耗為62 μW,動態范圍為1.6 V。

圖14 信噪比分析

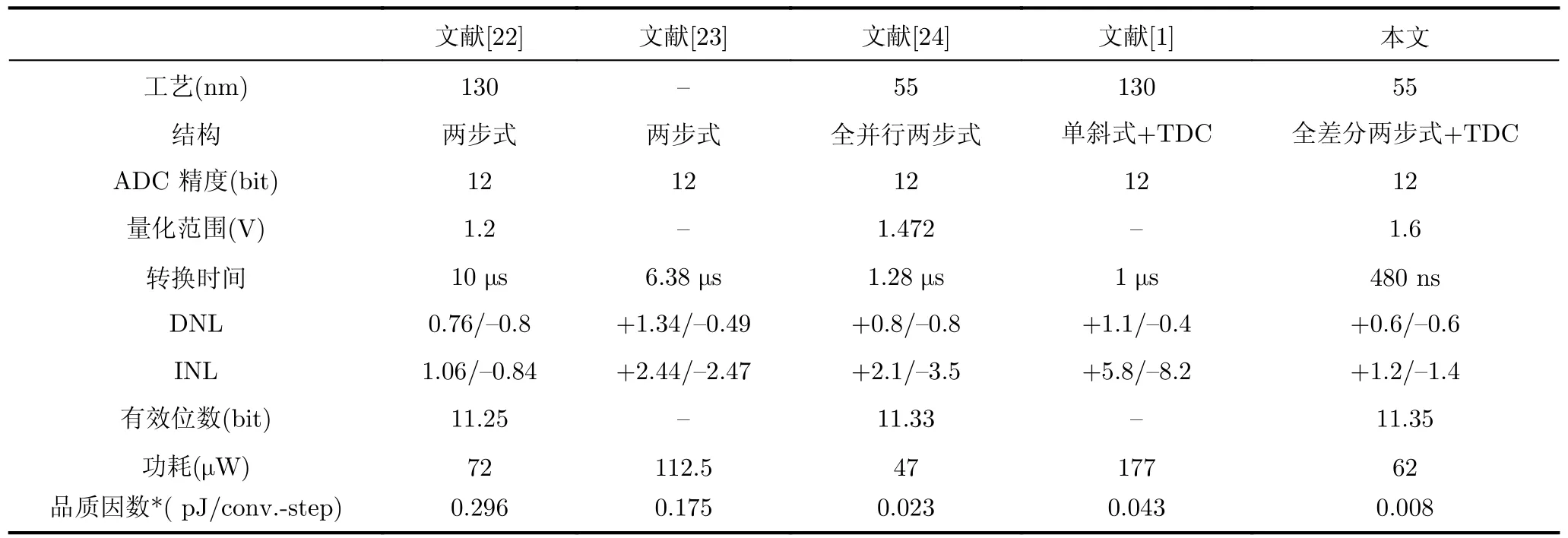

表1為本文設計方法與目前同領域前沿研究對比結果,表中ADC架構均在12 bit的精度下進行對比,文獻[22–24]均為粗細斜坡量化的兩步式結構,與文獻[22]相比,本文功耗減少了14%,轉換速度縮短了95.2%;與文獻[23]相比,本文功耗減少了45%,轉換速度縮短了92.5%;與文獻[24]相比,本文功耗高出32%,但是帶來了將近62.5%的速度收益,而且靜態特性更好;文獻[1]是以SS ADC與TDC相結合的兩步式架構,相較于文獻[1],本文功耗減少了65%,轉換速度縮短了52%。以上的對比可以看出,在相同精度下,本文設計的ADC與目前前沿架構相比,在保證功耗的前提下,依然具有明顯的速度優勢,轉換速度提高了52%以上。本文設計的ADC由于工藝和系統架構的先進性,實際帶來的速度提升效果與理論分析基本一致。綜上所述,本文提出的設計方法與現有的參考文獻相比,具有明顯的優勢。

表1 本文設計方法與文獻的對比結果

7 結論

本文針對高幀頻CMOS圖像傳感器對列級處理電路的高速要求,提出一種基于全差分兩步式ADC和低功耗TDC相結合的高速高精度ADC設計方法,該ADC設計方法將差動量化嵌套在兩步式的量化中,形成了區別于串行量化的并行量化模式,同時由于差動斜坡的存在,保證了系統的魯棒性;針對傳統TDC技術與單斜式ADC的匹配性問題,提出了一種基于電平編碼的TDC技術,在ADC量化的最后一個時鐘周期完成時間數字轉換,實現另一個層面的兩步式量化過程。最后在一款基于55 nm 1P4M工藝的8 192×8 192規模CIS芯片上進行了具體電路設計驗證,實驗結果表明,該ADC在單次量化達到480 ns的同時,將DNL的峰值誤差控制在了+0.6/–0.6 LSB,將INL控制在了+1.2/–1.4 LSB,并且對ADC的轉換結果進行FFT分析可得到包含輸入信號在內的幅頻曲線,將ADC的系統噪聲和隨機噪聲考慮在內,SNDR達到了70.08 dB,有效位數達到11.35 dB。

可見,本文提出的設計方法將現有SS ADC的轉換速度提高了52%以上,且隨著精度的提高對時間的收益越明顯,因此,該設計方法為高幀頻大面陣CMOS圖像傳感器提供了先進的實現方案。