一種偵干探多功能一體化微系統(tǒng)設計

肖國堯, 廖桂生, 柯華鋒, 李 帥, 全英匯

(1. 西安電子科技大學電子工程學院, 陜西 西安 710071; 2. 西安電子科技大學雷達信號處理全國 重點實驗室, 陜西 西安 710071; 3. 中國空間技術研究院通信與導航衛(wèi)星總體部, 北京 100094)

0 引 言

隨著雷達、電子戰(zhàn)等電子信息系統(tǒng)新技術和新體制的發(fā)展,以及先進封裝技術的出現(xiàn),將偵察、干擾、探測、通信等功能一體化[1-3],是未來電子頻譜作戰(zhàn)的必然手段。為了滿足系統(tǒng)中所有功能組件的可任意調(diào)配、性能參數(shù)可被編程,實時動態(tài)調(diào)配裝備平臺上的各種資源,使得作戰(zhàn)資源的配置更加優(yōu)化,提升交戰(zhàn)的有效性、戰(zhàn)術應用的活性以及系統(tǒng)整體性能的魯棒性,從而符合該要求的柔性構(gòu)造在信息化裝備平臺中被提出[4]。柔性構(gòu)造是實現(xiàn)偵干探一體化的最優(yōu)途徑,能提升信息化裝備對于復雜戰(zhàn)場環(huán)境的適應能力。

近年來,許多研究機構(gòu)、高校和公司都圍繞著一體化的概念提出了不同的設計方案,文獻[5]提出了一種基于隨機脈沖重復間隔(pulse repetition interval, PRI)捷變的雷達通信一體化共享設計方法,意在波形設計上融合多種功能來減少電子設備的體積和提高頻譜利用率。文獻[6]研制了高密度的相控陣T/R組件,減小相控陣面厚度和減輕陣面的重量,有效降低了星載或者彈載系統(tǒng)的載荷體積和重量。文獻[7]基于微組裝混合集成技術設計了一種具備雷達/偵察/干擾一體化收發(fā)前端,提高了作戰(zhàn)威力。文獻[8]介紹了一種數(shù)字信道化技術的偵察干擾一體化處理單元,實現(xiàn)對寬帶信號的收發(fā),完成對雷達信號的數(shù)字移頻干擾。

對于無人機載、彈載綜合電子系統(tǒng)領域,多功能信號處理平臺的靈活性、便攜性、實時性以及小型化等特點尤為重要,也是未來主要發(fā)展的重要技術方向[9]。隨著雷達信號帶寬、接收通道數(shù)量、工作模式種類等不斷增長,對其的實時處理能力、運算密集度、高速數(shù)據(jù)傳輸?shù)刃阅芴岢隽烁叩囊?面臨體積、重量、功耗、通道等多方面的嚴峻挑戰(zhàn)。而現(xiàn)階段信號處理系統(tǒng)仍為分立器件搭建,常見如3U、6U標準VITA第2代傳輸接口(VIAA P2 express, VPX)模塊與機箱,系統(tǒng)集成度低、體積龐大且互聯(lián)復雜、冗余,對應于信息化裝備中的偵察、干擾、探測等信號處理系統(tǒng)與裝備平臺的功能是一一對應的。各功能系統(tǒng)相互之間獨立性強,軟、硬件資源利用率較低,難以實現(xiàn)偵察、干擾、探測等多功能綜合處理,無法滿足未來復雜電磁頻譜環(huán)境的應用需求。

為了能很好地解決信號處理系統(tǒng)上述存在的問題以及偵干探一體化柔性構(gòu)造技術的問題,“微系統(tǒng)”是一個非常好的技術突破點[10-12]。微系統(tǒng)技術融合了微電子、微機電和微光電技術,采用統(tǒng)一的硬件系統(tǒng)架構(gòu)、共享/復用計算單元以及標準化軟件知識產(chǎn)權(quán)(intellectual property,IP)的思路,通過將處理器、控制器、轉(zhuǎn)換器以及各種接口等進行集成設計,構(gòu)成一體化軟、硬件多功能集成系統(tǒng),并采用微納制造及微集成工藝實現(xiàn)系統(tǒng)結(jié)構(gòu)的微型化,具有高集成度、微小型化、低功耗、高可靠性、高效率等優(yōu)點。微系統(tǒng)技術上的新材料、新方法、新工藝等技術變革必將對系統(tǒng)研發(fā)和制造帶來顛覆性影響,微系統(tǒng)具備從信息獲取到分析決策,再到指令執(zhí)行等完整電子信息系統(tǒng)功能,是實現(xiàn)單一或多種用途電子信息系統(tǒng)的綜合性前沿性技術,也是一種能更好地解決多功能一體化與柔性化構(gòu)造的關鍵技術[13]。

針對偵干探多功能一體化技術發(fā)展需求,本文著重研究與分析了偵干探一體化集成的可行性,開展全新架構(gòu)的偵干探多功能一體化微系統(tǒng)設計研究,并提出了一種偵干探多功能集成微系統(tǒng)設計新方法,采用異質(zhì)異構(gòu)混合系統(tǒng)集成思想,將偵干探多種功能的信號處理單元核心部組件。如數(shù)模轉(zhuǎn)換器(digital to analog converter, DAC)/模數(shù)轉(zhuǎn)換器(analog to digital converter, ADC)、高性能處理器、大容量存儲器等不同功能、不同工藝、不同材料芯片,通過系統(tǒng)級封裝(system in package, SiP)、三維堆疊、多芯片封裝等集成技術手段,進行微型化集成設計,形成信號處理SiP硬件模塊。同時,基于該SiP模塊平臺,開展偵干探一體化綜合處理軟件設計、實現(xiàn)與驗證。最后,形成偵干探一體化的多功能集成微系統(tǒng)。

該微系統(tǒng)可為偵干探多功能信息化系統(tǒng)應用提供靈活、便捷以及軟件化、標準化、模塊化的信號處理系統(tǒng)平臺,且大幅縮短了系統(tǒng)的研發(fā)、驗證和迭代周期,大大縮減了信號處理系統(tǒng)的體積和重量。同時,采用異質(zhì)異構(gòu)混合系統(tǒng)集成思想,將金絲引線鍵合(wire bonding, WB)、集成無源元器件(integrated passive device, IPD)、重新布線層(re-distribution layer, RDL)以及三維堆疊技術等多種封裝工藝技術進行集成、混合應用,共同實現(xiàn)復雜系統(tǒng)的可靠集成。該微系統(tǒng)設計技術在架構(gòu)、性能、工藝實施等方面具有較大優(yōu)勢和應用前景。

1 微系統(tǒng)整體架構(gòu)設計

在傳統(tǒng)的偵察接收機中,基于低通采樣結(jié)構(gòu)的數(shù)字接收機[14-15]接收較高頻段的信號時,存在不滿足奈奎斯特采樣定理的缺點,無法對信號進行有效恢復。基于帶通采樣結(jié)構(gòu)的數(shù)字接收機[14-15]由于需要使用可調(diào)諧帶通濾波器實現(xiàn)對整頻帶進行時分偵收,在某一時刻支持特定的頻帶進行處理,導致靈活性和實時性都無法滿足高精度和高性能的要求。基于中頻帶通采樣結(jié)構(gòu)的數(shù)字接收機[16]由于前端的模擬部分較多,結(jié)構(gòu)設計最為復雜,不適合在小型化中使用。而信道化接收機[17-22]不僅能滿足對高頻段信號接收的需求和結(jié)構(gòu)實現(xiàn)簡單的優(yōu)點,還因具有高靈敏度、大動態(tài)范圍、同步信號檢測以及全概率接收信號等理想的特點被廣泛的應用于各個領域。

在現(xiàn)有的干擾系統(tǒng)中,由于受到體積、功率等因素的限制,無法實現(xiàn)對寬帶雷達信號的高速采樣和對天線收發(fā)的高度隔離,而采用的傳統(tǒng)轉(zhuǎn)發(fā)干擾方法[23-25]需要將全部時長的雷達信號接收后,才進行調(diào)制轉(zhuǎn)發(fā)。該種方法所形成的假目標遠遠落后于真實目標,容易處在距離波門之外,無法形成有效的干擾。對于間歇采樣轉(zhuǎn)發(fā)干擾,由于其獨特的“欠采樣”和收發(fā)分時特性,對雷達信號進行間歇性采樣,不僅大大降低了信號處理的高速采樣要求,還能解決天線收發(fā)的隔離問題,對裝備在小型化設備上提供了可能。并且切片轉(zhuǎn)發(fā)的時寬帶寬小,易于進行調(diào)制和多種模式的組合等工程實現(xiàn),極大地豐富了干擾的樣式。同時,間歇采樣轉(zhuǎn)發(fā)干擾作為一種針對脈沖壓縮雷達的干擾樣式,其本質(zhì)與雷達信號具有部分相干特性,從而可以產(chǎn)生與目標信號相似的相干假目標串,達到影響雷達對目標的正常檢測效果。有研究表明,間歇采樣轉(zhuǎn)發(fā)干擾對發(fā)射信號為線性調(diào)頻信號、相位編碼信號、V-調(diào)頻信號的脈沖多普勒(pluse Doppler, PD)雷達、合成孔徑雷達(synthetic aperture radar, SAR)、逆SAR(inverse SAR, ISAR)體制和多輸入輸出(multiple input multiple output, MIMO)雷達均能達成有效的干擾[26-27]。

對于探測功能系統(tǒng),MIMO雷達通過發(fā)射正交波形獲得波形分集增益,對比技術已經(jīng)成熟并應用較廣的相控陣雷達,在參數(shù)估計能力等方面具有較大提升[28-29]。而MIMO雷達對于信號處理系統(tǒng)的需求是具備同時多發(fā)多收處理功能,所以在小型化上實現(xiàn)MIMO雷達的信號處理,微系統(tǒng)是一個很好的實現(xiàn)方向。

本節(jié)先對信道化偵察、間歇采樣轉(zhuǎn)發(fā)干擾、主動MIMO雷達探測功能的信號處理算法與實現(xiàn)進行分析,再提取偵干探多功能的公共計算單元/因子,并結(jié)合重構(gòu)/復用的軟件設計與先進封裝技術,提出了一種偵察、干擾、探測多功能信號處理一體化軟件設計與小型化集成設計新技術,形成具有偵干探多功能軟、硬件信號處理能力的微系統(tǒng)。該微系統(tǒng)具有一定的適用性,且在資源受限(體積、性能、功耗)應用場景中,有著巨大技術優(yōu)勢與應用前景。

1.1 一體化軟件架構(gòu)設計

1.1.1 偵察功能信號處理分析

在偵察信號處理過程中,傳統(tǒng)的接收機射頻(radio frequency, RF)前端復雜,不利于系統(tǒng)的小型化應用,隨著RF直采技術、大帶寬高采樣率模數(shù)轉(zhuǎn)換器件的發(fā)展,RF數(shù)字化已是大勢所趨。本文采用多相濾波器結(jié)構(gòu)[30-33]的大帶寬信道化技術實現(xiàn)偵察功能的數(shù)字接收機。如圖1所示,采用大帶寬ADC將一定頻帶內(nèi)的RF信號全數(shù)字化,得到x1(n),再經(jīng)數(shù)字下變頻和多倍抽取器得到零中頻和降采樣處理后的寬帶信號x2(n),采用多相濾波器將寬帶信號x2(n)劃分為N個均勻信道以及進行N點并行快速傅里葉變換(fast Fourier transform, FFT)處理,最后得到單個信道的基帶信號,該信號模型可表示為

Ymi(k)=DFT[x(m)(-1)ρejπρ/K]|m=mi

(1)

圖1 信道化信號處理流程Fig.1 Channelized signal processing flow

多相濾波器組可使得濾波運算和信號處理速率大大地降低,同時仍能滿足靈活性、實時性和高性能需求。該結(jié)構(gòu)采用數(shù)字化處理方式,減少RF鏈路,使得接收機系統(tǒng)更簡單,便于小型化、標準化。

1.1.2 干擾功能信號處理分析

間歇采樣轉(zhuǎn)發(fā)干擾,由于其獨特的“欠采樣”和收發(fā)分時特性,對雷達信號進行間歇性采樣,不僅大大降低了信號處理高速采樣的要求,還能解決天線收發(fā)的隔離問題,對裝備在小型化設備運用上提供了可能。并且切片轉(zhuǎn)發(fā)的時寬帶寬小,易于進行調(diào)制和多種模式的組合等工程實現(xiàn),極大地豐富了干擾的樣式。本文重點關注間隙采樣直接轉(zhuǎn)發(fā)干擾、間歇采樣重復轉(zhuǎn)發(fā)干擾以及間歇采樣隨機相位調(diào)制重復轉(zhuǎn)發(fā)干擾3種干擾模式,并建立信號模型[26,34-37]如下:

(2)

式中:T表示采樣時長;Ts表示采樣周期,且Ts=MT,M為當前脈沖串轉(zhuǎn)發(fā)次數(shù);ε(t)為一個碼元持續(xù)時間;φ(n)為隨機相位碼元序列。從該模型可得出,當M轉(zhuǎn)次數(shù)為1時,對應的干擾模式為直接轉(zhuǎn)發(fā)干擾,當碼元隨機序列φ(n)皆為同相時,干擾模式就從隨機相位調(diào)制重復轉(zhuǎn)發(fā)干擾變?yōu)橹貜娃D(zhuǎn)發(fā)干擾。則可認為前兩種干擾模式為隨機相位調(diào)制重復轉(zhuǎn)發(fā)干擾特殊情況,通過該信號模型,可得出干擾功能的完整信號處理流程如圖2所示,通過配置相關模式切換輸出路徑、控制轉(zhuǎn)發(fā)次數(shù),部署對應的干擾策略,使得功能模塊的實現(xiàn)更加簡便。

圖2 偵干探一體化綜合處理軟件架構(gòu)設計Fig.2 Integrated processing processing software architecture design for reconnaissance jamming and detection

1.1.3 探測功能信號處理分析

探測功能與傳統(tǒng)的MIMO雷達信號處理方式類似,接收上位機下發(fā)引導信息,裝訂波束指向與采樣波門起始位置,采集N路天線前端輸出的MIMO回波數(shù)據(jù),將回波數(shù)據(jù)下變頻到基帶后,對基帶回波信號經(jīng)過多倍抽取器獲取需要的處理采樣點數(shù)。根據(jù)波束指向?qū)Τ槿『蟮幕夭〝?shù)據(jù)做接收數(shù)字波束形成,將N路回波數(shù)據(jù)合成一路,這一路數(shù)據(jù)中會攜帶N個正交分量。通過組匹配濾波器將接收波束形成后的數(shù)據(jù)中的正交分量分離出來,得到N路脈沖壓縮結(jié)果。將N路脈沖壓縮結(jié)果再進行一次等效發(fā)射波束形成,等效發(fā)射波束形成權(quán)系數(shù)為接收波束形成權(quán)系數(shù)的共軛,得到最終的合成數(shù)據(jù)。在同一方向連續(xù)接收M次回波數(shù)據(jù),得到一個相干處理間隔(coherent processing interval, CPI)的等效發(fā)射波束形成結(jié)果,在做動目標檢測(moving targets detection, MTD)、恒虛警率(constant false alarm rate, CFAR)檢測與目標凝聚等目標檢測,獲取目標的距離與多普勒信息[38-42]。使用單脈沖比幅測角方法得到方位和俯仰的鑒角曲線,通過比對獲取目標的空間角度信息。最后,將目標的距離、多普勒與角度信息上報給上位機[43-44],探測信道處理流程如圖2所示。

1.1.4 多功能一體化軟件架構(gòu)

為了將上述3種信號處理功能融入到同一種系統(tǒng)框架,使得具備自主多任務規(guī)劃、軟硬件協(xié)同、認知外部環(huán)境并動態(tài)配置電路功能,滿足在極高時序約束、更小體積空間、更多功能等特點的條件下實際使用需求。本節(jié)將按照不同功能類型進行信道劃分,再提取信道間的共同計算單元,結(jié)合重構(gòu)/復用的軟件設計思路,可設計出適合微系統(tǒng)的偵干探一體化綜合處理軟件架構(gòu),如圖2所示。

在紅色虛框中,根據(jù)運算實時性和消耗資源的需求,將上述實框中功能模塊單元規(guī)劃到DAC/ADC、現(xiàn)場可編程門陣列(field programmable gate array, FPGA)和ARM(advanced RISC machine)處理器這3個硬件單元中。然后進行統(tǒng)一調(diào)度,分別發(fā)揮不同軟件功能,以便能高效地利用系統(tǒng)有限的接口、邏輯和運算資源。在可編程邏輯單元中,可以設置時序模塊產(chǎn)生偵察、干擾和探測的收發(fā)邏輯控制,完成對數(shù)據(jù)解包模塊和數(shù)據(jù)打包模塊的數(shù)據(jù)傳輸職能,以及對間歇采樣周期、采樣時長和采樣數(shù)據(jù)完成編號的流水線控制。數(shù)字下變頻、抽取和數(shù)字上變頻和插值4個共用IP模塊,可以根據(jù)各個信道的不同參數(shù)進行調(diào)用,完成收發(fā)的時段的頻譜搬移和處理速率匹配.有限脈沖響應(finite impulse response, FIR)濾波器組可以設置成低通、高通、或者是多相濾波器模式,根據(jù)各自信道的需求完成調(diào)用。N點FFT蝶形運算可實現(xiàn)對數(shù)據(jù)從時域變到頻域的處理,最大可支持64點并行運算。波束形成算法IP、脈沖壓縮IP、相位調(diào)制模塊、序列編號模塊和存儲區(qū)調(diào)用模塊都是作為專用模塊完成相應功能的數(shù)據(jù)處理。在多核處理器中,通過數(shù)據(jù)交換網(wǎng)絡可完成接收可編程邏輯端打包傳輸過來的數(shù)據(jù),也可以將上位機下發(fā)的數(shù)據(jù)包發(fā)送到相應的功能信道。DAC/ADC控制單元可以實時地調(diào)度多路轉(zhuǎn)換器進行收發(fā)處理,同時檢測各路轉(zhuǎn)換器的工作狀態(tài)。以太網(wǎng)收發(fā)控制單元可以完成與上位機進行通訊和數(shù)據(jù)傳輸,通過上位機參與到軟件的參數(shù)設置和功能模塊調(diào)度。多核交互單元和存儲數(shù)據(jù)調(diào)用模塊可以完成多核之間的數(shù)據(jù)互傳,實現(xiàn)多核并行處理控制和數(shù)據(jù)共享。MTD運算單元、CFAR檢測率運算單元、單脈沖測角運算單元、目標凝聚運算單元、門限判決運算等模塊作為對應信道的專用信號處理模塊調(diào)用。

1.2 多功能集成設計

根據(jù)偵察、干擾、探測一體化綜合處理軟件架構(gòu)設計中軟硬件資源的需求,結(jié)合高中頻、RF直采能力的信號處理技術以及多核處理器與可編程邏輯資源融合的異構(gòu)可重構(gòu)計算體系結(jié)構(gòu),探索了偵干探多功能一體化集成的可行性與新型架構(gòu)技術。本節(jié)提出了一種可實現(xiàn)偵干探多功能信號處理能力的微系統(tǒng)硬件結(jié)構(gòu),如圖3所示。通過先進系統(tǒng)級封裝技術手段,將信號處理系統(tǒng)核心單元部組件,如DAC/ADC、ARM、FPGA、主控處理器(main control processor, MCP)等,進行共封裝集成設計,形成具有偵干探多功能綜合處理能力的微系統(tǒng)芯片。在該微系統(tǒng)芯片上,實現(xiàn)如圖2所示的軟件架構(gòu),將偵干探一體化進行功能拆分,根據(jù)各個核心組件的特性,合理利用有限資源,各個核心組件分別進行相應的軟件配置。相比傳統(tǒng)結(jié)構(gòu),可實現(xiàn)更高波段、更高吞吐量、更低延時和更佳性能功耗比,同時適用于偵干探多功能系統(tǒng),具有多功能、可重構(gòu)、微型化、輕量化以及靈活、便捷等特點與優(yōu)勢。

圖3 多功能集成微系統(tǒng)結(jié)構(gòu)Fig.3 Multi-functional integrated microsystem architecture

微型化集成受散熱、尺寸以及封裝成本與工藝難度等諸多因素影響,并非所有分立器件均適用于微型化集成。本文在考慮上述因素外,還需滿足偵干探多功能一體化綜合處理能力需求,結(jié)合微型化、多功能、高性能以及現(xiàn)階段已有芯片技術,將高性能ADC和DAC、高性能處理器ARM、大規(guī)模FPGA、大容量數(shù)據(jù)緩存器DDR4 SDRAM(double-data-rate fourth generation synchronous dynamic random access memory)、程序存儲器Nor FLASH、時鐘芯片、線性穩(wěn)壓電源(low drop out, LDO)以及IPD(intelligent power device)電阻、電容等不同種類、不同工藝、不同材質(zhì)的芯片和元件,通過三維堆疊等先進系統(tǒng)級封裝技術手段,進行集成設計,構(gòu)成信號處理SiP芯片。核心芯片選用Xilinx公司最新一代UltraScal+系列—RFSoC芯片,該芯片集成RF直采能力的ADC、DAC、多核ARM以及大規(guī)模FPGA等,ADC/DAC/FPGA/ARM間的高速互聯(lián)采用先進的微控制器總線體系結(jié)構(gòu)(advanced microcontroller bus architecture, AMBA),直接在芯片內(nèi)部相連,很好地解決了外部接口占用空間、IO等資源問題,且集成度高,節(jié)省額外的互聯(lián)線路開銷,具有更高吞吐量、更低延時和更佳性能功耗比。該芯片無論體積尺寸、功能密度,還是異構(gòu)計算架構(gòu)、計算性能以及能耗比,均適用于微型化集成系統(tǒng)設計。

同時,為了提高系統(tǒng)集成度,降低設計難度、工藝難度和成本,將大容量數(shù)據(jù)緩存器DDR4 SDRAM、程序存儲器Nor Flash以及外圍電路如匹配電阻、去耦電容和參考電源等裸芯片、元件通過三維堆疊、引線鍵合等手段進行集成設計,構(gòu)成具有獨立功能的單顆存儲系統(tǒng)芯片。最后,再將獨立封裝的存儲系統(tǒng)芯片、RFSoC芯片以及外圍電路和阻容等進行二次封裝集成,構(gòu)成信號處理SiP芯片[45-50]。

2 存儲系統(tǒng)集成設計

為了更好地提升系統(tǒng)集成度與簡化集成難度,降低工藝復雜度,提升良率,針對信號處理微系統(tǒng)集成中的存儲系統(tǒng)集成設計,提出了一種全新的多功能存儲系統(tǒng)集成方案:將DRAM芯片、Flash芯片、終端匹配電阻、濾波電容以及參考電源芯片等全部集成在一個微小封裝內(nèi),構(gòu)成一顆具備通用能力的存儲系統(tǒng)芯片,該芯片同時具備數(shù)據(jù)緩存、程序存儲等功能。除了具有更高集成度之外,該存儲系統(tǒng)芯片可將72 bit位寬系統(tǒng)分為32 bit位寬和40 bit位寬(帶ECC(error checking and correcting)校驗8 bit)兩組獨立存儲器,單芯片可以支持32 bit、40 bit、64 bit以及72 bit這4種不同位寬存儲系統(tǒng)應用,另外支持32 bit和40 bit或32 bit和32 bit同時使用,且多片芯片并聯(lián)使用可擴展更高存儲位寬,如128 bit等,具有更強的靈活性和擴展性。

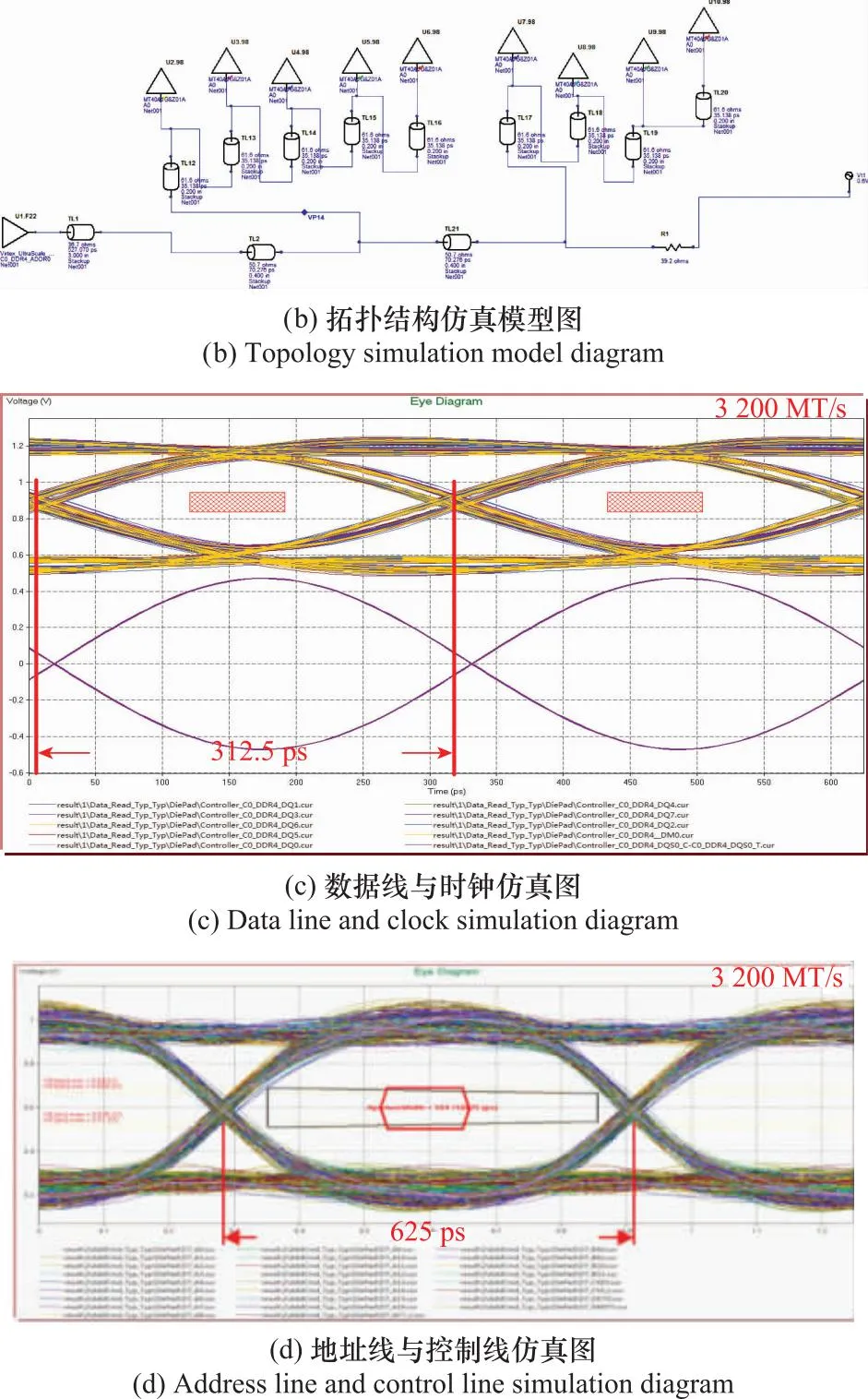

互聯(lián)拓撲結(jié)構(gòu)對DDRx SDRAM的系統(tǒng)應用至關重要,往往在布局之前,甚至是系統(tǒng)設計初期就要優(yōu)先考慮。本文在集成設計時,結(jié)合系統(tǒng)特點和需求,優(yōu)先對拓撲結(jié)構(gòu)進行規(guī)劃與論證分析,并通過建模和仿真驗證指導存儲系統(tǒng)的拓撲結(jié)構(gòu)設計,從而確保設計的可行性與正確性。

多片DDRx SDRAM顆粒互聯(lián)設計中,重點為其拓撲結(jié)構(gòu)設計,常用拓撲結(jié)構(gòu)主要有以下兩種:Fly-by結(jié)構(gòu)和T型結(jié)構(gòu),如圖4(a)所示。本文提出的存儲系統(tǒng)芯片主要設計難點在多片DDR4 SDRAM的堆疊設計與互聯(lián)拓撲設計,綜合Fly-by、T型拓撲結(jié)構(gòu)的優(yōu)缺點,本文采用Fly-by與T型結(jié)構(gòu)結(jié)合的共同拓撲結(jié)構(gòu)和DDR4 SDRAM多片堆疊設計,很好地解決了小面積、低層數(shù)的基板布局布線設計以及堆疊芯片鍵合互聯(lián)帶來的新問題。本文采用的拓撲結(jié)構(gòu)與堆疊設計模型示意圖如圖4(b)所示,9片DDR4 SDRAM分為兩組進行堆疊,其中一組為5層堆疊(40 bit位寬),一組為4層堆疊(32 bit位寬),兩組共同構(gòu)成72 bit位寬(帶ECC功能)。

圖4 存儲器集成拓撲方案對比Fig.4 Comparison of memory integration topology schemes

采用上述拓撲方案,通過對拓撲結(jié)構(gòu)與堆疊鍵合的聯(lián)合模型構(gòu)建、仿真和分析,充分驗證該拓撲結(jié)構(gòu)和鍵合方案的可行性。按照鍵合線最大長度200 mil、鍵合線阻抗61 Ω、最大速率3.2 Gbps,進行數(shù)據(jù)線、地址線、控制線以及時鐘線的信號仿真。如圖5所示的仿真圖中,各信號線眼圖效果良好,數(shù)據(jù)線與地址線的眼寬均滿足需求,同時數(shù)據(jù)線一個UI寬度312.5 ps,地址線一個UI寬度625 ps,反映了數(shù)據(jù)線和地址線均可在3 200 Mbps速率下正常傳輸,且有較大設計余量,可補償在工程實施過程中引入的誤差,提高容錯率,提升成功率。

圖5 存儲器集成仿真測試Fig.5 Memory integration simulation test

DDRx SDRAM采用兩組分開、錯位堆疊方式,數(shù)據(jù)線、地址線等采用金絲引線鍵合,每組片間地址與控制信號線采用級聯(lián)引線鍵合方式,構(gòu)成Fly-by拓撲結(jié)構(gòu),終端匹配電阻IPD芯片疊層在最上方。同時,多片Nor Flash也采用堆疊方式,示意圖如圖6(a)所示。圖6(b)和圖6(c)分別為DDRx SDRAM堆疊設計三維圖、存儲系統(tǒng)組裝設計三維圖。根據(jù)工藝種類,需逐步完成組裝:① 阻容元件貼裝;② 平鋪器件粘接、鍵合;③ 堆疊芯片粘接、鍵合;④ 塑封、成片;⑤ 植球。最終完成形態(tài)如圖6(d)所示。

圖6 儲存器集成效果圖Fig.6 Memory integration effect drawing

傳統(tǒng)分離器件搭建同等大小容量的儲存器與本文集成儲存器所需面積對照如表1所示,傳統(tǒng)分離器件構(gòu)成的存儲系統(tǒng)占用面積最小約2 85 mm2,而本文集成后面積為260 mm2,相比之下面積節(jié)約87.5%,且設計應用更加簡單、便捷,優(yōu)勢明顯。

表1 等容量儲存器所需面積對比Table 1 Comparison of area required for equal capacity packets

3 微系統(tǒng)集成設計

采用兩次集成設計方案可以大大降低信號處理SiP集成設計復雜度與難度,但在二次集成設計中仍然面臨模數(shù)混合信號隔離、ADC/DAC通道隔離、高速信號鏈路處理等難點問題,為解決該類問題,主要設計方法如下:

(1) 模擬信號區(qū)與數(shù)字信號區(qū)、模擬電源區(qū)與數(shù)字電源區(qū)盡可能隔開,減小信號串擾;

(2) 模擬信號、高速信號周圍采用地做屏蔽處理,確保傳輸鏈路干凈;

(3) 模擬信號、高速信號管腳分布周圍,盡可能用接地管腳隔離處理;

(4) 嚴格阻抗控制,盡可能縮短模擬信號、高速信號的傳輸路徑;

(5) 結(jié)合封裝布局進行仿真,通過仿真結(jié)果分析,進行設計優(yōu)化。

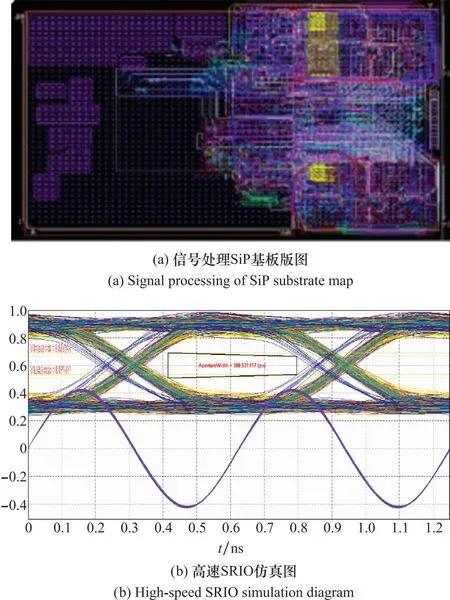

信號處理SiP基板設計版圖如圖7(a)所示,為了能更好地將信號互聯(lián)和扇出,高速串行通信(serial rapid IO, SRIO)測試仿真圖如圖7(b)所示。本文采用14層基板布局方案,通過增加地層和電源層,對關鍵信號扇出和電源分區(qū)做了較好的設計保護。圖7(c)和圖7(d)分別為接收通道與發(fā)射通道的通道隔離仿真結(jié)果。

圖7 信號處理SiP基板高速接口仿真測試Fig.7 Simulation test of signal processing SiP substrate high-speed interface

仿真時,選擇其中一通道作為輸入/輸出測試通道,同時其他通道保持靜默狀態(tài),測試頻段范圍從DC掃頻到10 GHz,并觀測通道變化情況,計算通道隔離度值:

(3)

式中:V1代表的是仿真中給到激勵通道幅度大小;V2代表靜默狀態(tài)通道的最大值。

可見,通道間隔離度優(yōu)于60 dB,滿足信號處理系統(tǒng)應用需求。

散熱設計也是信號處理SiP設計中的一大重點。經(jīng)過評估,如采用全塑封封裝方式,核心芯片熱量無法被傳出,將會直接影響芯片工作性能和系統(tǒng)穩(wěn)定性。為此,本文采用高導熱率金屬材料作為信號處理SiP的封裝殼體,殼體與芯片之間通過高導熱膠進行填充,同時在殼體與基板粘接處預留微通孔,用于釋放冷熱環(huán)境下產(chǎn)生的應力,最終得到信號處理SiP集成芯片如圖8所示。

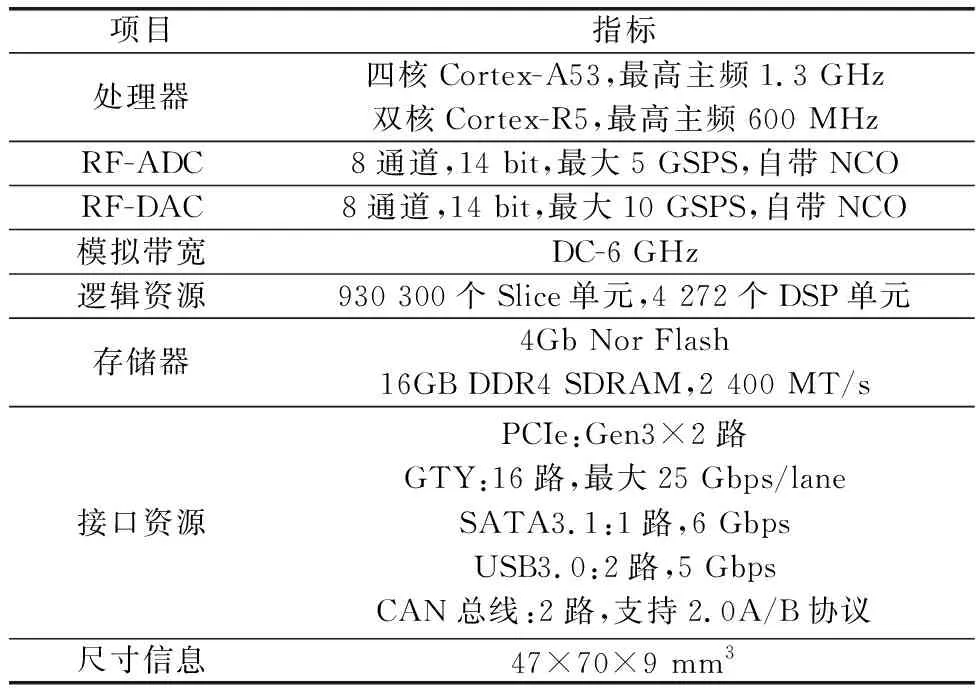

集成的信號處理SiP芯片技術指標參數(shù)如表2所示,可滿足一體化軟件功能中的偵察、干擾、探測信道的收發(fā)通道數(shù)量要求和信號帶寬需求,以及豐富的邏輯資源應用于信號處理算法功能實現(xiàn)和相關信息的提取。還有多個高速接口資源匹配到軟件系統(tǒng)用于擴展通信、控制和數(shù)據(jù)大帶寬傳輸功能。

圖8 信號處理SiP集成芯片F(xiàn)ig.8 Signal processing SiP integrated chip

表2 信號處理SiP芯片技術指標Table 2 Signal processing SiP chip technical indexes

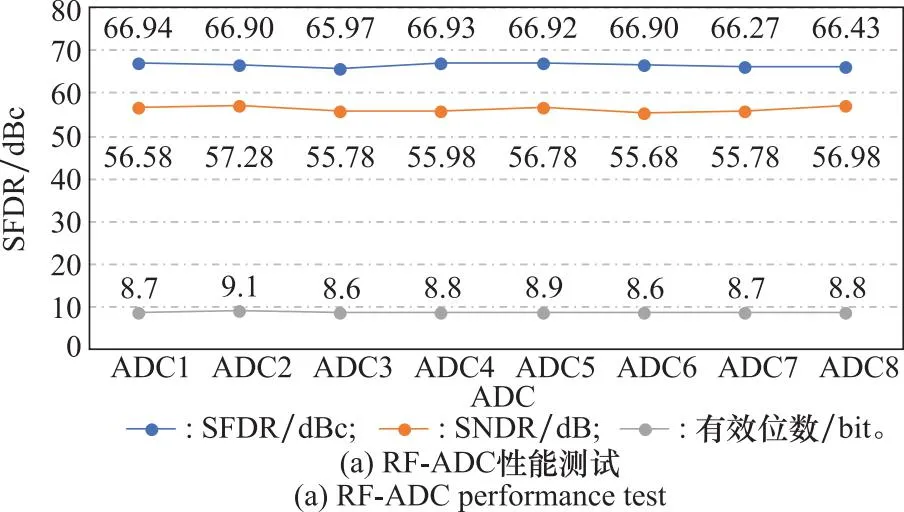

4 收發(fā)通道性能參數(shù)測試

信號處理SiP接收通道的無雜散動態(tài)范圍、信納比以及有效位數(shù)值的高低反映了接收通道性能的好壞,對于后續(xù)數(shù)據(jù)處理中算法實現(xiàn)產(chǎn)生了重要影響。對8路接收通道同時輸入1 GHz的正弦信號測試得到的結(jié)果如圖9(a)中的ADC性能測試曲線所示。可以看出,8路接收通道的有效位數(shù)變化不大,平均處于8.77 bit。同時,無雜散動態(tài)范圍(spurious-free dynamic range, SFDR)約為66.43 dBc,信噪失真比(signal to noise and distortion ratio, SNDR)平均值約為55.82 dB,接收通道的性能較好,與期望效果基本符合。另外,對8路發(fā)射通道輸出3 GHz的正弦波進行功率和相對相位偏移統(tǒng)計分析,測試結(jié)果如圖9(b)中的DAC性能測試所示,8路發(fā)射通道輸出功率偏差較小,其最大延遲時間不大于6 ps(DAC1通道作參考),輸出相位一致性較好,滿足大帶寬MIMO、相控陣以及數(shù)字陣系統(tǒng)應用需求。系統(tǒng)使用時,僅需確定前端RF組件的延時時間即可實現(xiàn)系統(tǒng)校正,簡化了系統(tǒng)校正的測試流程和復雜度。

圖9 多通道收發(fā)模擬轉(zhuǎn)換器性能測試Fig.9 Performance test of multichannel transceiver analog converter

5 實驗測試

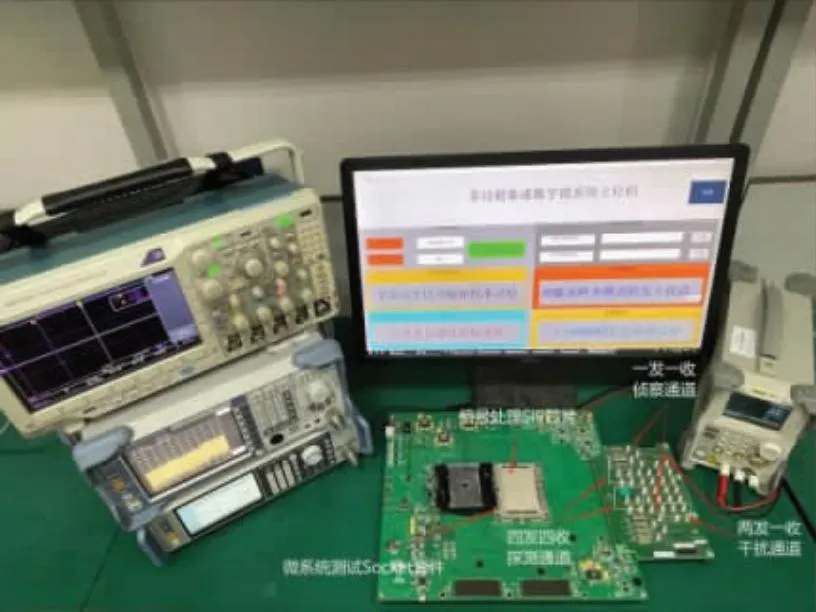

根據(jù)集成信號處理SiP芯片性能參數(shù)以及一體化軟件功能架構(gòu),本文多功能測試系統(tǒng)采用如圖10所示的微系統(tǒng)專用Socket測試環(huán)境,實現(xiàn)3個功能同時進行收發(fā)自回環(huán)測試。首先,對多通道模擬轉(zhuǎn)換器進行使能,其中偵察功能配置為一發(fā)一收測試通道,對2 GHz帶寬內(nèi)的信號進行偵收。其次,干擾功能配置為兩發(fā)一收測試通道,進行3種間歇采樣轉(zhuǎn)發(fā)干擾策略的切換。然后,探測功能配置四發(fā)四收測試通道,對設定目標完成相關信息的識別。

圖10 系統(tǒng)測試環(huán)境圖Fig.10 System test environment diagram

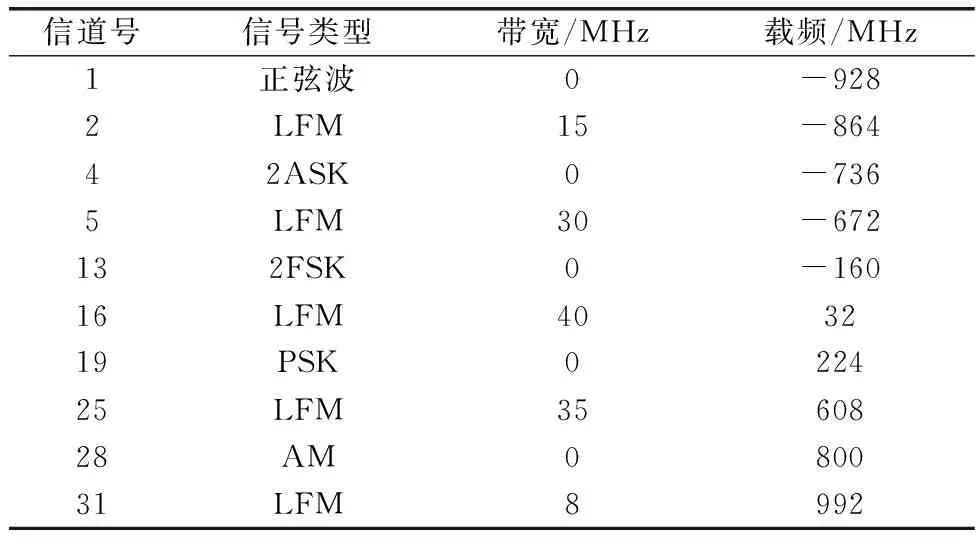

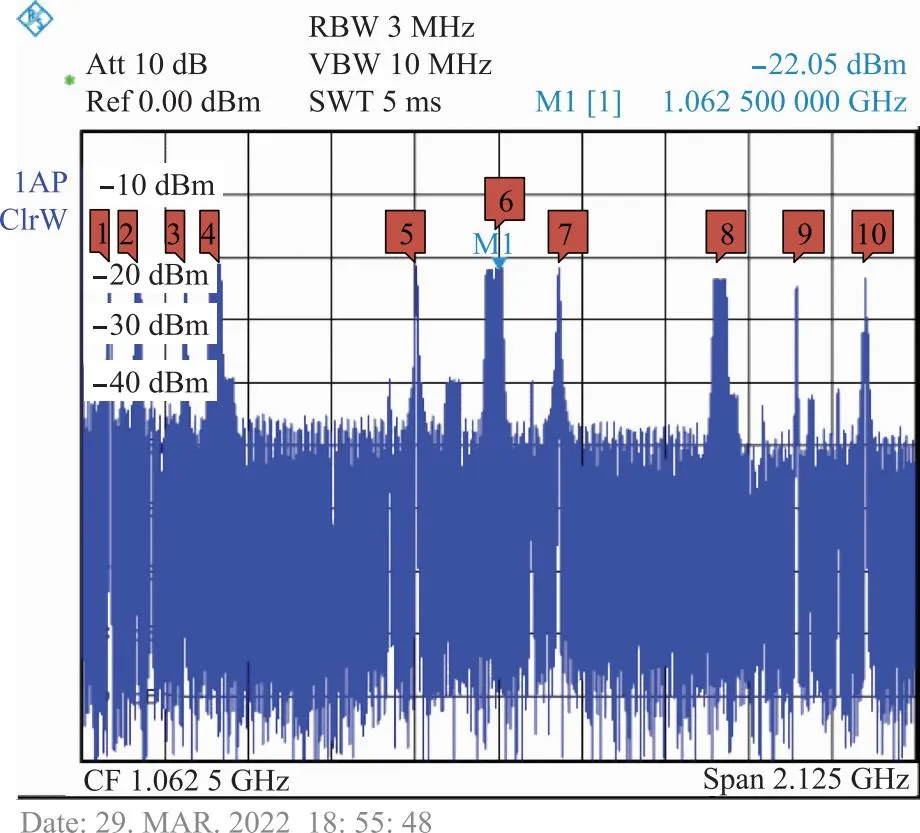

對于偵察功能測試,上位機根據(jù)如表3所示的信號參數(shù)生成10個不同頻點疊加的波形數(shù)據(jù),經(jīng)過多倍插值器和數(shù)字上變頻將輸入信號經(jīng)過發(fā)射通道輸出的頻譜如圖11所示,中心頻率為1 GHz,占用帶寬為2 GHz。再由采樣率為4.096 Gsps的ADC將該信號接收回來,經(jīng)由數(shù)字下變頻和2倍抽取后變?yōu)榱阒蓄l的寬帶復信號。

表3 發(fā)射波形信號列表Table 3 List of transmitted waveform signals

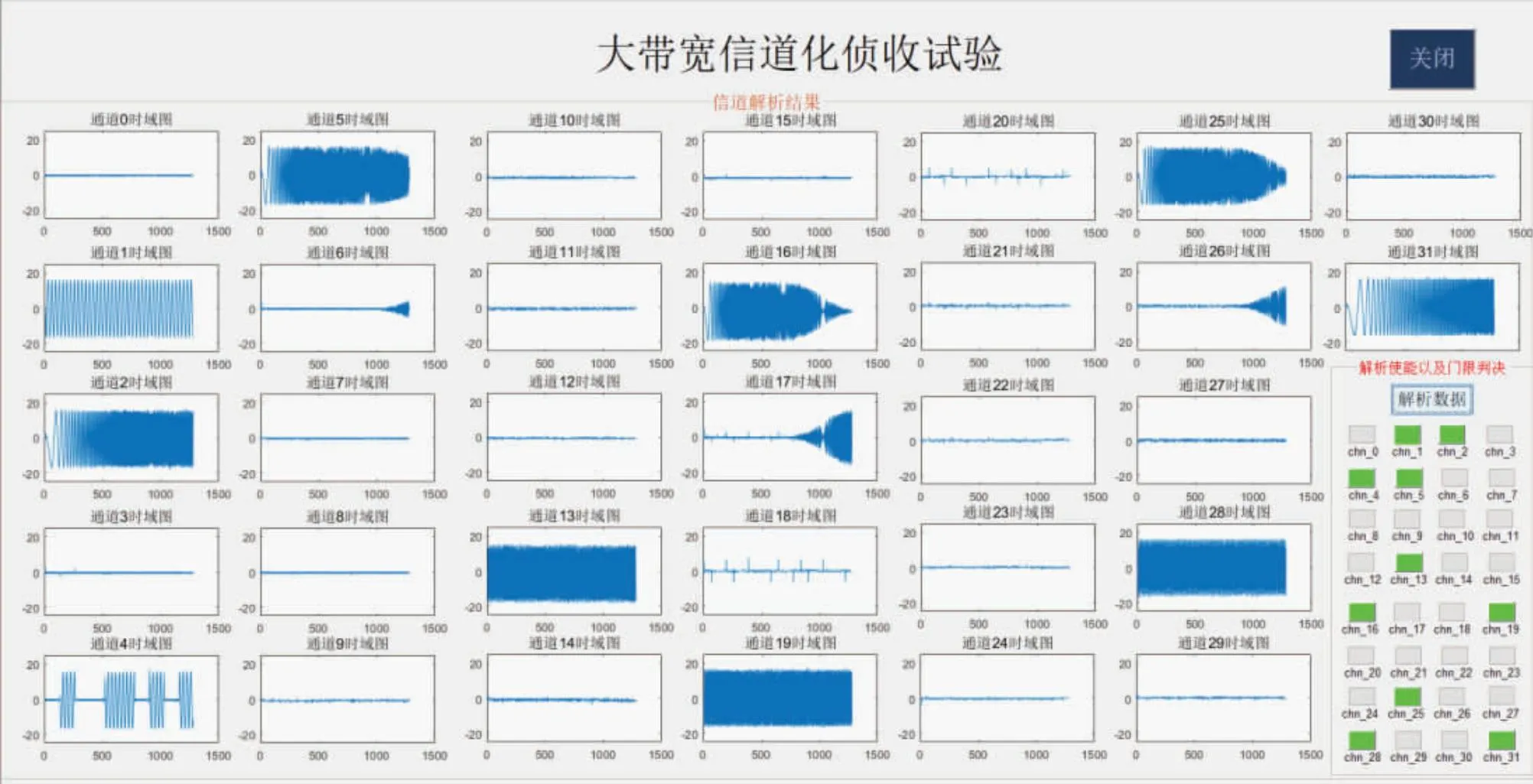

由表3可以得知,信號的帶寬最大為40 MHz,所以將接收回來的數(shù)據(jù)頻帶可以劃分32個信道,每個信道占用的帶寬為64 MHz。將寬帶復信號通過32個多相濾波器組和32點FFT處理后,得到的信道偵收結(jié)果如圖12所示。在結(jié)果中,除了將設定的信道號與發(fā)射波形一一對應之外,還能看到信道6、17和26也存在信號,緣由是劃分的32個多相濾波器組的子濾波器通帶只有32 MHz,信道5、16和25中的信號帶寬與載頻相加,超過了濾波器的通帶范圍,導致信號進入了臨近信道。所以,后續(xù)通過門限判決將泄漏的信號剔除,從而正確偵收到10個信號。

圖11 DAC輸出大帶寬信號頻譜Fig.11 DAC outputs large bandwidth signal spectrum

圖12 信道化處理結(jié)果Fig.12 Channelized processing results

對于干擾功能測試,上位機將相關參數(shù)和發(fā)射波形數(shù)據(jù)下發(fā)到FPGA端,并完成參數(shù)裝訂,后續(xù)只需要更改相位碼元序列和轉(zhuǎn)發(fā)次數(shù)即可完成干擾模式的切換。波形數(shù)據(jù)通過一路DAC完成插值和數(shù)字上變頻自回環(huán)到一路ADC,采集的數(shù)據(jù)完成抽取和下變頻后,經(jīng)過序列編號和儲存后,由相關干擾模式將編號數(shù)據(jù)再經(jīng)由另一路DAC完成干擾數(shù)據(jù)的輸出。同時,為了增加干擾覆蓋范圍,在脈沖之外自由組合轉(zhuǎn)發(fā)已編號切片數(shù)據(jù)。采1 μs轉(zhuǎn)發(fā)1 μs的間歇采樣直接轉(zhuǎn)發(fā)干擾如圖13所示。采1 μs轉(zhuǎn)發(fā)3 μs的間歇采樣重復轉(zhuǎn)發(fā)干擾如圖14所示。并且附帶脈沖外轉(zhuǎn)發(fā)4 μs,為采1 μs轉(zhuǎn)發(fā)3 μs并帶有隨機2PSK相位調(diào)制的間歇采樣重復轉(zhuǎn)發(fā)干擾和脈沖外轉(zhuǎn)發(fā)40 μs如圖15所示。

圖13 間歇采樣直接轉(zhuǎn)發(fā)干擾Fig.13 Intermittent sampling directly transmit jamming

圖14 間歇采樣重復轉(zhuǎn)發(fā)干擾Fig.14 Intermittent sampling repetitive transmit jamming

圖15 間歇采樣隨機相位調(diào)制重復轉(zhuǎn)發(fā)干擾Fig.15 Intermittent sampling random phase modulation repetitive transmit jamning

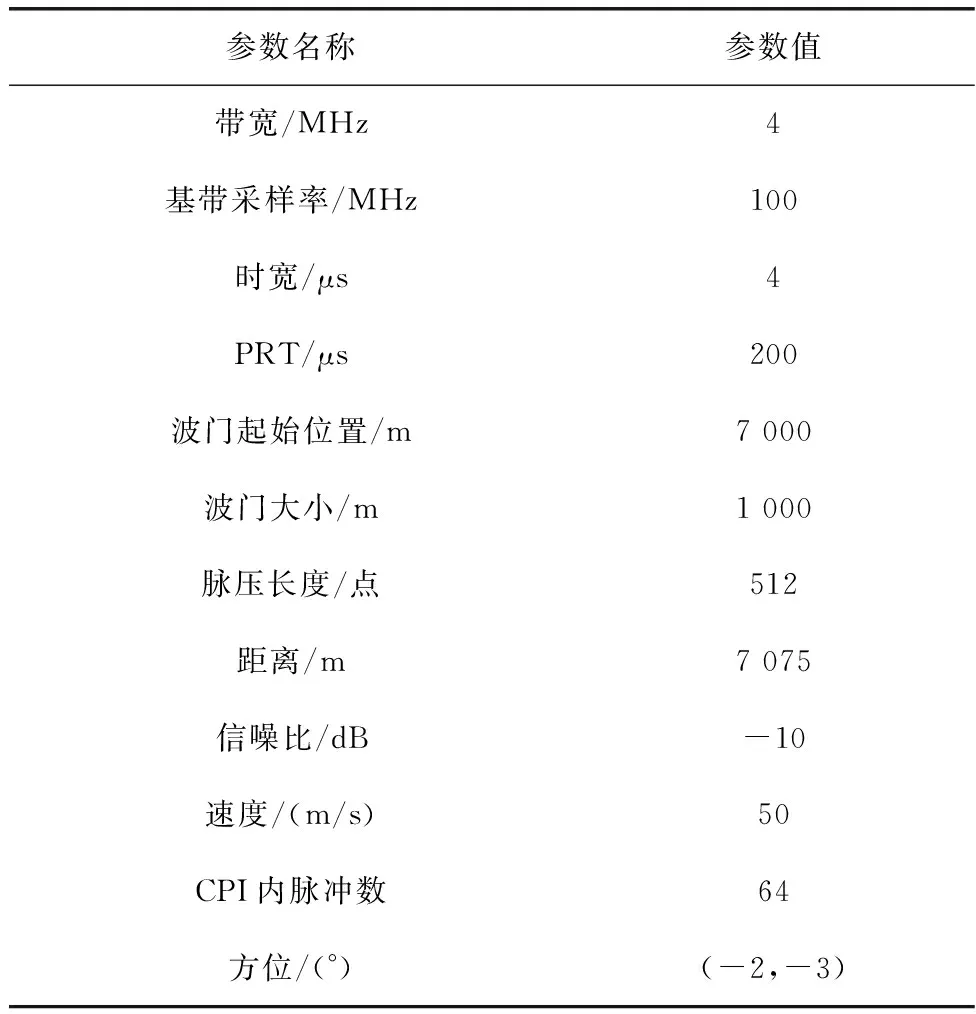

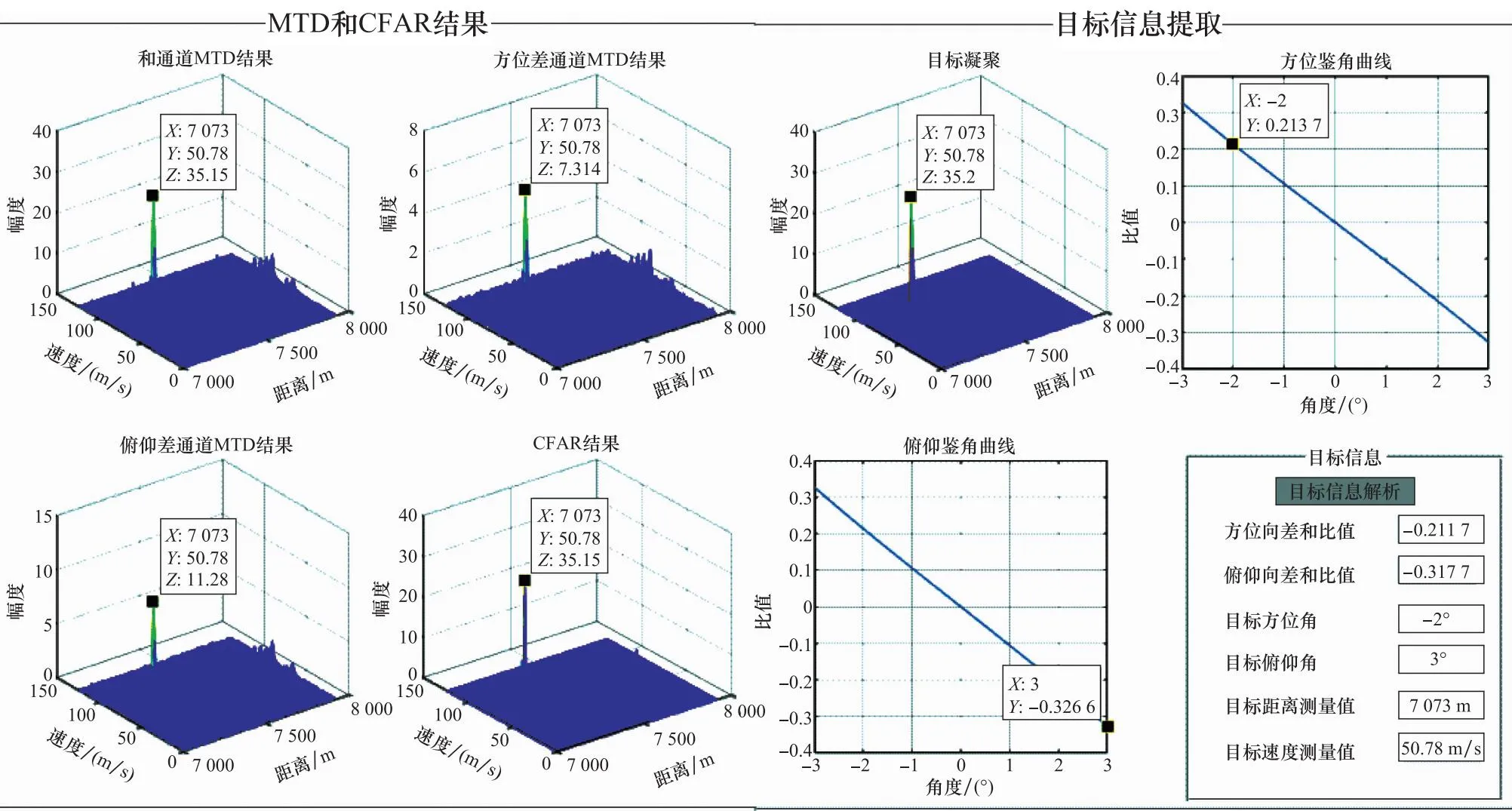

對于探測功能測試,主動MIMO雷達相關測試參數(shù)如表4所示。

表4 探測功能目標參數(shù)設置Table 4 Detection function target parameter settings

首先,四路DAC將四路正交的波形發(fā)射到天線陣元,再由ADC采集天線陣元接收回來的四路數(shù)據(jù),經(jīng)由在FPGA端兩級波束形成和脈沖壓縮處理,再由ARM端完成目標識別算法,最后得到的目標信息結(jié)果如圖16所示。可以看出,得到的目標速度、距離和方位信息與設定信息一一對應。

圖16 主動MIMO雷達探測測試結(jié)果Fig.16 Active MIMO radar detection test results

所以,軟件一體化在硬件一體化的基礎上更進一步地節(jié)省了系統(tǒng)的空間需求,能夠帶來更具有靈活性、便攜性的性能優(yōu)勢。

6 結(jié) 論

本文從3種功能軟件一體化需求出發(fā),提出了一種新的集成硬件微系統(tǒng)實現(xiàn)多功能方案,通過對后摩爾時代下的多種先進封裝技術(如三維堆疊、金絲引線鍵合、IPD、RDL等)進行混合集成應用,將多通道RF直采的DAC/ADC、FPGA、ARM以及多功能儲存芯片MCP等器件進行共封裝集成設計,形成具有性能高、體積小以及多功能的信號處理SiP芯片,并針對該芯片完成了多通道ADC和DAC的隔離度、幅相一致性、無雜散動態(tài)范圍和有效位數(shù)等相關性能參數(shù)的測試驗證。最后,基于該芯片構(gòu)建了偵察、干擾和探測多功能一體化軟件應用場景,并完成驗證。結(jié)果表明,本文研究的偵干探多功能一體化微系統(tǒng)可靈活實現(xiàn)多功能一體化功能,并兼有體積小、重量輕以及多功能、高性能的優(yōu)越性能,驗證了方案的可行性與工程應用價值,具有較好的應用前景。