基于SerialLiteⅡ協議的磁共振采集數據傳輸系統設計

摘 "要: 磁共振成像(MRI)是一種無創檢測人體內部結構的技術,隨著接收通道數量增多,產生的采集數據量越來越大,給快速成像帶來了巨大的挑戰。文中設計一種基于SerialLite Ⅱ協議的磁共振采集數據傳輸系統。系統功能主要由FPGA實現,分為數據緩存模塊和數據傳輸模塊兩類,數據緩存模塊基于雙緩存區和狀態機控制的乒乓操作,有效地解決了因數據量大而帶來的讀寫沖突問題;數據傳輸模塊基于FPGA建立SerialLite Ⅱ數據傳輸鏈路,實現了采集數據的光纖傳輸。通過仿真和實驗驗證了系統功能的正確性,表明其能夠實現磁共振采集數據的高速穩定傳輸。

關鍵詞: 磁共振成像; SerialLite Ⅱ協議; 數據傳輸; "無創檢測; FPGA; 數據緩存; 光纖傳輸

中圖分類號: TN751.1+1?34 " " " " " " " " " " " "文獻標識碼: A " " " " " " " " " " "文章編號: 1004?373X(2024)06?0085?06

Design of magnetic resonance acquisition data transmission system based

on SerialLite Ⅱ protocol

XIAO Liang, YUAN Jiahui, XING Cangju

(College of Information Science and Technology, Beijing University of Chemical Technology, Beijing 100029, China)

Abstract: Magnetic resonance imaging (MRI) is a non?invasive technology for detecting the internal structure of human body. As the number of receiving channels increases, the amount of collected data generated increases, which brings huge challenges to rapid imaging. A magnetic resonance acquisition data transmission system based on the SerialLite Ⅱ protocol is designed. The system functions are mainly implemented by FPGA and are divided into data cache module and data transmission module. The data cache module is based on double buffer area and state machine controlled ping?pong operation, which effectively solves the problem of read and write conflicts caused by large data volume. The data transmission module is used to establish a SerialLite Ⅱ data transmission link based on FPGA, so as to realize optical fiber data transmission of collected data. The simulation and experiments verifies the correctness of the system functions, showing that it can achieve high?speed and stable transmission of magnetic resonance acquisition data.

Keywords: magnetic resonance imaging; SerialLite Ⅱ protocol; data transmission; non?invasive detection; FPGA; data caching; fiber optic transmission

0 "引 "言

磁共振成像(Magnetic Resonance Imaging, MRI)是一種利用磁場和射頻波對人體內部結構進行無創檢測的技術,具有高分辨率、高對比度、多參數和多維度等優點,被廣泛應用于醫學診斷與神經認知研究等領域[1?2]。隨著磁共振成像技術的發展,其采集數據傳輸面臨著接收通道數量多與快速成像等挑戰,傳統的基于同軸電纜的方案難以滿足這些需求,影響了磁共振成像的性能。因此,研究高速、穩定的磁共振成像采集數據的傳輸系統具有重要的意義與價值。

MRI系統的控制核心是成像譜儀,傳統的方法是數據采集裝置與譜儀集成在一起,通過同軸電纜將回波信號從屏蔽間的接收線圈傳送到譜儀進行采集,然而,同軸電纜的傳輸存在衰減、易受干擾等缺點。為克服這個缺點,當前的研究趨勢是將采集裝置與成像譜儀分離,置于接收線圈邊上,通過光纖傳輸數據。國內外學者提出了多種基于光纖的磁共振信號傳輸方案。凱斯西儲大學的研究團隊A. Simonsen等人提出了一種三角積分調制光纖傳輸方案[3],實現了回波數據的數字光纖傳輸,但其一路光纖只能傳輸一個通道信號,每個光纖通道都要配置相應的調制器和光纖收發模塊,實現起來比較復雜。國內華中師范大學姚俊江等研究了基于自定義通信協議的磁共振數據光纖傳輸[4],降低了系統復雜度,但其方案缺少數據錯誤檢測和流控制等鏈路穩定功能。Tang Weinan等提出了基于FPGA與Aurora協議的數據傳輸方案[5],但該協議沒有差錯控制機制,需要編寫額外的數據判斷模塊保證傳輸可靠性[6],導致FPGA編程較為復雜。

當采集通道數量與一行采樣點數較多時,對采集數據的存儲提出了很高的要求,例如通道數量為32,一行的采樣點數為1 024,則所需的存儲容量為32×1 024×4=128 KB(一個點包括16 bit的I與Q分量,需4 B),這占用了大量的存儲資源。

為了適應磁共振成像系統多通道與快速成像的要求,實現磁共振采集數據的高速可靠傳輸,本文設計一種基于SerialLite Ⅱ協議的磁共振數據傳輸系統,實現數據采集與成像譜儀分離,以及由光纖傳輸數據。SerialLite Ⅱ協議是一種高速串行通信協議,具有低延遲和高可靠性的特點。本系統基于FPGA構建SerialLite Ⅱ協議數據傳輸鏈路,實現了采集數據的光纖傳輸;同時,為了減少對存儲區的占用,還設計了一種基于雙緩存區和狀態機控制的乒乓操作數據緩存系統,實現了采集數據的高效存儲。通過軟件仿真和實際測試,驗證了系統的功能和傳輸性能。

1 "系統硬件平臺

磁共振成像采集數據傳輸系統的總體框圖如圖1所示。系統由數據采集模塊和數據傳輸模塊兩部分組成。系統與采集裝置通過局部總線連接,與成像譜儀之間通過光纖連接。回波信號經過信號采集模塊的低噪聲放大、信號濾波、模數轉換和數字下變頻處理后,被存儲在數據緩存模塊的存儲單元中。數據傳輸模塊負責將存儲的數據通過SerialLite Ⅱ協議由光纖鏈路傳輸到成像譜儀,再由譜儀傳送到上位機進行圖像重建。

目前采集裝置配置4個接收通道,這個數量可以比較方便地擴展到32甚至更高,以適應多通道成像的需求。

1.1 "FPGA

本文選用Intel公司ArriaIIGX系列的EP2AGX65芯片作為FPGA器件。該芯片擁有65 000個邏輯單元(LE),具有高密度的邏輯功能和存儲器資源,采用了獨特的自適應邏輯模塊(ALMs)結構,可提高邏輯資源的利用率。此外,該芯片具有SerialLite Ⅱ協議IP核,支持600 Mb/s~6.375 Gb/s的數據傳輸速率,為實現數據的高速、穩定和高可靠光纖傳輸提供了硬件基礎。FPGA通過PCML差分管腳與SFP光纖模塊直接連接,進行數據的高速發送與接收。

1.2 "時鐘設計

為了保證磁共振射頻發射與接收的相干性,系統采用譜儀的時鐘作為時鐘源。譜儀的時鐘采用高精度高穩定度的恒溫晶振,其頻率為60 MHz。時鐘信號通過光纖發送到系統,由SFP光模塊將光信號轉換為LVDS電平的電信號,再通過專用差分管腳輸入FPGA。通過FPGA該時鐘信號被分配到三個不同的功能模塊:第一個功能模塊是信號采集模塊的控制模塊,它負責控制信號的采集和處理;第二個功能模塊是一分四時鐘驅動芯片CY2304NZ,它將單路時鐘信號分成多路相位相同的時鐘信號,作為信號采集模塊中模數轉換器件和數字下變頻器件的工作時鐘;第三個功能模塊是鎖相環模塊,它根據不同的功能需求,輸出多個不同頻率的時鐘信號。

2 "系統功能設計

2.1 "基于乒乓操作的數據緩存系統設計

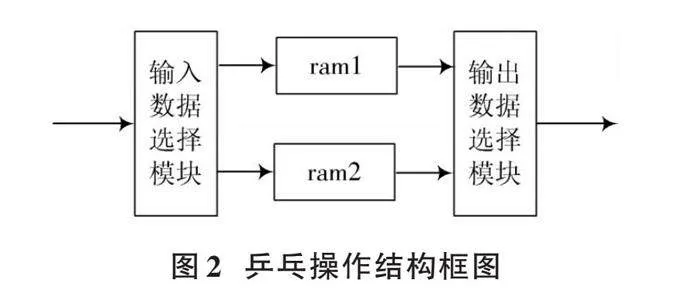

乒乓操作是一種控制數據緩存單元的讀寫周期切換,從而實現數據連續傳輸的有效策略,是常用的緩存數據交換技術[7?9]。其基本原理是:將輸入的數據流通過輸入數據選擇單元,按照時間順序分配到兩個數據緩存區。如圖2所示,乒乓操作結構包括兩個數據緩存模塊ram1和ram2,以及一個輸入數據選擇單元和一個輸出數據選擇單元。在每個緩存周期內,輸入數據選擇單元將輸入的數據流寫入到一個數據緩存模塊中,同時輸出數據選擇單元將另一個數據緩存模塊中的上一個周期的數據讀出,并傳送給下游信號處理模塊。例如,在第1個緩存周期,輸入的數據流被寫入到ram1中,而ram2中沒有數據;在第2個緩存周期,輸入數據選擇單元切換到ram2,將輸入的數據流寫入到ram2中,同時輸出數據選擇單元從ram1中讀出第1個周期的數據并傳送出去;在第3個緩存周期,輸入數據選擇單元再次切換到ram1,將輸入的數據流寫入到ram1中,同時輸出數據選擇單元從ram2中讀出第2個周期的數據并傳送出去。這樣循環進行,就可以實現無間斷的數據存儲傳輸,從而可以避免因為寫入操作耗時而導致的數據丟失風險,提高系統性能和數據可靠性。

在FPGA的實現中,數據緩存系統由兩個實例化的RAM組成,分別作為兩個數據存儲單元,命名為“data_ram1”和“data_ram2”。這兩個RAM通過端口連接其各自的信號,實現了數據的輸入和輸出。其中,“rden1”與“rden2”為讀使能輸入,“wren1”與“wren2”為寫使能輸入,“address1”與“address2”為內存地址,“data1”與“data2”為數據,“txrdp_clk”與“txrdp_clk”表示時鐘輸入,“q1”與“q2”表示數據輸出。

如圖3所示,數據緩存系統的讀寫操作過程如下:首先,程序初始化,讀寫操作切換標志信號pingpang_select置為低電平,此時數據存儲單元ram1處于寫狀態,ram2處于空閑狀態。ram1的寫地址由采集數據計數器產生的連續地址決定,當計數器的值達到設定的采集點數時,讀寫操作切換標志信號pingpang_select翻轉電平,進入下一個讀寫操作周期。此時,數據存儲單元ram1處于讀狀態,ram2處于寫狀態。ram1的讀地址由發送數據計數器產生,將ram1輸出的數據傳輸至數據發送模塊;ram2的寫地址由采集數據計數器產生,將新采集的數據寫入ram2中。當采集數據計數器再次達到設定的采集點數時,讀寫操作切換標志信號pingpang_select再次翻轉電平,以此類推進行輪換。通過這種方式,實現了數據在兩個RAM之間的交替存儲和讀取。

在傳統的數據傳輸過程中,數據流的速度可能會超過數據傳輸模塊編碼封裝的速度,導致數據包丟失的情況頻繁發生。而乒乓操作通過引入緩存區,提供了更為靈活和可靠的解決方案。乒乓操作的主要優點有三個方面:一是通過暫存數據,防止數據丟失;二是緩解下游模塊壓力,通過同時進行讀寫操作,減少下游模塊的等待時間;三是緩解數據堵塞問題,通過合理安排讀寫請求的順序和時間,保持數據的流暢傳輸。

2.2 "SerialLite Ⅱ協議實現

SerialLite Ⅱ協議是一種輕量級點對點串行傳輸協議,它的特點是邏輯單元的消耗低、數據傳輸的延時小,能夠支持單通道高達3.125 Gb/s的數據傳輸速率,具有簡單易實現、可靠高效、靈活可擴展等優勢[10?13]。SerialLite Ⅱ協議由鏈路層和物理層兩個層次組成。鏈路層負責將上層數據封裝成包,并在包頭和包尾添加控制信息,如起始標志、結束標志、長度字段、CRC校驗等,以保證數據的完整性和正確性。物理層負責將鏈路層的數據進行編碼,以便在物理介質上進行傳輸,并在接收端進行解碼,恢復原始數據。

本設計中SerialLite Ⅱ傳輸鏈路設置為單向鏈路,鏈路通道寬度為16 bit,鏈路層和物理層使用相同的60 MHz時鐘源,通道傳輸數據速度為1 920 Mb/s。SerialLite Ⅱ單向鏈路具有自動同步機制,它可以使發送端和接收端在沒有外部訓練序列的情況下,快速地建立并維持數據傳輸的同步狀態。該機制的原理是:利用物理層的編碼方式,在數據中嵌入特殊的控制信息,使得接收端可以根據這些信息來檢測和調整數據的對齊和時鐘。SerialLite Ⅱ單向鏈路的自同步鏈路建立過程如下:首先,發送端在開始傳輸數據之前,先發送一段特殊的控制信息,稱為K28.5字符,該字符由10位組成,其值為0011110100。接下來,接收端在接收到數據后,對其進行解碼,并檢測是否存在K28.5字符,如果接收端檢測到K28.5字符,則說明發送端已經開始傳輸數據,并且已經完成了對齊和時鐘恢復;如果接收端沒有檢測到K28.5字符,則說明發送端還沒有開始傳輸數據,或者數據存在錯位或失鎖的情況。最后,接收端根據檢測到的K28.5字符的個數和位置,來調整數據的對齊和時鐘恢復,接收端在完成數據對齊和時鐘恢復后,就可以正常地接收和解析數據包。

2.3 "數據傳輸系統設計

當信號采集開始信號有效時,進入開始采集狀態,信號采集板上的FPGA讀取各采集通道輸入的回波數據,根據讀寫操作切換標志信號的狀態,將經過數字正交解調等處理后的數據存儲至相應的數據緩存模塊內;當采集到的數據量達到設定的采集數量,發送數據開始信號置高電平有效,持續4個時鐘周期,以便數據發送模塊正確識別。

數據發送模塊有5個狀態:空閑狀態、發送數據包頭狀態、發送數據狀態、發送數據包尾狀態和暫停發送狀態。數據傳輸發送時序狀態機如圖4所示,系統上電復位后,發送模塊狀態機首先進入空閑狀態,等待數據發送開始信號以及數據有效信號txrdp_dav為高。當這兩個信號都為高時,狀態機進入發送數據包頭狀態,此時置高數據包開始信號txrdp_sop,并將數據包頭信息發送到光纖接口。當數據包頭信息發送完成后,狀態機進入發送數據狀態,此時置低txrdp_sop,并將數據包有效數據發送到光纖接口。若此時txrdp_dav信號為低,表示沒有更多的有效數據,狀態機進入暫停發送狀態,此時保持當前的輸出信號不變,并等待txrdp_dav信號恢復為高。當發送有效數據的字節數達到預設的數據包大小時,狀態機進入發送數據包尾狀態,此時置高數據包結束信號txrdp_eop,并將數據包尾發送到光纖接口。當數據包尾發送完成后,狀態機返回空閑狀態,等待下一次數據傳輸。

3 "系統測試

3.1 "功能仿真

為了驗證數據緩存系統的功能,本文使用ModelSim軟件對系統進行了功能仿真。仿真的過程如下:首先,設置每個緩存周期存儲8個16 bit數據,輸入數據流為從0~31的遞增數列;然后,啟動程序觀察數據緩存系統的讀寫操作過程。圖5所示為數據緩存系統的讀寫操作切換標志信號pingpang_select的變化情況。由圖5可知:每當采集數據計數器達到8時,pingpang_select就會翻轉電平,從而切換數據存儲單元ram1和ram2的讀寫狀態;輸入數據流根據pingpang_select的狀態分流存儲,輸出數據流與輸入數據流一致,數據緩存系統交替存儲和讀取數據工作正常。

對于數據傳輸系統,同樣在ModelSim軟件中對其進行了功能仿真。設置發送數據包大小為8×16 bit,發送數據包個數為2。如圖6所示,在發送端,當數據有效信號dav為高電平時,進入數據包發送狀態,直到發送數據數量達到數據包大小,當前數據包發送完成;在接收端,識別到數據包開始信號sop有效時,開始往數據存儲單元存入數據,直到識別到數據包結束信號eop為高電平,表示當前數據包接收完成。

3.2 "數據緩存系統功能測試

為了驗證數據緩存系統的實際工作情況,設置采樣點數為256,采樣通道數為2,使用Quartus Ⅱ的嵌入式邏輯分析儀Signal?Tap對乒乓操作緩存系統主要信號進行抓取,結果如圖7所示。

當讀取切換標志信號pingpang_select電平翻轉后,兩個數據緩存單元的讀寫狀態正確切換,數據流被成功緩存到相應存儲區。

在Quartus Ⅱ的In?SystemMemoryContentEditor工具中,分別查看數據緩存單元ram1及ram2與接收數據緩存單元的存儲數據內容。

結果表明,數據緩存單元ram1和ram2的存儲數據內容與圖7信號數據一致,數據存儲正確,未出現數據丟失。接收數據緩存單元的存儲數據內容由ram1及ram2的存儲數據組成,輸出數據正確連續,說明乒乓操作數據緩存系統功能完整且正確。

3.3 "數據傳輸系統功能測試

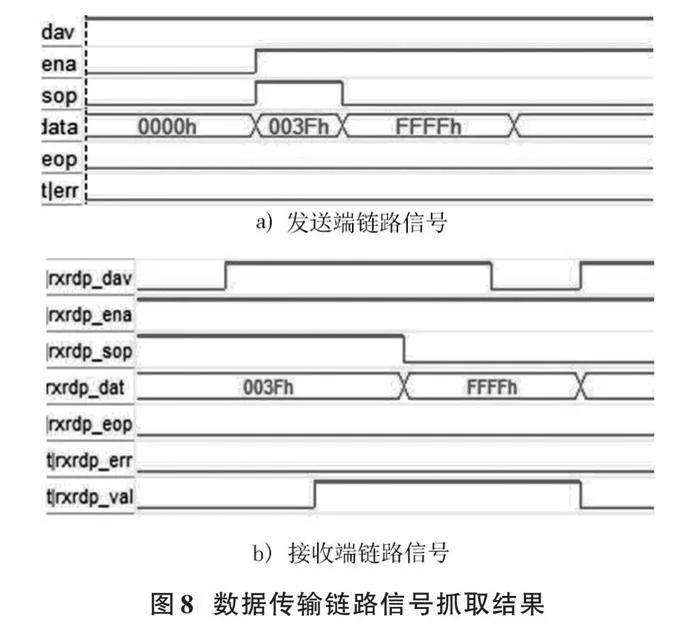

數據傳輸過程中,在發送端與接收端使用Signal?Tap對鏈路信號進行抓取,圖8為信號抓取結果。

圖8中數據包大小為64×16 bit,發送端與接收端發送的數據與數據緩存系統中存儲的數據一致,重復多次測試結果均準確無誤,與仿真結果相符,驗證了SerialLite Ⅱ協議數據傳輸的正確性。

在發送端發送第一個有效數據和接收端接收完最后一個有效數據時,各發出一個脈沖信號,用示波器測量這兩個脈沖的時間間隔。測試結果表明,當采用4個接收通道,每個通道一行采集1 024個點(這樣一行總的數據量為16 KB),所需的傳輸時間平均約為91.16 μs,傳輸速率約為1.44 Gb/s。

3.4 "信號采集測試

通過信號發生器產生一個中心頻率8.6 MHz,幅度為30 mV,調制頻率為500 Hz,調制深度為100%的調制三角波信號,由信號采集系統模塊采集處理后,解調得到2 048個16 bit的I、Q數據,經由數據緩存與傳輸系統最后上傳至用戶計算機,在計算機的掃描軟件中可以看到采集的I、Q數據波形,如圖9a)所示,數據的幅度圖如圖9b)所示。由圖可知,波形連續無波動,說明系統的數據存取連續,數據傳輸無誤。

4 "結 "語

本文設計了一種基于SerialLite Ⅱ協議的磁共振采集數據傳輸系統,實現了數據的乒乓存儲和光纖傳輸。數據緩存系統基于乒乓操作,有效解決了因數據量大而帶來的讀寫沖突問題,實現了磁共振數據寫入與讀取的同步進行,提高了系統工作效率和可靠性。在發送端和接收端建立SerialLite Ⅱ數據傳輸鏈路,實現了磁共振數據的高速穩定傳輸,提高了傳輸性能和穩定性。通過仿真和實驗驗證了系統功能的正確性與穩定性,表明其能夠滿足磁共振成像數據傳輸的需求,為高性能成像譜儀的研制提供了技術支撐。

目前尚未在實際的磁共振成像系統上對所設計系統進行測試和應用,在未來的工作中將加快在實際系統上的成像實驗,以驗證系統的實用性。

注:本文通訊作者為邢藏菊。

參考文獻

[1] KIM Y, CHENG S S, DIAKITE M, et al. Toward the development of a flexible mesoscale MRI?compatible neurosurgical continuum robot [J]. IEEE transactions on robotics, 2017, 33(6): 1386?1397.

[2] WOODS J C, CONRADI M S. 3He diffusion MRI in human lungs [J]. Journal of magnetic resonance, 2018, 292(7): 90?98.

[3] SIMONSEN A, S?NCHEZ?HEREDIA J D, SAARINEN S A, et al. Magnetic resonance imaging with optical preamplification and detection [J]. Scientific reports, 2019, 9(1): 18173.

[4] 姚俊江,胡晉杰,蔣瑜.磁共振成像中數字光纖傳輸技術研究[J].信息技術,2017(12):121?124.

[5] TANG W N, WANG W M, LIU W T, et al. A home?built digital optical MRI console using highspeed serial links [J]. Magnetic resonance in medicine, 2015, 74(2): 578?588.

[6] Xilinx Corporation. Aurora 64B/66B LogiCORE IP product guide (v12.0) [EB/OL]. [2022?01?14]. https://docs.xilinx.com/r/en?US/pg074?aurora?64b66b/Aurora?64B/66B?v12.0?LogiCORE?IPProduct?Guide.

[7] 毛雨陽,劉一清.基于FPGA的多路磁共振信號采集設計[J].電子測量技術,2018,41(14):128?133.

[8] 王炳友,黨博,黨瑞榮,等.基于FPGA的多通道出砂振動信號緩存系統研究[J].石油化工應用,2021,40(4):98?104.

[9] 趙越,余紅英,王一奇.一種高速數據存儲方法的設計與驗證[J].數據采集與處理,2021,36(2):384?390.

[10] 譚磊,李益,付建國.基于異構多核平臺的數據傳輸方法研究與實現[J].科學技術創新,2021(1):61?63.

[11] Altera Corporation. Serial lite Ⅱ protocol reference manual [EB/OL]. [2022?04?12]. https://www.altera.com.

[12] Altera Corporation. Serial lite Ⅱ IP core user guide [EB/OL]. [2022?01?21]. https://www.intel.com/content/www/us/en/docs/programmable/683179/16?1?16?1/seriallite?ii?ip?core?overview.html.

[13] 張天寧,雷展智,肖亮.基于SerialLiteⅡ協議的磁共振成像數據傳輸系統設計[J].波譜學雜志,2023,40(2):179?191.