基于FPGA的智能電網監控系統數據集中器設計

[關鍵詞]FPGA ;智能電網;監控系統

[中圖分類號]TM76 [文獻標志碼]A [文章編號]2095–6487(2024)10–0044–03

在智能電網數據監控系統中,數據集中器具有連接作用,可使應用端和監控端相互連接。在分布式電源大量接入電網后,電網系統所需處理的數據快速增加,而現場可編程門陣列(FPGA,Field-Programmable Gate Array)擁有強大性能,將其作為基于設計數據集中器,可強化裝置應用效果,是保證電網監控系統實時處理數據的重要舉措。因此,研究此項課題,具有十分重要的意義。

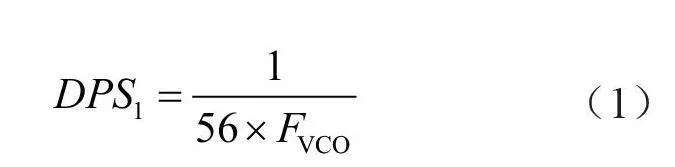

1框架設計

數據集中器總體架構如圖1所示。

1.1子卡和數據集中器通信

所設計的數據集中器和子卡,在通信過程中需要將數據與交易通信協議DTC(Data and" Trading" Cpmmunications Protocol)作為基礎。其中,處于傳遞狀態下的信號數量為4 個,分別為時鐘、觸發、數據和應答請求。子卡在發送數據過程中,集中器會利用80Mbps 的DTC_TRIG 時鐘信號控制數據,其中,DTC 信號的方向和比特率如圖2 所示。時鐘同步控制時所應用的時鐘信號為40MHz的DTC_CLK,通過該信號,使數據輸出的準確性得到保證。子卡向數據集中器發送數據信息,使用信號80 Mbps 的DTCDATA。子卡在確認數據傳輸是否到位時,應用信號為80 Mbps的DTC-RETURN[1]。

在數據集中器內,上述信號會在子卡之間傳遞,且在傳輸時,應用形式均為差分信號。究其原因,主要是此類傳輸信號,可規避信號干擾,使信號穩定性增強。

1.2命令接口設計

命令在通信過程中主要將DCS接口作為媒介,首先由監控端發送分散控制系統DCS(Distributed Control systrm)命令,接收方為數據集中器,在對該命令讀取后,方能響應。但回復存在延時性,并不會立即執行,在結果內存中被存儲,之后,通過讀取結果,確定DCS命令,最終回復。

2時鐘設計

2.1時鐘網絡

時鐘網絡由多個模塊組成,具體如下。

(1)輸入緩沖器IBUFGDS(Differential Signaling lnput Buffer with Selectable l/O" interface),屬于FPGA的重要模塊,其具有對轉功能,可使輸入端所接收的差分時鐘變為主時鐘,為后續輸出創造有利條件[2]。

(2)時鐘管理模塊,可對各種時鐘信號加以處理。同時,模塊在接收復位信號后,會對時鐘信號做復位處理,當信號保持穩定后,鎖定信號會同步生成,該信號可表示主時鐘brdclk 的可用性。

(3)模塊接收時鐘信號后,會生成復位信號,該信號可使相移控制模塊位置復原。

2.2 跨時鐘區域同步

亞穩態問題的出現,會導致時鐘網絡內模塊無法發揮相移控制作用,針對此類問題,處理措施如下。

(1)對雙觸發器加以應用,使其成為同步器,其原理為通過對時鐘周期做延遲處理,使亞穩態信號的穩定性增強,變為穩態信號,但該方法無法從根源上解決問題。

(2)利用先進先出的存儲器,使信號輸出更加有序,該方法適用范圍有限,僅在處理多源數據時有效。

(3)利用二級寄存器,將其作為全局復位信號輸出。

基于實際情況,將上述3 種處理措施作為基礎,對異步信號寄存同步方法加以應用。

在傳入相位同步指令后,此時,其值為1,利用選擇器將其輸出至觸發器,由觸發器對指令轉化,使其成為send_pscmd信號。在信號撤銷后,同時控制模塊未處在空閑狀態時,將觸發器輸出信號返回,以此鎖定信號,避免信號在操作前出現問題。此外,還會通過觸發器時鐘,使時鐘域同步目標達成。研究結果表明,文章所提出的方法,可使亞穩態問題被完全規避[3]。

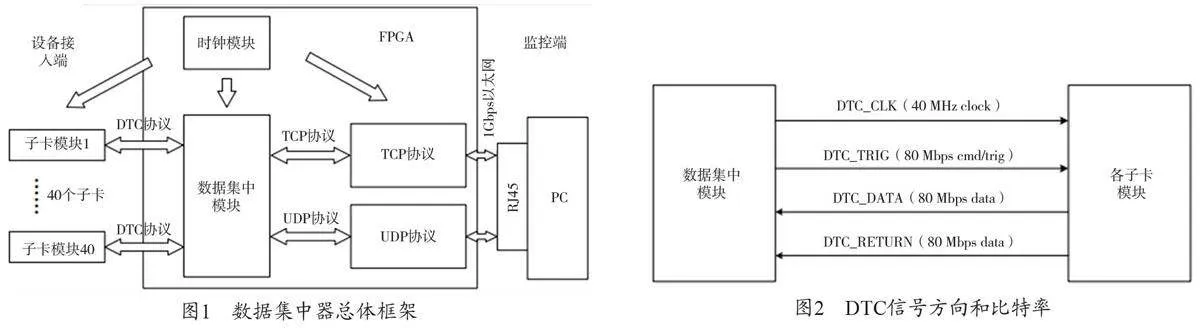

本研究在對IP核處理時,對內部電壓振蕩工作頻率FVCO(Frequency of VCO,VCO)設置, 將其數值確定為1000MHz,周期為1ns。各次移動大小相同, 均為電壓振蕩器工作周期的1/56,此時,可利用下述公式計算一次動態相移操作移動的分辨率DPS1(Dynamic Phase Shift),計算結果為17.86ps。

文章所設計的數據集中器,可為精準相移提供支持的輸出時鐘頻率為10MHz和40MHz。

3"TCP和UDP模塊設計

智能電網運行對數據傳輸質量提出非常高的要求,其中,TCP和UDP屬于協議模塊,可以為傳輸控制協議模塊協議傳輸數據提供支持。TCP模塊雖然能保證通信質量,但存在一定缺陷,具體表現為傳輸數據同時,額外數據傳輸會同步產生。故在本研究中,主要被用于監控命令信息傳輸,究其原因,主要是此類信息對傳輸質量的要求較為嚴格。而UDP作為傳輸層協議無須連接,且不會產生額外數據傳輸,故在本研究中,被應用于傳遞應用數據[4]。

3.1物理接口

FPGA所提供的EMAC能夠實現千兆以太網,故其應用有助于保證數據傳輸效率。EMAC所提供的物理接口選項包括五種,各接口說明如下。

(1)MII接口。該接口提供的以太網連接速率較低,處在10~100Mb/s。

(2)CMII和RGMII接口。CMII 接口具有可拓展的特點,在經過拓展后,以太網連接速率高達1Gb/s。相較于CMII,RGMII接口通過對觸發器的應用,使接口引腳使用數量減少,減少量約為一半。

(3)SGMII接口。SGMII接口傳輸速率較高,可達1 Gb/s,且能利用串行接口,對并行接口取代,因此,可在最大限度上控制引腳使用量,同時PCB布局對引腳的需求量和難度會隨之降低。

在上述接口應用后,會激活FPGA 提供的高速收發器子層。對于應用SGMII的PCS子層,其傳輸率和觸發器對時鐘校準要求較高。為此,本研究對差分時鐘予以利用,其目的是準確校準觸發時鐘。

針對傳輸速率高的以太網通信,主要通過電纜完成數據傳輸,與設計傳輸速率相比,實際傳輸速率更高,可達1.25Gb/s。本次設計的集中器,在編碼和解碼數據處理方面,為提升處理效率,分別使用8B/10B編碼器和10B/10B解碼器。研究結果表明,上述裝置的應用,有利于縮短以太網幀傳輸和接收時間。其中,8B和10B分別表示以太網幀和電纜傳輸數據寬度。拋開以太網幀內容不談,10B數據流0和1均相等,能夠使直流相互平衡,并規避電信號波動對以太網數據傳輸造成的影響。考慮10B數據信號與時鐘之間,具有高度一致性,故該信號在時鐘恢復和字對齊時,亦能發揮良好的作用。

3.2MAC內核

MAC內核在本設計中,主要用于連接物理層。針對三模以太網訪問控制器,所采用的內核包括兩種,分別為硬內核和軟內核。其中,硬內核與數字信號處理器、鎖相環等模塊較為相似,屬于FPGA 的重要組成部分。鎖相環模塊所處位置是FPGA的功能模塊,其擁有諸多方面的應用優勢,具體表現為簡便性和穩定性優越。而軟內核,并未在功能模塊中固化,而是通過開發代碼的方式設計功能,其靈活性優勢顯著。相較于軟內核,硬內核的特征更加鮮明,主要體現在以下方面。

(1)在條件允許的情況下,硬內核支持超頻操作,這里所說的超頻,其頻率超過2.5GB/s。

(2)軟內核在開發源代碼的過程中,所損耗的資源較多,而這些資源在其他功能設計中亦可被應用。

建議設計過程中,將硬內核作為首選。若FPGA不包括硬內核,同時需要使用內核,則采用軟內核。而文章所基于的FPGA 擁有硬內核,故對其加以應用。

在完成上述設計后,對集中器應用效果進行檢測,本次檢測內容包括子卡通接口、時鐘同步測試和TCP與UDP模塊測試。本次測試所應用的平臺為woreshark,該平臺屬于免費且專業的網絡協議分析裝置,將其作為測試平臺,有助于協議進行字節上的調節。測試結果表明,文章所設計的數據集中器,功能十分完善,在智能電網監控系統中應用,可對1Gbp/s的吞吐量進行監測,同時,還能提高事件傳輸率,其速度高達每幀KHz。此外,子卡通接口和時鐘同步測試結果均與設計要求相吻合,具有應用可行性[5]。

4結束語

在能源問題日益嚴峻的背景下,智能電網快速發展,但如何處理并網所產生的海量數據,成為制約智能電網發展的重要因素。而FBGA因具有良好的性能,被廣泛應用于各領域,將其作為基礎,設計數據集中器,并將其應用于監控系統中,有助于提升數據處理效率和質量。文章基于FPGA 對集中器的整體框架進行設計,包括子卡和數據集中器通信和命令接口設計,之后設計集中器的時鐘、TCP和UDP模塊,通過科學合理的設計方法,使時鐘控制信號生成問題被有效解決。而針對TCP和UDP模塊,鑒于二者具有相似性,故以物理接口和MAC內核為切入點進行設計,最終完成設計目標。文章所設計的基于FPGA 的智能電網監控系統數據集中器應用效果良好,可為相關行業提供借鑒。