SpaceWire CODEC的容錯設計和實現

程照強,劉淑芬

(北京控制工程研究所,北京 100190)

SpaceWire[1]是由ESA推出的專門面向航天應用的高速總線,它以IEEE 1355-1995和LVDS標準(ANSI/TIA/EIA-644)為基礎,同時在錯誤處理方面有更好的支持.其基本特點是串行、高速(200Mbit/s)、全雙工.SpaceWire CODEC(encoderdecoder)是SpaceWire協議控制器的主要組成部分,主要完成對數據的編碼發送和解碼接收.SpaceWire CODEC的組成中包含寄存器以及存儲器單元,這些單元存儲著系統的狀態、控制信息、數據等,在空間環境中高能粒子的影響下容易發生單粒子翻轉(SEU,single event upset)、單粒子功能中斷(SEFI,single event functional interrupt)等,尤其在基于FPGA的實現方式中,這些存儲單元更容易受到SEU、SEFI的影響.為了保證產品在軌正常工作,必須對SpaceWire CODEC進行容錯設計以減緩SEU、SEFI等單粒子效應的影響.

1 SpaceWire CODEC及容錯性能分析

1.1 SpaceWire CODEC 結構

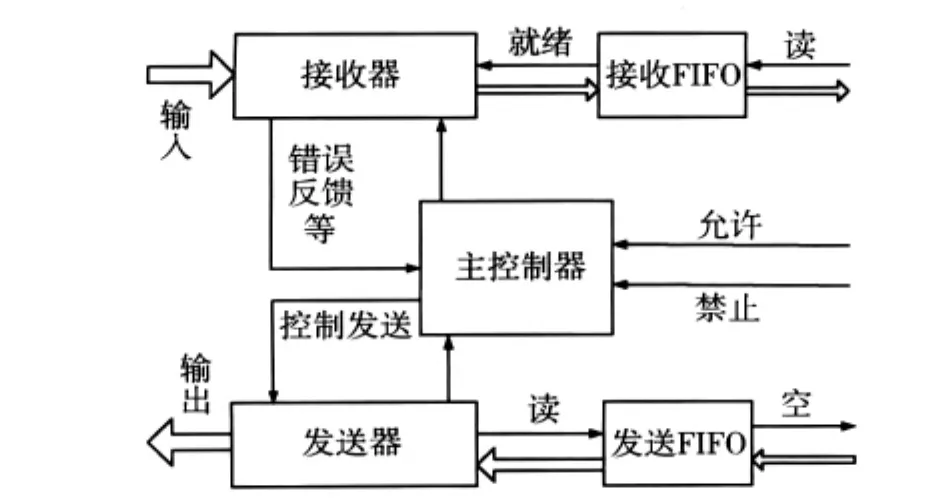

SpaceWire CODEC包括協議中的信號層(不包含其中LVDS接口部分)、字符層、交換層和數據包層.SpaceWire CODEC由發送先進先出數據緩存器(FIFO,first in first out memory)、接收 FIFO、發送器、接收器以及主控制器5部分組成.發送及接收FIFO主要用來實現主機和SpaceWire CODEC的數據交換;發送器則是按照主控制器的要求,對相應的字符進行編碼并發送;接收器則主要實現對數據進行解碼和錯誤檢測;主控制器主要用來控制數據傳輸,包括鏈路控制、錯誤恢復、控制發送器發送數據以及接收器接收數據等功能.SpaceWire CODEC結構簡圖如圖1所示.

圖1 SpaceWire CODEC結構簡圖Fig.1 Block diagram of SpaceWire CODEC

1.2 SpaceWire容錯性能分析

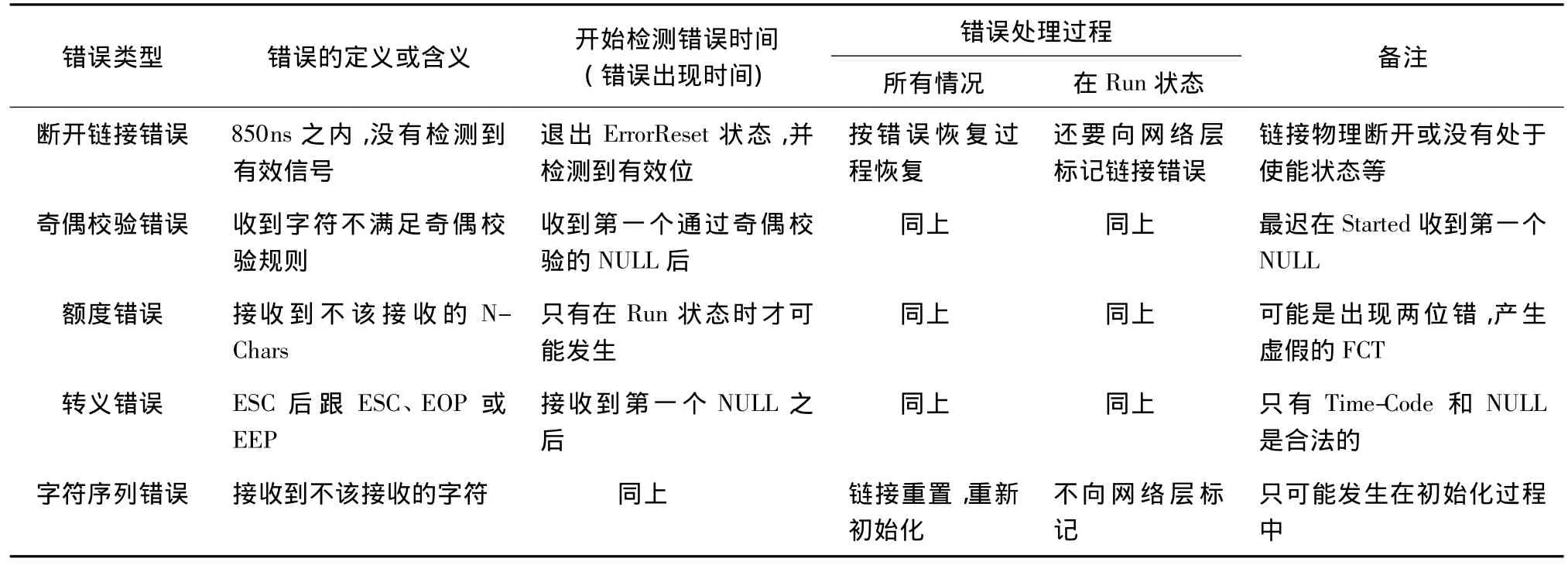

SpaceWire自身提供了一些容錯措施,包括:在信號層中采用DS(Data-Strobe)編碼,該編碼可以很好地消除時鐘偏移,減小或者補償數據偏移;在字符層增加奇偶校驗位(每10位數據至少有1位奇偶校驗位),通過信息冗余來提高數據傳輸的可靠性;在數據包層,通過正常數據包結束符(EOP,normal end of packet)和錯誤數據包結束符(EEP,error end of packet)來區分正確的數據包以及錯誤的數據包;在交換層能夠檢測到的錯誤以及這些錯誤的處理方法如表1所述,交換層是實現SpaceWire錯誤檢測和恢復的主要協議層;在網絡層中,采用自適應群組路由(GAR,group adaptive routing),其目的之一是實現冗余路由、冗余鏈接,當到達目標節點的某條鏈接出現故障時,可以通過網絡中的其他鏈接到達目標節點,從而提高網絡的容錯能力.

表1 中,ErrorReset、Started、Run 是SpaceWire主狀態機的三個狀態,Time-Code、FCT(flow control token)、ESC(Escape)、EEP、EOP、NULL 則 是SpaceWire中規定的字符,N-Chars(Normal-Characters)指EEP、EOP和數據字符.表1中的錯誤恢復過程是基于端到端的SpaceWire鏈接來實現的.具體的恢復過程以A、B兩個端點之間的鏈接為例:當A端主控制器的狀態寄存器跳轉到一個非法的狀態(如發生SEU,A端檢測到錯誤的情況類似)時,A端主控制器將控制A端發送器停止發送任何數據,鏈接B端的接收器在850ns內接收不到任何有效的數據,將產生一個斷開鏈接錯誤,并將此錯誤通知給B端的主控制器,B端主控制器在接收到斷開鏈接錯誤后,控制B端發送器停止發送任何數據,這將在A端造成一個鏈接斷開錯誤,至此,A、B兩端之間的鏈接完全斷開,并重新開始建立鏈接,如果建立鏈接條件不成立,那么A、B兩端將一直嘗試建立鏈接,直到A、B兩端非使能(停止建立鏈接)或建立鏈接的條件成立;如果建立鏈接條件成立,鏈接重新建立,恢復數據傳輸,A、B之間的鏈接完成一個錯誤恢復過程.B端檢測到錯誤的情況和A端類似.此外,當A、B之間的鏈接出現故障時,可以通過路由、冗余的鏈接找到從A到B進行數據傳輸的其他鏈接.

SpaceWire沒有規定SpaceWire CODEC內部的容錯能力,其發送/接收FIFO本身不具有任何錯誤檢測、恢復的能力;發送器對數據進行發送時,增加奇偶校驗位,提高數據傳輸的可靠性;接收器具有較強的檢錯能力,可以檢測到表1中的各種錯誤,將錯誤信息傳遞給主控制器.主控制器通過控制鏈接來實現錯誤恢復.

SpaceWire的容錯能力體現在基于端到端的鏈接,SpaceWire CODEC具有一定的錯誤檢測能力,但這不足以保證在惡劣的空間環境中實現可靠的數據傳輸,具體表現在以下幾個方面:

①SpaceWire CODEC僅在發送數據時增加奇偶校驗位,在發送/接收FIFO中,沒有任何保證數據可靠性的措施.FIFO作為SpaceWire CODEC和主機之間的緩沖區,用來存儲待發送/接收到的數據、命令、控制信息,是容易受SEU、SEFI影響的部分,不采取容錯措施有可能導致發送/接收到的數據、命令發生錯誤并造成嚴重的后果;

②SpaceWire CODEC的容錯策略側重在檢測到錯誤后,采用基于端到端的錯誤恢復機制實現錯誤恢復,而不是SpaceWire CODEC自身來糾正檢測到的錯誤,在空間環境中SpaceWire CODEC的實現載體如果受到空間輻射的影響,將影響系統的可靠性;

③SpaceWire基于端到端的錯誤恢復機制,并非能糾正檢測到的所有錯誤;當SpaceWire CODEC中的一些寄存器,如寄存器中的[Linkable]位(鏈接建立使能位)發生了翻轉,只能通過對寄存器中的[Linkable]位進行重新設置,否則鏈接將無法建立;

④SpaceWire CODEC這種基于鏈接的錯誤檢測、恢復方法需要占用網絡的時間資源和帶寬資源.以錯誤恢復時間為20μs、傳輸速率為100Mbit/s計算,那么在鏈接恢復的過程至少有2000bit的數據無法處理,這不僅會造成鏈接阻塞,影響數據的正常傳輸,對系統的實時性也將產生影響.

根據以上分析,為適應惡劣的空間環境,有必要對SpaceWire CODEC中的FIFO、狀態機、寄存器等容易受SEU、SEFI影響的部分進行容錯設計.

表1 交換層出錯類型以及處理方法Tab.1 Error types and their handling ways in exchange level

2 SpaceWire CODEC的容錯設計

2.1 FIFO的容錯設計

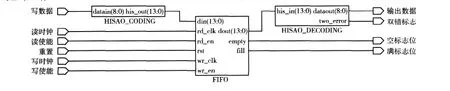

FIFO作為CODEC和主機之間的緩沖單元,需要存儲的數據包括8位數據和1位控制信息標志位.檢錯糾錯(EDAC,error detect and correct)是FIFO的有效容錯設計方法.

本文通過實現Hsiao[2-3]編碼,使FIFO具有糾一檢二的能力.與擴展Hamming編碼相比,Hsiao編碼具有以下優點:①編解碼速度快,校驗矩陣中每行“1”的個數相等,這說明用于產生每位校驗位的電路延時幾乎相等,不僅速度快,而且便于優化;②電路面積小,校驗矩陣中的“1”表示硬件電路中參與XOR運算的相關數據位,Hsiao編碼中所用到的XOR比擴展Hamming編碼的要少,這不僅能減小面積,同時能降低功耗;③Hsiao編碼4位錯誤的檢測概率高于擴展Hamming編碼.

Hsiao編碼最重要的是校驗矩陣即H矩陣的構造,H矩陣應滿足:

①每列中有奇數個“1”,無相同列;

②每行中“1”的個數盡可能相等;

③“1”的總個數盡可能少.

上述條件保證了編碼的最小距離是4,可實現糾一檢二,但是校驗矩陣卻不唯一.以本文中的FIFO為例,(14,9)分組碼的H矩陣有C(10,9)=10種選擇,不同的矩陣對電路的性能影響是不同的,目前尚無有效的選擇算法,本文選擇了表2所示的校驗矩陣.

當出現兩位數據錯誤時,具體的處理方法如下:將錯誤信號返回給更高層,同時將數據中的原有數據直接輸出.這樣的考慮是基于:①檢測到兩位錯誤,這兩位錯誤并非一定出現在有效數據位,也有可能在校驗位出錯,甚至出錯的兩位都在校驗位;②傳輸層、應用層如果也采取相應的措施,完全有可能糾正此錯誤;③可以由應用層根據數據的不同應用來決定如何處理.

表2 Hsiao碼校驗矩陣Tab.2 Check matrix of Hsiao coding

采用Hsiao編碼使FIFO具有糾一檢二的能力,實現EDAC后FIFO的結構如圖2所示.

2.2 主控制器狀態機容錯設計

SpaceWire主控制器狀態機(FSM,finite state machine)是SpaceWire CODEC電路中的重要組成部分,主要用來完成鏈接建立、鏈路維護、鏈路控制以及錯誤處理等,其容錯能力、可靠性直接影響到總線的正常工作.

SpaceWire主控制器狀態機包括ErrorReset、ErrorWait、Ready、Started、Connecting、Run 6 個狀態,除了在鏈接建立過程中要經過ErrorReset、ErrorWait、Ready、Started、Connecting這 5 個狀態之外,一旦鏈接建立,其狀態機的狀態將一直保持Run狀態,直到鏈接終止或者出現錯誤.

圖2 帶有檢錯糾錯功能的FIFO結構圖Fig.2 Block diagram of FIFO with EDAC

對正常運行的SpaceWire網絡來說,幾乎所有接口的主狀態機都運行在Run狀態.為保證數據的可靠傳輸,狀態機處在Run狀態時要采取更加有效的容錯設計方法,同時增強在其他狀態時的檢錯能力,借助SpaceWire自身的錯誤恢復能力實現錯誤恢復.本文對主控制器狀態機采用下列方案進行容錯設計:

①狀態機采用 One-Hot編碼[4],可有效地提高電路的速度和可靠性;

②One-Hot編碼正常狀態只有一個觸發器的狀態為1,其余態皆為0,根據這個特點,對當前狀態機寄存器增加奇偶判斷,來有效地檢測合法狀態到非法狀態之間的轉化;

③增加一個前態寄存器,在主狀態機的轉換關系中,任何狀態到達ErrorReset都是合法的;除了Error-Reset狀態之外,其他任何狀態只能由一個狀態轉換而來;在到達當前狀態時,首先判斷前一個狀態是否對應,以此來防止合法狀態之間的非法轉化(如ErrorWait跳轉到Started就是一個非法的轉化);

④設置rflag標志,在到達Run狀態時,對當前的狀態寄存器采取刷新的策略,保證狀態機在Run狀態時,有更高的可靠性.同時對rflag標志位進行刷新,防止錯誤的積累而導致rflag判斷出錯.

本文對主狀態機采用 One-Hot編碼、帶有EDAC功能的二進制編碼[5]以及本文所采用的方法進行對比(僅對主控制器進行綜合),如表3所示.

由表3可知,狀態機采用EDAC編碼,增加了額外的解碼電路、編碼電路,因而需要較多的邏輯資源,對頻率會產生影響;One-Hot編碼需要較多的觸發器資源,邏輯資源則相對較少;本文采用的方法資源開銷較小,并可以達到較高的頻率.

表3 主控制器狀態機3種不同設計方法對比Tab.3 Comparison of three different design methods for master controller FSM

2.3 寄存器的容錯設計

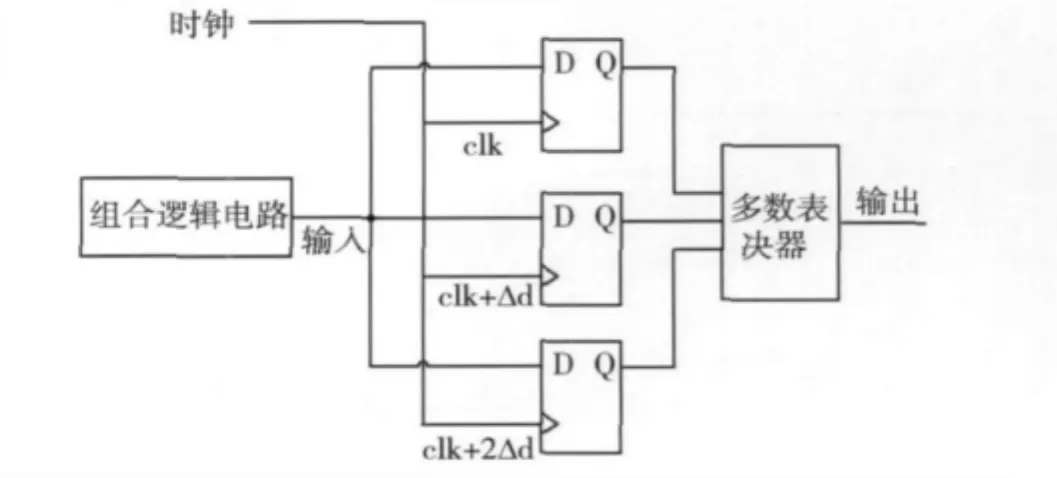

寄存器作為SpaceWire CODEC的重要組成單元,其中暫存著協議執行過程中的重要數據,它的可靠性至關重要.由于設計中的寄存器分布比較分散,不適合采用冗余編碼方案,因此本文對SpaceWire CODEC中所有寄存器采用空時三模冗余(ST-TMR,space-time triple modular redundancy)[6]設計.

圖3 空時三模冗余結構示意圖Fig.3 Block diagram of ST-TMR

采用ST-TMR不僅可以防止單一寄存器發生SEU而導致數據失效,同時由于ST-TMR采用了硬件冗余和時間冗余相結合的技術,寄存器前一級的組合邏輯上的單粒子瞬時干擾(SET,single event transient)也可以被濾除.ST-TMR能夠有效減輕組合邏輯的SET和時序邏輯的SEU.如圖3所示,STTMR容錯方法通過在組合邏輯的下一級時序邏輯上使用帶延遲的多級時鐘,可以在不同時刻采樣組合邏輯的輸出,利用該時間差,濾除組合邏輯有可能發生的SET.

實現ST-TMR首先是要生成帶有時延的時鐘.在FPGA中可以通過插入buffer來實現,本文采用xc4vlx200型FPGA中的BUFIO緩沖單元來實現,延時約為 380ps.實現兩級延時為 760ps.當采用100MHz的時鐘頻率時,這一延時為時鐘周期的7.6%,對時序的影響較小,當采用的時鐘頻率更高時,影響將加大.

3 驗證與測試

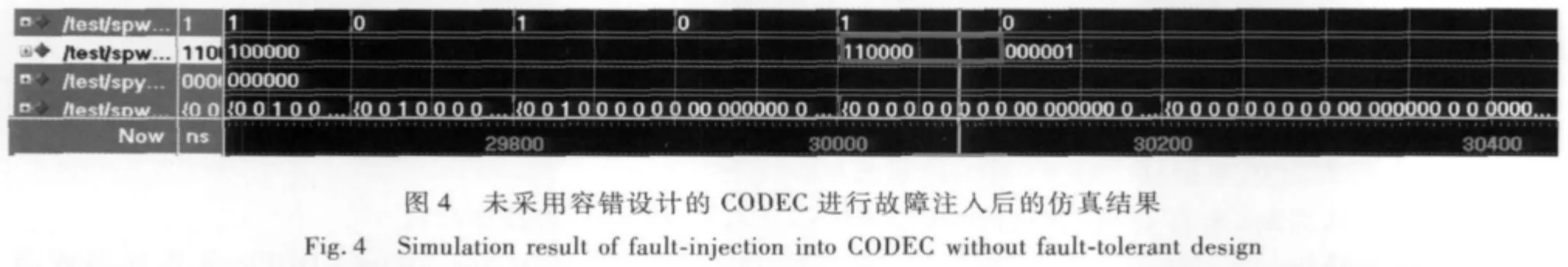

在Modelsim6.2g下,通過對寄存器、信號進行強制賦值來實現對SpaceWire CODEC中寄存器的故障注入;在TestBench中,通過一個故障注入的進程來實現對某些信號的強制賦值,在30001ns時,強制將狀態寄存器的狀態更改為一個非法的狀態“110000”,持續時間為100ns.分別對容錯設計前后的CODEC注入故障,可以看到在圖4中,由于注入故障,導致狀態寄存器直接回到 ErrorReset(“000001”)狀態,鏈接斷開;在圖5中注入同樣的故障,在故障結束后,狀態寄存器仍然在 Run(“100000”)狀態,鏈接并沒有受到故障的影響,仍然進行正常的數據傳輸.在對數據進行EDAC編碼后、寫入FIFO之前以及在從FIFO中讀出數據進行EDAC解碼之前,隨機的注入一位、兩位故障來實現對FIFO的故障注入.故障注入的結果表明,容錯設計能有效地屏蔽注入的故障.

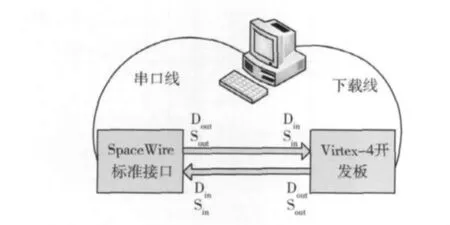

采用容錯設計的SpaceWire CODEC在Vitrex-4系列開發板上實現,其物理測試鏈接示意圖如圖6所示.通過和SpaceWire標準接口建立鏈接,能夠正確地發送、接收各種字符以及斷開鏈接后恢復鏈接.驗證結果表明采用容錯設計后的SpaceWire CODEC功能正確.

圖6 SpaceWire物理測試鏈接示意圖Fig.6 Interconnection of SpaceWire test

4 結論

容錯設計是提高產品可靠性的有效途徑,產品設計過程中需要在各個環節采取容錯措施.本文分析了SpaceWire協議的容錯性能,并對 SpaceWire CODEC的容錯設計方法及驗證情況進行了介紹.通過對SpaceWire CODEC中的FIFO、狀態機和寄存器進行相應的容錯設計,從整體上提高了SpaceWire CODEC的容錯能力.仿真結果表明容錯設計有效,測試結果表明容錯設計的SpaceWire CODEC功能正確.

[1 ] Steve P.Space engineering spacewire-links,nodes,routers and networks[S].ESA-ESTEC ,2008

[2] Hsiao M Y.A class of optimal minimum odd-weight-column SEC-DED codes[J].IBM Journal of R & D,1970,14:395-401

[3] Ghosh S,Basu S,Touba N A.Reducing power consumption in memory ECC checkers[C].IEEE International Test Conference,Charlotte,Oct 26-28,2004

[4] Kumar N.Automated FSM error correction for single event upsets[C].Military and Aerospace Programmable Logic Devices International Conference,Washington D.C,2004

[5] Shailesh N.A comparison of fault-tolerant state machine architecture for space-borne electronics[J].IEEE Transactions on Reliability,1996,45(1):109-113

[6] Chen W,Gong R.Two new space-time triple modular redundancy techniques for improving fault tolerance of computer systems[C].The 6thIEEE International Conference on Computer and Information Technology,Washington D C,Sep.2006