直接頻率合成器雙路上變頻信號產生方法

蘇 宏,全 閔,于 宇,趙耀軍

(1.機電動態控制重點實驗室,陜西 西安 710065;2.西安機電信息技術研究所,陜西 西安 710065)

0 引言

在科學試驗或工程中,可能會需要一個可以連續調整頻率的信號源。例如在步進電機控制系統中,步進電機的轉速范圍為0.01r/s至幾十轉每秒,那么就需要信號源的頻率從幾赫茲到10kHz線性連續變化[1]。同樣在雷達成像中需要大的時寬、帶寬積的線性調頻信號以取得高分辨圖像。如果采用模擬鎖相環方法[2]是非常困難的,采用直接數字頻率合成器(Direct Digital Frequency Synthesis簡稱DDS)技術[3],就可以很容易地實現上述要求。目前常用DDS芯片抗輻照特性不強,且產生同等帶寬線性調頻信號,相比直接數字頻率合成法,采樣時鐘需要提高到2倍,為保證高頻率采樣時鐘的穩定性就需要利用放大器或變壓器將單端時鐘轉換為差分時鐘,提高了設計復雜性。同樣,利用FPGA控制內置ROM讀表法,由于FPGA的內置ROM存貯量有限,也產生不了時寬長線性調頻信號。利用FPGA控制外掛Flash讀表法,需要在板子上外掛Flash,如果線性調頻信號的分辨率高,時寬長,需要幾塊Flash,使板子結構也復雜化,無形增加了風險。據此,提出基于FPGA的DDS上變頻I、Q雙路基帶線性調頻信號產生方法以簡化硬件設計。

1 直接數字頻率合成器基本原理

直接數字頻率合成器原理(Direct Digital Synthesizer)是從相位概念出發直接合成所需波形的一種頻率合成技術[4],它由相位累加器、波形存儲器(sin表)、DA 轉換器及低通濾波器等組成[5-6]。下面對線性調頻信號產生的過程作簡單說明。

參數:設線性調頻信號的中心頻率為Fcenter,起始頻率為Fbegin,截止頻率為Fend,帶寬B為ΔF,時寬為T,采樣頻率為Fcollection,初相位為0。

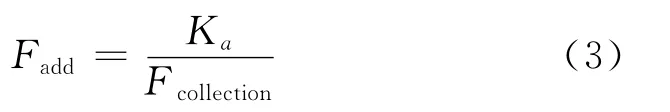

1)調頻率Ka表示為:

2)DA轉換次數M表示為:

則每個轉換次數的增加頻率表示為:

3)設制定的sin表的地址數為1 024,則相位分辨率為2π/1 024,且該sin表的幅值為1~1 024,即20~210,則它的幅度分辨率為10位。該原理的相位變化表達式為:

通過式(4),可以計算出M 次轉換次數對應頻率點的相位值,再由相位值在制定的sin表中查找對應的幅度值,從而得到所需的線性調頻信號。

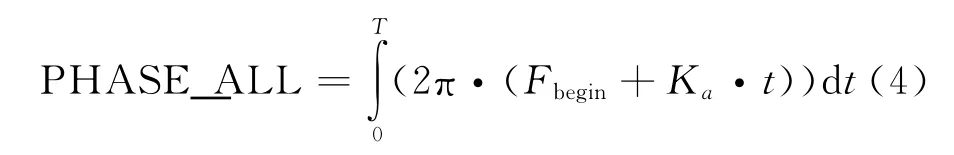

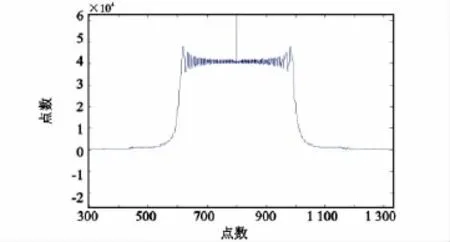

圖1是以Altera公司的EP1k30QI208-2FPGA為硬件基礎根據數字頻率合成器原理設計的單板產生的頻率為-10~10MHz,時寬為40μs的基帶線性調頻信號,此圖為在示波器中以Matlab信號格式采集。

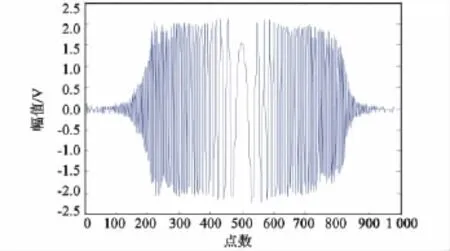

經過頻譜儀分析,頻譜平坦度達到0.5dBm,信號和噪聲功率差大概48dB。圖2是運用Matlab編程分析得到該信號的頻譜圖,由于產生的是單路實信號,所以頻譜為對稱不平整狀。

圖1 單路-10~10MHz線性調頻信號時域波形Fig.1 Single channel-10~10MHz liner FM time domain waveform

圖2 單路-10~10MHz線性調頻信號頻譜波形Fig.2 Single channel-10~10MHz liner FM frequency spectrum waveform

2 直接數字頻率合成器I、Q雙路上變頻

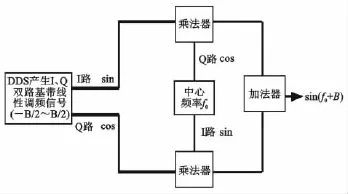

針對單路實信號,頻譜為對稱不平整,可以設計I、Q兩路線性調頻信號合成后的頻譜為光滑對稱平整狀,如圖3所示。

直接產生中頻線性調頻信號對采樣時鐘的要求非常高,例如要產生以100MHz為中心頻率、帶寬為60MHz的線性調頻信號,那么至少要提供260 MHz的采樣時鐘。如果直接利用數字頻率合成I、Q雙路頻率為-30~30MHz共60MHz基帶線性調頻信號,上變頻為100MHz為中心頻率、帶寬為60MHz的線性調頻信號,只要提供60MHz以上的采樣時鐘即可,時鐘要求比常規方法少了2倍的中心頻率大小。此主要原理即為三角公式的合差化積原理,表達式為:

圖3 I、Q雙路-10~10MHz線性調頻信號頻譜波形Fig.3 I/Q twin-channel-10~10MHz liner FM frequency spectrum waveform

設B為-30~30MHz共60MHz基帶線性調頻信號,f0為100MHz中頻信號,經過流程圖4,可得到100MHz為中心頻率、帶寬為60MHz的線性調頻信號,再經混頻器上到射頻,即完成發射信號的調制。此即為簡化硬件設計,基于FPGA的DDS上變頻I、Q雙路基帶線性調頻信號產生的方法。

圖4 直接數字頻率合成器I、Q雙路上變頻流程圖Fig.4 DDS I/Q twin-channel up-converted flow chat

通過直接利用數字頻率合成I、Q雙路頻率基帶線性調頻信號上變頻為中頻線性調頻信號,只要提供基帶最高頻率2倍以上的采樣時鐘即可,時鐘要求比常規方法少了,同時由于采樣頻率的減少使得硬件設計大大簡化,縮短了設計和生產周期,增強系統的穩定。

3 仿真驗證

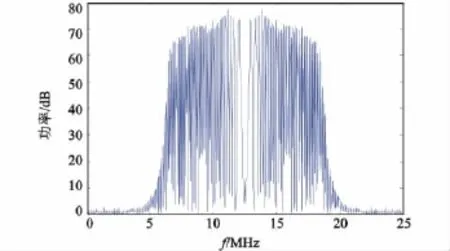

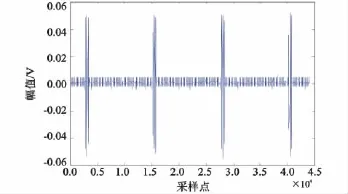

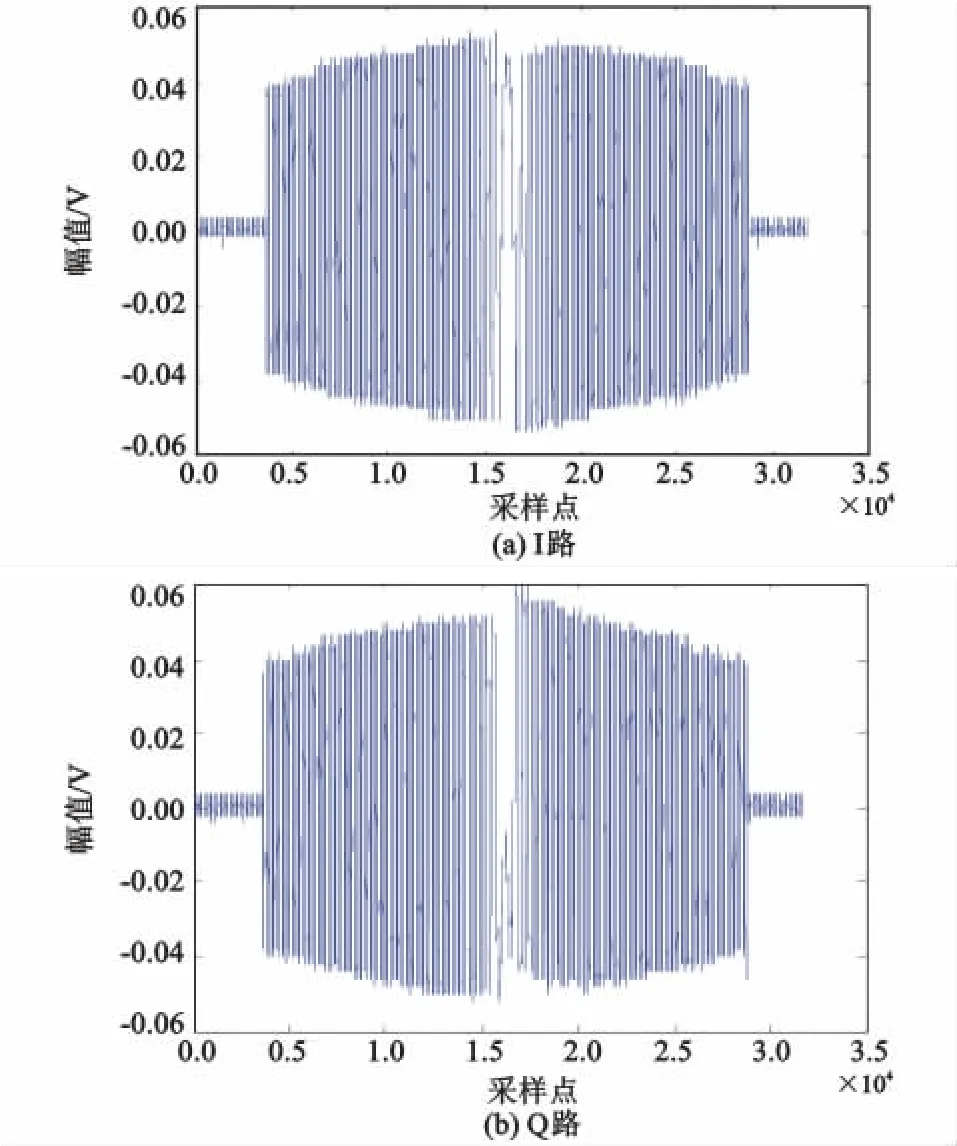

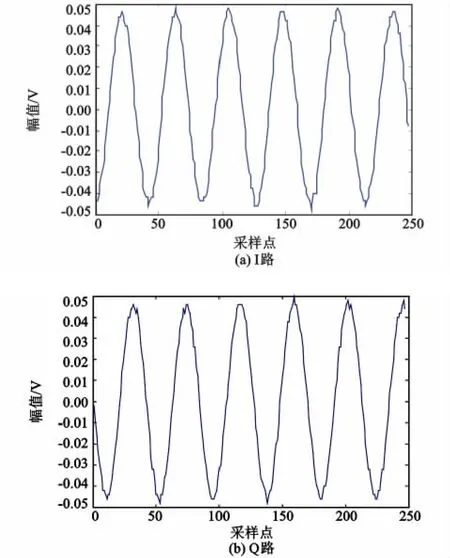

下面對利用FPGA產生的I、Q雙路基帶線性調頻信號從時域和頻域進行仿真分析。要實現流程圖4,好的信號源是關鍵。如圖5,根據DDS原理設計單板,并產生I、Q雙路-30~30MHz帶寬為60 MHz的基帶線性調頻信號,重復頻率為1kHz,采樣時鐘為80MHz,示波器采樣頻率為625MHz。圖6為產生I、Q雙路的采集Matlab數據時域波形,時寬為40μs。

圖5 I路重復周期為1ms的Matlab時域波形Fig.5 I channel time domain wave of 1ms repeating cycle wave

圖6 I、Q雙路的Matlab時域波形Fig.6 I/Q twin-channel Matlab time domain waveform

要使流程圖4順利實現,I、Q雙路的相位一致性要好,觀察一下時域波形,看I、Q雙路的幅值是否相差1/4或3/4個周期,即相位是否相差90°的奇數倍。

1)將圖6中的Matlab時域波形放大,對應同一段時間段,如圖7,I、Q雙路同一時段的放大Matlab時域波形,仔細觀察,發現在I路幅值為-0.05時,Q路為0。I路幅值為0時,Q路為-0.05。即差了3/4周期。

圖7 I、Q雙路同一時段的放大Matlab時域波形Fig.7 I/Q twin-channel magnified Matlab time domain waveform in the same period of time

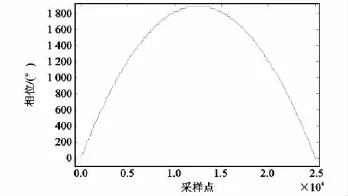

2)既然產生的是I、Q雙路-30~30MHz的基帶線性調頻信號,那么理論上將I、Q合成為復信號,它的相位曲線為標準的拋物線。將I、Q雙路采集的Matlab數據合成為復信號,利用Matlab得到相位曲線如圖8,近似標準的拋物線。

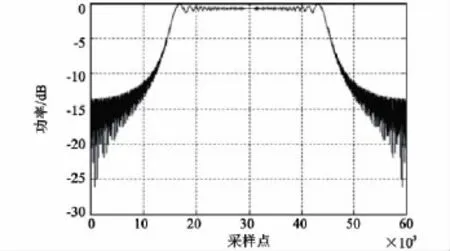

3)將產生的I、Q雙路信號合成為復信號后,作FFT變換,就可得到-30~30MHz的基帶線性調頻信號的頻譜,如圖9。近似理想的線性調頻信號頻譜,完全可以達到實際應用的要求。

仿真結果表明:利用FPGA產生I、Q雙路基帶線性調頻信號的結果達到實用工程化要求。可在基帶范圍內產生大頻帶I、Q正交基帶線性調頻信號,通過正交調制產生寬帶中高頻信號,避免了中頻線性調頻信號由于時鐘限制,只能產生小頻帶基帶線性調頻信號,再通過倍頻器放大頻帶所帶來的噪聲影響和波形變形的問題。

圖8 I、Q雙路合成為復信號的相位曲線Fig.8 Phase curve of I/Q twin-channel synthesized complex signal

圖9 I、Q雙路合成為復信號的幅頻特性曲線Fig.9 Amplitude-frequency Curve of I/Q twin-channel synthesized complex signal

4 結論

本文提出了基于FPGA的DDS上變頻I、Q雙路基帶線性調頻信號產生方法。根據DDS原理產生I、Q雙路基帶線性調頻信號,利用乘法器分別與要達到的變頻信號的中心頻率相乘并通過加法器求和,根據合差化積原理,產生所需的線性調頻信號,再經混頻器上到射頻,實現發射信號的調制。仿真結果表明:該方法產生的調頻信號從時域和頻域均滿足工程化要求,有效地簡化了調頻信號源硬件設計。由于芯片等級不高,信號指標有待提高,可通過更高級芯片組合(FPGA,DA)產生性能更好的各種信號。

[1]張少輝.基于DDS技術構建信號發生器[J].中國科技信息,2007(1):96-98.ZHANG Shaohui.The sinewave Generator based on direct digital synthesizer[J].China Science and Technology Information,2007(1):96-98.

[2]吳士云,葉建芳,劉敏.基于FPGA的直接數字頻率合成器的設計與仿真[J].中國電子商情:通信市場,2009(2):109-113.WU Shiyun,YE Jianfang,LIU Min.Design and simulation of direct digital frequency synthesizer based on FPGA[J].Telecom Market,2009(2):109-113.

[3]蔣一,魏駿,李昊.基于DDS的寬帶雷達信號產生技術研究[J].國外電子測量技術,2007(2):47-49.JIANG Yi,WEI Jun,LI Hao.Study on the generation of wide band radar signal based on DDS[J].Foreign Electronic Measurement Technology,2007(2):47-49.

[4]盧一喆,蒙美海,張峰,等.基于工具軟件的直接數字頻率合成器設計方法[J].探測與控制學報,2011,33(6):42-45.LU Yizhe,MENG Meihai,ZHANG Feng,et al.FPGA DDS Design Based on DSP Builder[J].Journal of Detection & Control,2011,33(6):42-45.

[5]楊秀增.基于FPGA和DDS的信號源設計[J].電子設計工程,2009(11):13-14,17.YANG Xiuzeng.Design of a signal generator based on FPGA and DDS[J].Electronic Design Engineering,2009(11):13-14,17.

[6]李勇,艾竹君,劉巧云,等.基于FPGA的DDS設計方法[J].低溫與超導,2007(6):88-91.LI Yong,AI Zhujun,LIU Qiaoyun,et al.A design for DDS based on FPGA[J].Cryogenics and Superconductivity,2007(6):88-91.