單片機系統中的干擾及其處理措施

達州職業技術學院 岳曉禮

1.引言

單片機作為電子技術工作人員手中的一種可編程的“智能”元件,已經在工業自動化、智能化儀表、生產過程自動化控制等領域得到了廣泛深入的運用。但是由于單片機系統的工作現場非常復雜,存在來自系統內部與外部的各種電氣干擾,除此以外還受到系統結構、制造工藝、元器件的選擇與安裝的影響,這些都是單片機系統的干擾因素,對系統的可靠性和安全性構成了極大的威脅。單片機系統必須長期穩定、可靠的運行,否則將影響產品質量和產量,嚴重時會使系統失靈,甚至造成事故和巨大的經濟損失。這就要求我們在設計單片機系統時應結合現場情況,在硬件設計、軟件設計以及線路板設計等方面來采取相應的抗干擾措施。

2.干擾的種類和主要來源

工業環境中干擾是以脈沖的形式竄入單片機系統的,是通過三種途徑影響系統的正常工作的,即空間干擾,供電系統干擾和過程通道干擾。空間干擾主要發生在高電壓、大電流和高頻電磁場附近,通過靜電感應、電磁感應等方式竄入系統;供電系統干擾主要由電源的噪聲干擾引起;過程通道干擾主要是干擾通過前向通道與后向通道進入系統內部。另外接地裝置的不可靠,也是產生干擾的重要原因;各種類型的傳感器,輸入和輸出線路的絕緣損壞都有可能引入系統干擾。

干擾如果進入單片機系統,將會對系統產生如:數據采集誤差的加大,程序運行失常,系統被控對象誤操作,被控對象狀態不穩定,定時不準,數據發生變化等后果。因此必須對單片機系統采取抗干擾措施。

3.對電源干擾采取的措施

對于單片機系統供電系統的干擾最為嚴重,絕大多數單片機系統的直流電源都是由市電經過整流、穩壓和濾波后得到的,而電網電壓受到電氣設備的通斷、跳閘等影響,都會造成電源干擾。

3.1 提高供電系統的供電質量

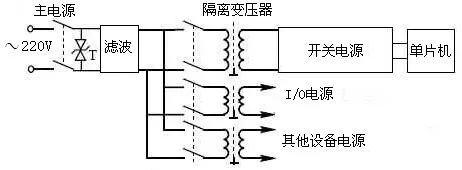

提高供電系統的供電質量是非常重要的一步,可以采用圖一所示的供電結構。電源分別給系統各個功能模塊供電,從而減少了公共電源與公共阻抗之間的相互耦合,從而提高了電源的抗干擾性。

圖一 單片機供電結構

3.2 利用壓敏電阻抑制尖峰、浪涌

利用壓敏電阻兩端的電壓超過其限定值時,電流會迅速增大,呈短路狀態的特點,用它吸收瞬間的尖峰和浪涌電壓。把壓敏電阻并聯在電源變壓器的初極與次級,加入壓敏電阻后,電源干擾造成單片機程序失控的可能性將大大減小。壓敏電壓的計算公式為:VIMA=1.56×32×V~(V~:交流電壓有效值)。

3.3 利用濾波器抑制高頻干擾

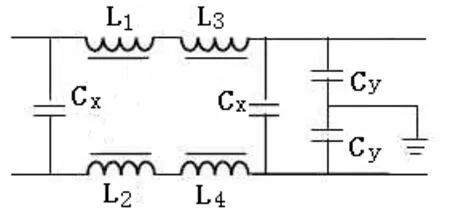

市電中含有多種高次諧波,它們很容易由電源進入單片機系統內部,這些干擾以“共模”或“差模”方式存在。圖二為電源EMI濾波器電路,它是由參數元件構成的無源低通網絡,L1和L2是繞在同一磁環上的兩只獨立線圈,繞匝數相同、繞向相反,稱為共模線圈,L3和L4是獨立的差模線圈。由L1和Cy,L2和Cy就分別構成兩對獨立端口間的低通濾波器,用來抑制電源線上的共模EMI信號;由(L1-L2)形成差模電感,它與L3、L4形成的獨立差模線圈與Cx電容器又組成一只低通濾波器,用來抑制電源線上的差模EMI信號。此外單片機控制系統還需要有完備的電源保護電路,其具有在電源啟停、瞬時短路、瞬間降壓時產生復位信號,當電源電壓恢復正常后,復位信號會自動解除。

圖二 EMI濾波器電路

4.印制電路板采用抗干擾設計

印制電路板(PCB)是電路元件和器件的支撐件,它提供單片機系統中的電路元件和器件之間的電氣連接,是系統中元器件、信號、電源線的高密度集合體,印制電路板設計的好壞對抗干擾能力影響很大,因此印制電路板應符合抗干擾設計的要求。主要有:

①采用接地抑制干擾的方法。低頻電路的地線盡量用單點并聯接地,高頻電路盡量用多點串聯接地。應加粗接地線條,使它能通過3倍于印刷電路板上的允許電流,同時使電源線、地線的走向與數據傳遞的方向一致,有助于增強抗噪聲能力。盡量使用45°折線而不使用90°折線,用以減少高頻信號對外的發射與耦合,減少互感振蕩。電源線與地線應盡量靠近走線從而減少所包圍的環路面積,因而可以減少外界磁場對環路切割而產生的電場干擾,同時也可以減少環路對外電磁輻射。

②對于單片機系統中的CPU、RAM、ROM等主芯片以及VCC、GND之間接電解電容和瓷片電容。石英晶體振蕩器的外殼接地而不要走信號線,并且要適當加大接地面積。時鐘線要盡量的短,并用地線將時鐘區圈起來,使周圍電場盡可能地減小。

③對于獨立系統結構,應減少接插件與連線;輸入輸出驅動器件、功率放大器件應盡量的靠近線路板邊的引出接插件。集成塊與插座接觸要可靠,使用雙簧插座,最好集成塊直接焊在印制板上,要防止器件接觸不良。信號的輸入、輸出端盡量使用光電隔離,這樣既可以防止外圍器件動作時產生的回流沖擊系統,又可以使輸入端的干擾信號沒有足夠的功率去干擾發光二極管的正常工作。

④在印刷電路板的各個關鍵部位配置去耦電容。原則上每個集成電路芯片都應安置一個0.01μF的瓷片電容排除射頻耦合干擾,電容引線不要太長,應緊靠芯片的電源線和地線。如果印刷電路空間狹小時,可以每4~10個芯片安置一個1~10μF限噪聲鉭電容。線路板布局時,應盡量使單片機的振蕩晶體放在單片機兩引腳近端。

5.采用軟件抗干擾措施

當單片機系統的CPU部位受到干擾信號的作用時,將使系統失控。典型的故障是破壞程序計數器PC的狀態值,進而導致程序在地址空間內"亂飛",或者陷入死循環。對這種情況的主要有指令冗余技術、軟件陷阱技術、睡眠抗干擾技術、“看門狗”技術。

5.1 在程序中插入空操作指令(指令冗余)

指令是由操作碼和操作數組成,操作碼指明CPU要完成怎樣的操作,而操作數是操作碼的對象。在程序執行過程中,CPU受到干擾后可能會將一些操作數當作指令碼來執行,引起程序混亂,但只要PC指針落在單字節指令上時程序就可納入正軌。因而在軟件設計時,應多采用單字節指令,并在一些關鍵地方插入NOP指令(如在雙字節、三字節指令后面插入2條NOP指令),另外在一些對程序流向起決定作用的指令之前也插入兩條NOP指令(如JNC,JB,JNB,JBC,RETI,RET,JC,ACALL,LCALL,SJMP,AJMP,LJMP,JZ,JNZ,DJNZ,CJNE)以保證彈飛的程序迅速納入程序軌道,或將有效的單字節指令重寫,這就是指令冗余技術。

5.2 采用軟件陷阱

當CPU受干擾,造成程序彈飛到非程序區是,指令冗余技術無能為力,可在非程序區采取攔截措施,使程序進人陷阱,強迫程序進入一個指定的地址去執行如下的指令:

NOP

NOP

LJMP ERR

此程序是專門對程序出錯進行處理(其中ERR為指定地址)的。軟件陷阱主要安排在未使用的中斷區、未使用的EPROM空間及非EPROM空間、程序運行區及中斷服務程序區。

①在未使用的中斷區,可以按照如下的方式寫中斷服務程序:

NOP

NOP

POP D1;將原來的錯誤斷點彈出

POP D2;將原來的錯誤斷點彈出

PUSH 00H

PUSH 00H;將斷點地址重寫為0000H

RETI

②在未使用的EPROM區,可在未用的區域里填充上020000數據,這樣當程序飛入其中時就會很快的走入正軌,這條指令就是“LJMP 0000H”的機器碼。

③在非EPROM空間,當CPU讀程序存儲器的時候,會產生一個PSEN信號,可利用這個信號,再加上一個非EPROM區的地址譯碼信號,構成一個選通信號來起動一個空閑的中斷,再用軟件陷井的方法從中斷程序中把程序導入正軌。

5.3 采用睡眠抗干擾

某些單片機具有睡眠狀態,在睡眠狀態下只有定時/計數系統、中斷系統處在工作狀態,此時CPU對系統三總線上出現的干擾不會作出反應,從而降低系統對干擾的敏感度。因此可以讓CPU在非正常工作的時候休眠,必要時由中斷系統喚醒它,工作完后再進入休眠狀態。這種安排,CPU可以在60%以上的時間處于睡眠狀態,從而使CPU受到隨機干擾的威脅降低,與此同時也降低了CPU的功耗。

5.4 “看門狗”技術

當程序飛到一個臨時構成的死循環或PC指針落到程序存儲器芯片地址之外時,冗余指令和軟件陷阱對此毫無辦法,系統將完全癱瘓。在這種情況下,只有復位。因此“看門狗”技術,就是一個能發出“復位”信號的計數器或定時器電路。“看門狗”技術可已由硬件實現,也可已由軟件實現。在單片機系統中,嚴重的干擾有時會破壞中斷方式控制字,關閉中斷,此時系統無法定時“喂狗”,硬件看門狗電路失效,但是軟件“看門狗”可有效地解決這類問題。實際應用中,可以采用環形中斷監視系統(如:用定時器T0監視定時器T1,用定時器T1監視主程序,主程序監視定時器T0),采用這種環形結構的軟件“看門狗”具有良好的抗干擾性能,有效的提高了系統的可靠性。對于需經常使用T1定時器進行串口通訊的測控系統,則定時器T1不能進行中斷,可改由串口中斷進行監控。

6.結束語

抗干擾是單片機系統設計中不可缺少的內容。硬件抗干擾是主動的,軟件抗干擾是被動的。由于干擾環境不同,在設計系統時應根據具體情況,選用針對性的抗干擾措施。

[1]王豐,欒學德.單片機應用技術[M].北京:北京航天航空大學出版社,2007.

[2]何立民.MCS-51系列單片機應用系統設計系統配置與接口技術[M].北京:北京航空航天大學出版社,1990.

[3]馬洪連.嵌入式系統設計教程[M].北京:電子工業出版社,2006.

[4]李朝青.單片機原理及其接口技術[M].北京:北京航空航天大學出版社,2005.

[5]趙新民.智能儀器設計基礎[M].哈爾濱:哈爾濱工業大學出版社,1999.

[6]侯大年.數字電子技術[M].北京:電子工業出版社,2000.