基于模塊局部可重構FIR濾波器設計

黃鳳英,王 俊,錢 慧

(1.福州大學 物理與信息工程學院,福建 福州350002;2.福州大學 電氣工程與自動化學院,福建 福州350002;3.福建省集成電路設計中心,福建 福州350002)

FIR數字濾波器具有在設計任意幅頻特性,同時能夠保證嚴格的線性相位特性,具有穩定性強、精度高、速度快等特點[1],在雷達、通信、音視頻、圖像、航空航天等領域有著廣泛應用。傳統的FIR濾波器的特性一般不能在線改變。但對未知時變環境下的信號進行處理時,濾波器的性能必須隨著實際條件變化而變化[2]。因此,設計一種能在保證系統正常運行的前提下,實時更改濾波器系數的FIR濾波器在研究、工業生產領域得到了廣泛的關注。

FPGA是一種典型的動態可重構器件,具有“在系統”重新配置電路功能的獨特性能,同時還具有在系統動態重構電路邏輯的能力,對提高電子信息系統的實時處理能力、可靠性、降低硬件系統的規模和功耗具有重大的理論和實際意義[3]。

本文利用Xilinx Virtex-4 FPGA可以重構配置特性,結合濾波器結構的特點,設計了一個基于模塊局部可重構的FIR濾波器,并結合MATLAB工具軟件,對可重構設計的性能進行了測試。實驗結果表明,相對于傳統設計方法,本文設計的可重構FIR濾波器具有快速、靈活、硬件資源消耗少等優勢。

1 FIR濾波器原理概述及設計方法

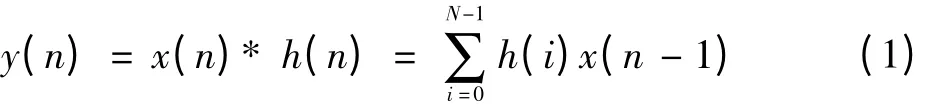

FIR濾波器的數學表達式為

式(1)中,N是FIR濾波器的抽頭數,x(n)表示第n時刻的輸入樣本,h(i)表示濾波器的第i級抽頭系數。FIR的傳遞函數H(Z)是通過對h(i)進行Z變換得到,其形式如式(2)所示

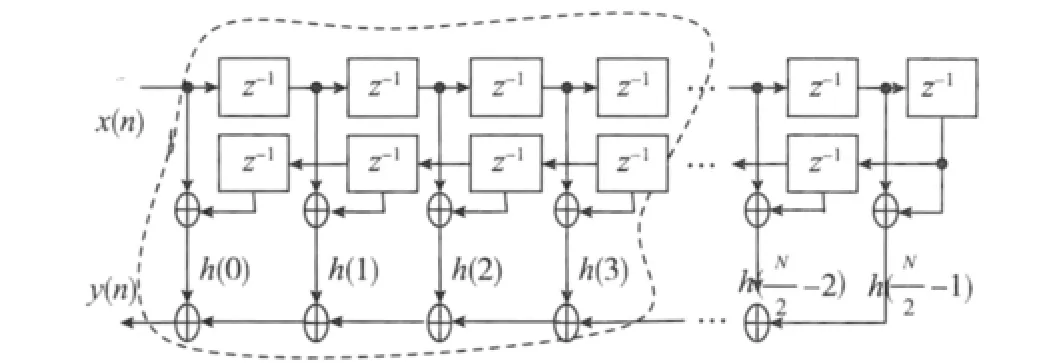

根據式(1)、(2),可畫出FIR濾波器的一般結構如圖1所示。

圖1 FIR濾波器的一般網絡結構

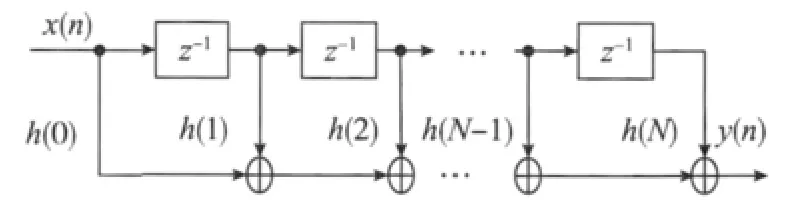

由圖1可知,FIR濾波輸出結果y(n)實質上是由一個輸入信號x(n)經過逐級延遲,且在各級延遲輸出進行加權累加得到。濾波器最主要的工作過程是進行乘累加運算,一個N階的FIR濾波器完成一次濾波需要進行(N-1)次加法運算和N次乘法運算。但FIR數字濾波器具有線性相位特性及對稱特性,即

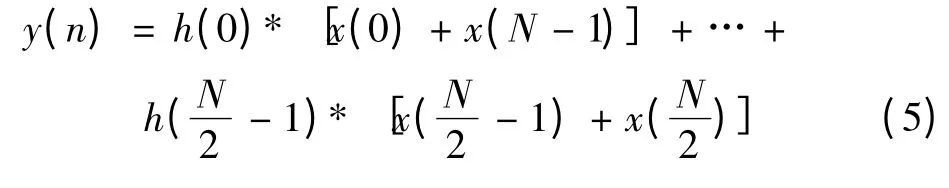

從而容易得到偶對稱的FIR濾波器的輸入輸出關系,如式(5)所示

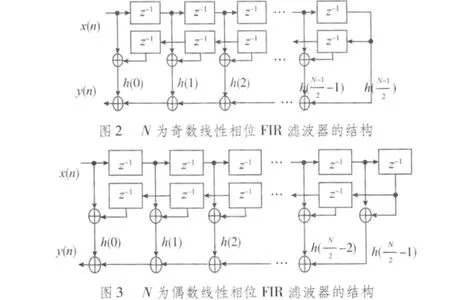

相對于直接型結構,在實現濾波器硬件電路上,乘累加次數得到減半,資源消耗更少,且濾波的時鐘周期減半,從而大大提高了處理速度[4]。圖2和圖3分別顯示了N取奇數和N取偶數的線性相位FIR濾波器結構。

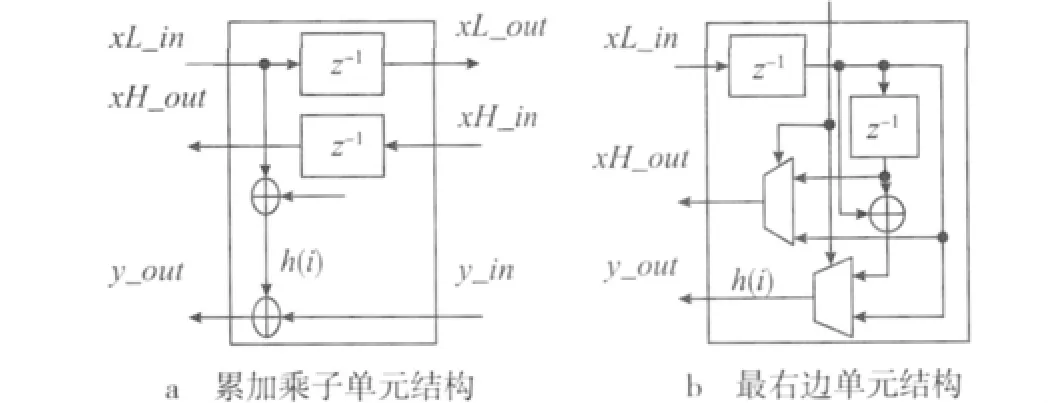

從圖2、圖3可知,FIR數字濾波器可以看成由多個累加乘子單元和一個最右面的單元結構組成,如圖4a,4b所示,根據階數為偶數或者奇數(信號線even為1或者0)決定最右單元結構。從結構上看,FIR濾波器容易通過多個濾波器直接級連就能夠擴展濾波器的階數,因此在FPGA上采用基于模塊局部重構技術來重構FIR濾波器變得簡單、靈活,且能夠充分利用資源。

圖4 單元結構圖

2 基于模塊局部重構設計

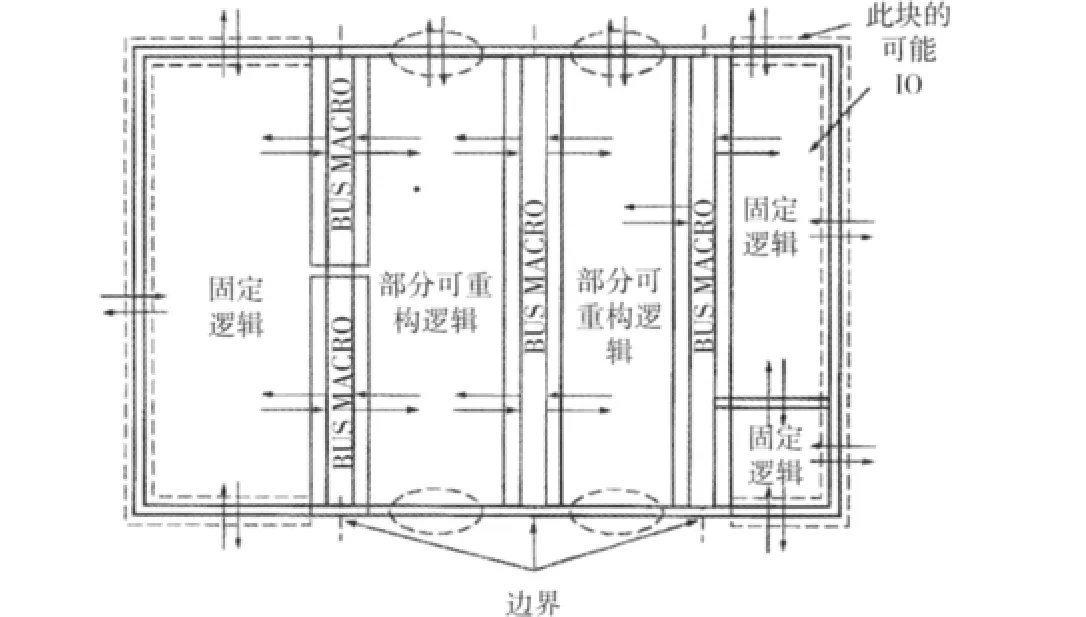

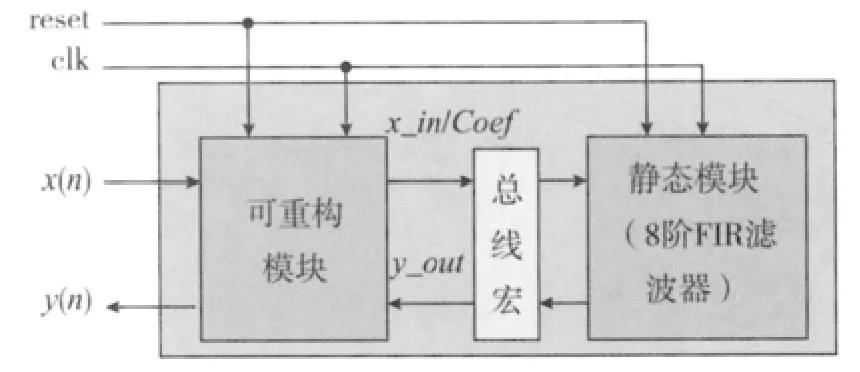

如圖5所示,基于模塊的可重構設計的一個重要步驟是將整個電路功能劃分成功能可變的重構模塊(可重構邏輯)和功能不變的靜態模塊(固定邏輯)。其中,可重構區域可以在器件的其他部分還在運行的情況下進行重構。

圖5 兩個模塊的設計布局圖

基于模塊局部重構的輸入、輸出以及穿過可重構模塊邊界的布線資源是預先固定的,這就需要一種特殊的總線宏(BUS MACRO)在局部重構模塊和靜態模塊之間充當一個固定的布線橋,總線宏在功能重構的時候仍保持不變,從而能夠保證兩個模塊之間能正確的通信[5]。

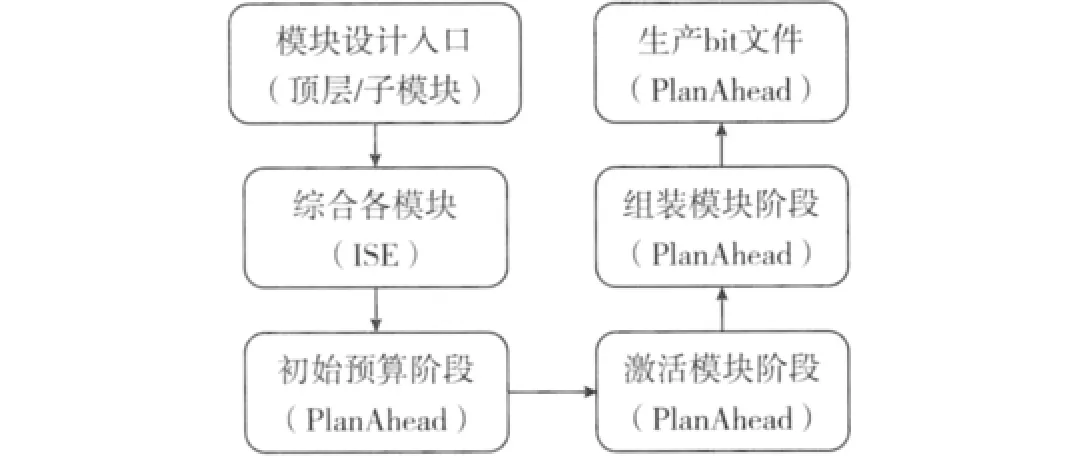

實際設計中,如圖6所示,每個模塊從硬件描述語言(verilog)設計開始,經過獨立綜合、布局、實現等操作,并生成比特流文件[6]。

圖6 局部重構設計流程圖

3 可重構FIR濾波器設計

本文設計的可重構FIR濾波器階數可從8階到16階進行的轉變,其中靜態模塊由3個累加乘子單元結構和最右邊單元結構組成;可重構模塊由多個累加乘子單元結構模塊和濾波器系數輸入的控制模塊組成。且在靜態模塊和動態可重構模塊之間插入總線宏,設計框圖如圖7所示。

圖7 可重構FIR濾波器的設計框架

從前面濾波器的結構圖中可以看出16階的FIR濾波器和8階的濾波器硬件結構基本相同,為了構成16階濾波器,可在原有的8階濾波器結構上加載4個累加乘單元模塊,如圖8中的虛線區域所示。在實現重構過程中,只需下載重構模塊的配置信息,而不需要重新配置整個芯片,就能將原有的濾波器構成16階的FIR濾波器,而原本在FPGA上的8階FIR濾波器不受任何影響,如此可大大減少芯片的重配置時間。

圖8 虛線區為局部重構部分可動插入或刪除

4 實現

該部分描述了一個重構的FIR濾波器在Xilinx Virtex-4 FPGA上的實現過程。

4.1 硬件描述語言編碼及綜合

局部重構是一種分層設計方法,在編碼過程中必須嚴格遵守。首先,用ISE軟件設計3種HDL文件,分別是頂層HDL設計,靜態模塊HDL設計和局部重構模塊HDL設計,然后獨立綜合各文件。

頂層模塊不包含任何邏輯,只有輸入輸出實例、靜態和可重構模塊實例、信號聲明,以及定義了各個子模塊的連線,區域及總線宏的分配。靜態模塊和可重構模塊主要完成移位相加、乘法、輸出相加功能,但靜態模塊在重構過程中保持固定不變,局部重構模塊在重構前后功能改變。當多個重構模塊使用同一個可重構區域的時候,每個模塊的文件名和端口配置必需和頂層實例化的可重構模塊一樣[7]。

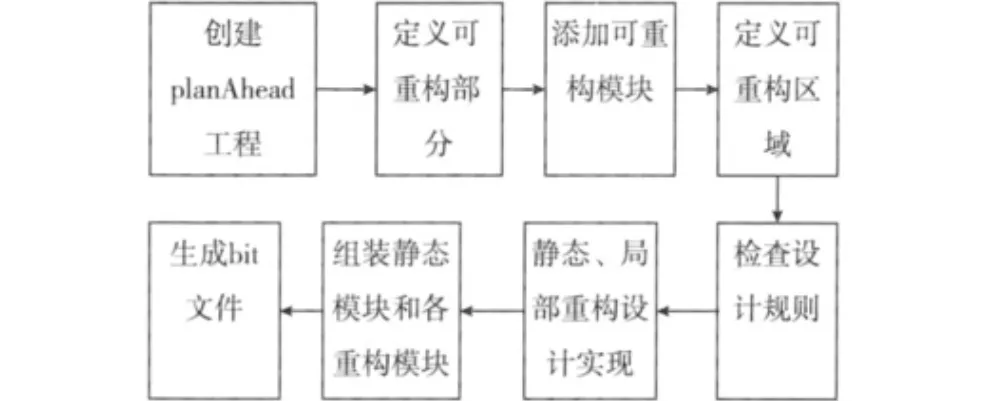

4.2 實現局部可重構

完成前面的編碼和綜合工作后,將進入實現局部重構的過程,如圖9所示。此過程在Xilinx的局部重構平臺PlanAhead集成環境下實現。

圖9 局部重構的流程

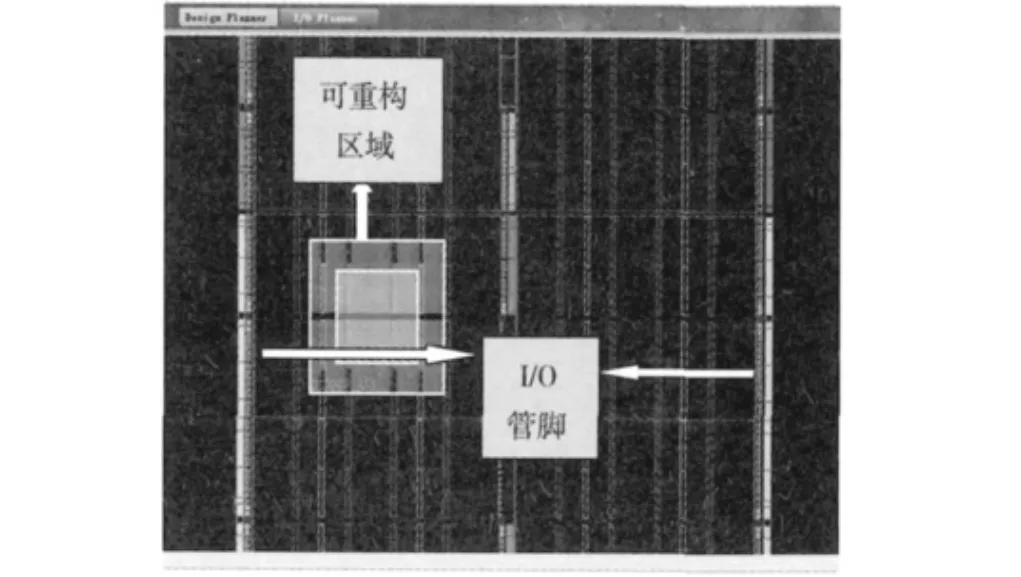

圖10 顯示了在FPGA上可重構區域和I/O管腳的布局以及總線宏的位置。實現的最后一步是組裝,組裝靜態模塊和局部可重構模塊,并創建配置FPGA的位流文件。在此過程中,將創建好兩種位流文件:整體位流文件(full bit file),根據需要,在每個可重構區域中選擇一個可重構模塊作為缺省模塊被并入整體位流文件,用于FPGA初始化時裝載配置;局部位流文件(partial bit file),由重構模塊生成,該文件在整體位流文件配置FPGA后再下載到FPGA中,此時靜態模塊仍處于運行狀態,最后實現FIR濾波器階數的轉變。

圖10 可重構區域和I/O管腳的布局

5 驗證和結果

本實驗選擇一個只含8階FIR濾波器系數的可重構模塊和一個靜態模塊(8階FIR濾波器功能)合并為整體位流文件,該文件大小為1 673 kbyte,通過下載線下載到Virtex-4 XC4VSX35 FPGA設備上。之后下載構成16階濾波器的可重構位流文件,大小為74 kbyte,該部分只重構可重構區域的電路,靜態部分將不受任何影響。驗證時,把兩頻率的正弦波信號疊加后,經過ADC,再通過FPGA上的濾波器模塊,最后通過USB傳輸到計算機,并用MATLAB顯示出濾波前后的時域及頻域圖形,如圖11所示。疊加信號經過可重構FIR濾波器后,將高頻信號濾除了,從而驗證了可重構設計的正確性。

由于位流大小直接與占用硬件資源大小及配置時間成比例,只加載重構模塊74 kbyte的配置信息就能實現更高階FIR功能,而代替了整個FPGA重構(整體文件為1 673 kbyte),這樣一來大大縮短配置重構時間。表1顯示了整體和重構位流文件的配置速度。

表1 兩種位流文件的配置速度

本文還與直線型結構的可重構FIR濾波器的進行對比,同一性能的FIR濾波器,映射后的Slice、LUT及DSP48使用個數對比,如表2所示,從表中可以計算出對稱轉置結構的可重構濾波器可以節省大約12%的Slice資源、45%的LUT資源及50%的DSP48資源。

6 總結

本文描述一個在Xilinx Virtex-4 XC4VSX35 FPGA設備上采用動態局部可重構的方法來設計階數可變的FIR數字濾波器,與同類的濾波器相比,資源配置更少,Slice、LUT和DSP48s資源分別節省大約12%、45%和50%,重構時間提高了80%,并能實現重構區域資源的時分復用,同時提高了該區域資源的利用率及靈活性。動態局部可重構技術能夠動態插入或刪除局部可重構模塊,使得FIR濾波器系數得到實時更新,階數能夠更靈活地改變。

[1]王靜,魚云岐.基于FPGA的FIR數字濾波器設計與仿真[J].國外電子元器件,2008(11):90-92.

[2]梁甲華,林爭輝,林濤.基于可重構FPGA技術的自適應FIR濾波器的實現[J].電子工程師,2004,30(12):48-50.

[3]谷鑾,徐貴力,王友仁.FPGA動態可重構理論及其研究進展[J]計算機測量與控制,2007,15(11):1415-1418.

[4]劉慶良,盧榮軍,李建清.FIR數字濾波器的FPGA實現研究[J].電子設計工程,2010(3):59-61.

[5]KARTHIK S,SHILPA J.Implementation of partial reconfigurable FIR filters using dynamic partial rconfiguration[J].Computer Science,2011(1):65-69.

[6]CARDOSO J M P,HUBNER M.Reconfigurable computing[M].New York:Springer-Verlag,2011.

[7]YEONG J,HANHOLEE O,LEE C H.Dynamic partial rconfiguration FIR filter design[J].Computer Science,2006(5):30-35.