基于F P G A的異步串行通信的實現

陳啟發 羅 京

(中國南車股份有限公司 株洲電力機車有限公司,湖南 株洲 412001)

0 引言

異步串行通信要求的傳輸線少、可靠性高、傳輸距離遠,被廣泛應用于計算機和外設的數據交換。異步串行通信是以幀為單位,每幀按照通信協議進行傳輸,并且數據的發送端和接收端都使用各自的時鐘控制數據的發送和接收過程[1];接收端先數據解調,然后將有效數據傳輸給終端設備。

對于接收端的數據解調,首先要從數據流中提取同步信號位信息,然后提取數據位信號。同步信號位信息提取性能的好壞直接影響到整個數據的解調質量,甚至影響整個通信系統的性能[2]。傳統的幀設計很難做到位同步,隨著FPGA的飛速發展及Verilog語言的出現,用FPGA來實現同步信號位的提取,不僅簡化了電路、縮小了體積、提高了可靠性,而且設計時的靈活性更大、保密性更好。

1 通信協議及接收思路

FPGA的輸入是485收發器傳輸過來的信號rxd,并不是標準的485通信協議,其幀結構如圖1所示,其特點如下:

圖1 輸入信號rxd波形

(1)每一幀長度固定為25位;

(2)波特率為 1Mbit/s;

(3)每一幀由同步信號位和數據位組成,前13位為1111111111110的二進制同步序列,后12位為數據位;

(4)當矩形脈沖信號占空比為75%時,表示數據“1”;當矩形脈沖信號占空比為25%時,表示數據“0”。

FPGA接收信號的步驟如下:

(1)先檢測輸入信號每一位數據的上升沿,當檢測到輸入信號的上升沿,把輸入采樣信號tb_zhen置1,并開始計數,當計數計到輸入信號每一位的中間位置時,把tb_zhen置0,保證每次采樣都是在每一位數據的中點處,可以得到一組與輸入同步的30%占空比的方波信號tb_zhen;

(2)在tb_zhen下降沿的時候,開始讀取輸入信號電平,此時得到的邏輯電平就認為是輸入信號的電平信號,讀取的信號電平較輸入有0.5us的延時;

(3)幀同步的提取,可以考慮采用有限狀態機實現幀同步,也可以采用隊列模式實現,當13位寄存器中出現1111111111110時,就認為同步完成,數據位已經到來;

(4)當檢測到同步完成后,開始接收和發送數據,當下一次同步完成時,進行下一輪數據的接收和發送。

2 軟件設計

部分程序的源代碼如下:

捕捉到幀同步完成后,就可以開始采集數據位,然后根據需要采用串行或并行發送給上位機。

程序經過綜合后得出的原理圖模型如圖2所示。

圖2 原理圖模型

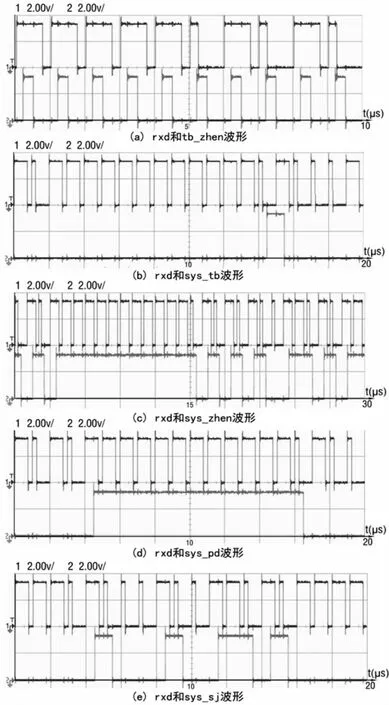

圖3 實際檢測的波形

(1)clock系統時鐘輸入,為30M的晶振;

(2)rxd為485芯片傳輸的信號,數據的輸入端口;

(3)tb_zhen為輸入信號采集的同步讀取信號;

(4)sys_tb為幀同步完成信號;

(5)sys_pd為同步信號位數據串行輸出端口;

(6)sys_zhen為完整的數據幀串行輸出端口;

(7)sys_sj為解幀后的串行輸出端口。

3 實測波形

為了進行對數據提取的檢測,將程序下載到EP1C6系列的FPGA里進行數據采集,為了便于觀察,主要測量5種波形:tb_zhen的波形、幀同步完成sys_tb波形、完整的幀sjs_zhen波形、同步信號位sys_pd波形、數據位sys_sj波形。如圖3所示。(a)是rxd和tb_zhen的波形,(b)是 rxd 和 sys_tb 的波形,(c)是 rxd 和 sys_zhen 的波形,(d)是rxd和sys_pd的波形,(e)是rxd和sys_sj的波形。從下面的波形可以看出,解幀后的輸出波形和輸入波形是一樣的,說明對輸入電平的讀取及幀同步過程是正確的,并成功地提取了同步信號位和數據位數據。

4 結束語

本文使用Verilog語言成功地實現了對輸入電平的正確讀取和幀同步的提取,體現了FPGA的強大功能。文中的通信協議并不是標準的485通信協議,但是實際效果比485通信協議方便可靠,具有一定的應用價值。

[1]陽憲惠.現場總線技術及其應用[M].清華大學出版社,1999.

[2]葉懋,景新辛,楊海燕.基于Verilog語言的幀同步的實現[J].系統仿真技術,2007.

[3]夏宇聞.Verilog數字系統設計教程[M].北京航空航天大學出版社,2008.

[4]Lee,Weng Fook.Verilog coding for logic synthesis[M].Hoboken,N.J.:Wiley-Interscience,2003.