數字系統的現代軟件設計

左智成

(中原文化藝術學院,鄭州450002)

數字系統的硬件設計目前有兩種方法,即傳統系統硬件設計和現代系統軟件設計.電子工程師因其使用設計方法的不同,被劃分為硬件工程師和軟件工程師.他們專心于自己的設計事業,很少從事跨界工作,尤其軟件從業人員更是如此.隨著微電子技術的迅猛發展,特別是計算機技術的日新月異和硬件描述語言(Hardware Description Language,HDL)的開發和使用,這種傳統的、難以逾越的溝界被打破,電子工程師無論是硬件設計人員還是軟件從業者都已經開始使用HDL語言設計趨于合理、符合生產要求的數字設備.而且,使用HDL語言設計數字系統與傳統方法設計相比,優勢極為突出,可降低設計難度,在設計的每一步都可進行仿真,能及早發現問題,縮短開發周期,且文件資料歸檔方便,可節省大量的人力物力資源,它是硬件設計領域的一次變革,對系統硬件的設計將產生巨大的影響[1].

1 數字系統硬件的傳統設計方法

在未開發計算機輔助設計系統的年代,電子工程師均采用傳統的設計方法設計數字系統[2].這種數字系統的設計方法是在“人工”的基礎上形成的,具有以下幾個主要特征:

1.1 自底向上的設計方法

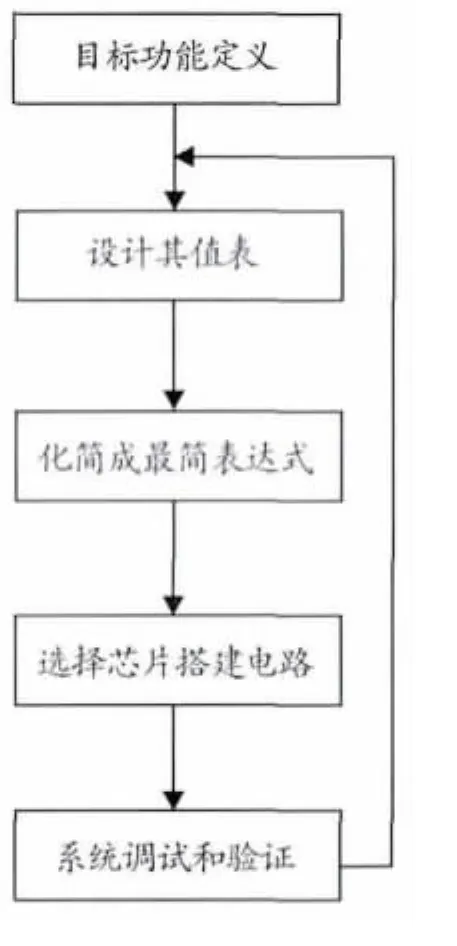

自底向上的硬件電路設計方法的主要步驟是:當給定生成目標后,設計真值表,使用卡諾圖或邏輯代數化簡成最簡表達式,然后采用“搭積木”的方法選擇功能固定的標準芯片實現生成,最后調試和驗證并修改相關設計.上述設計方法也稱自下向上的設計方法,它充分體現在各功能模塊的電路設計中,其設計流程如圖1所示.

1.2 通用邏輯元器件是構成系統的主要部件

在傳統的硬件電路設計方法中,設計者總是根據系統的實際需要,力求選擇市場上能買到的邏輯元器件來搭建所要求的邏輯電路,從而實現系統的硬件設計.對于由微處理器及相應硬件組成的系統中,部分系統的硬件功能可以用軟件來實現,這在某種程度上簡化了系統硬件電路的設計,但是這種選擇通用元器件構成數字系統的模式并未改變.

圖1 傳統設計流程

1.3 在系統設計硬件搭建的后期進行仿真和調試

仿真和調試在傳統的數字系統設計方法中,通常是在完成系統硬件搭建以后才能進行,這是因為進行仿真和調試的工具一般為系統仿真器、邏輯分析儀和示波器等.它們只有在數字系統硬件構成后才能使用.因此,在設計過程中潛伏存在的問題只能在后期被發現,這就對系統設計人員提出了更高的要求,一旦出現失誤,系統設計將存在較大缺陷,那么極有可能推倒進行重新設計,使得設計周期大為延長[3].

1.4 電路原理圖是設計的主要文件

在使用傳統的硬件設計方法進行數字系統設計并調試完結后,得到的硬件設計文件主要是由若干張電路原理圖集合形成的文件.在這些集合文件中詳細說明了各邏輯部件的名稱及相互間信號的依賴關系,是用戶今后使用和維護系統的依據.對于較為簡單的小系統,這種電路原理圖只要幾張、幾十張至幾百張即可,但如果系統龐大,硬件結構相對復雜,那么這種原理圖文件可能有幾千張、幾萬張乃至幾十萬張,這就給原理圖文件的歸檔、閱讀、修改和使用帶來了極大的困難,對系統的使用和維護帶來了極大的不便.

2 現代的系統軟件設計方法

隨著微電子技術的迅猛發展,大規模、超大規模專用集成電路(ASIC、Application Specific Integrated Circuit)的研制和使用,各ASIC制造廠商為了提高研、發、產效益,縮減研發周期及增強研發成果的繼承性,均開發了適于各自目的的系統設計軟件,即HDL語言.現時使用最廣泛的是美國國防部研發的VHDL(Very High Speed Integrated Circuit,HDL)和Verilog公司的Verilog硬件描述語言[4].利用HDL語言設計數字系統有以下幾個特征:

2.1 自頂向下的模塊化設計方法

自頂向下的模塊化設計方法,就是從系統的總體功能要求出發,先進行整體規劃,然后確定設計方案,自頂向下逐步將設計指標分解到各模塊,再進行模塊和細節設計,最后實現數字系統的總體設計.這種設計方法將數字系統的設計自頂向下分成三步進行.

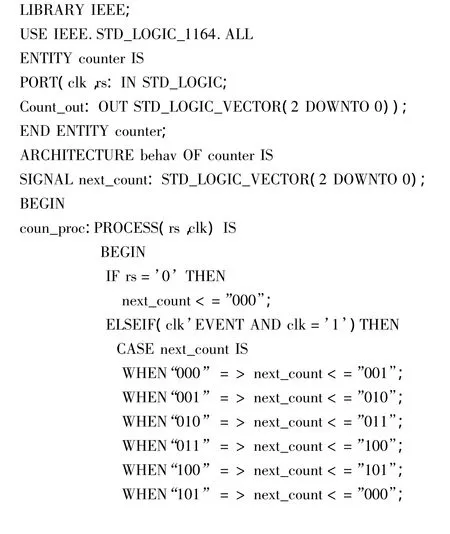

第一步是行為描述(頂部描述).它是對整個數字系統頂部功能的描述,建立系統的數學模型.通過對系統頂部功能的數學模型描述、仿真來發現設計中早期存在的功能不完善、行為描述不準確的問題.這一階段主要考慮數字系統的整體結構及工作過程是否達到系統總體功能的預設要求,不考慮行為描述實際的操作和算法實現.下面以六進制計數器為例說明以行為方式描述的工作特性.

以上VHDL語言程序勾畫出了六進制計數器的輸入、輸出引腳和內部計數過程的計數狀態變化時序及關系.這實際上是計數器工作狀態的描述.當該程序仿真通過以后,說明六進制計數器模型是正確的.

第二步是寄存器傳輸(Register Transfer Level,RTL)描述,也稱數據流描述.第一步頂部描述建立系統結構的數學模型因其程序抽象度高,難以直接映射到數字系統內部的具體邏輯部件結構,不便用硬件來實現.因此必須將數字模型方式描述的VHDL程序轉化為數據流方式描述的VHDL程序.只有這樣,才能求得系統的邏輯表達式,再進行下一步的綜合.下面仍以六進制計數器為例,說明行為方式描述轉化為RTL方式描述.

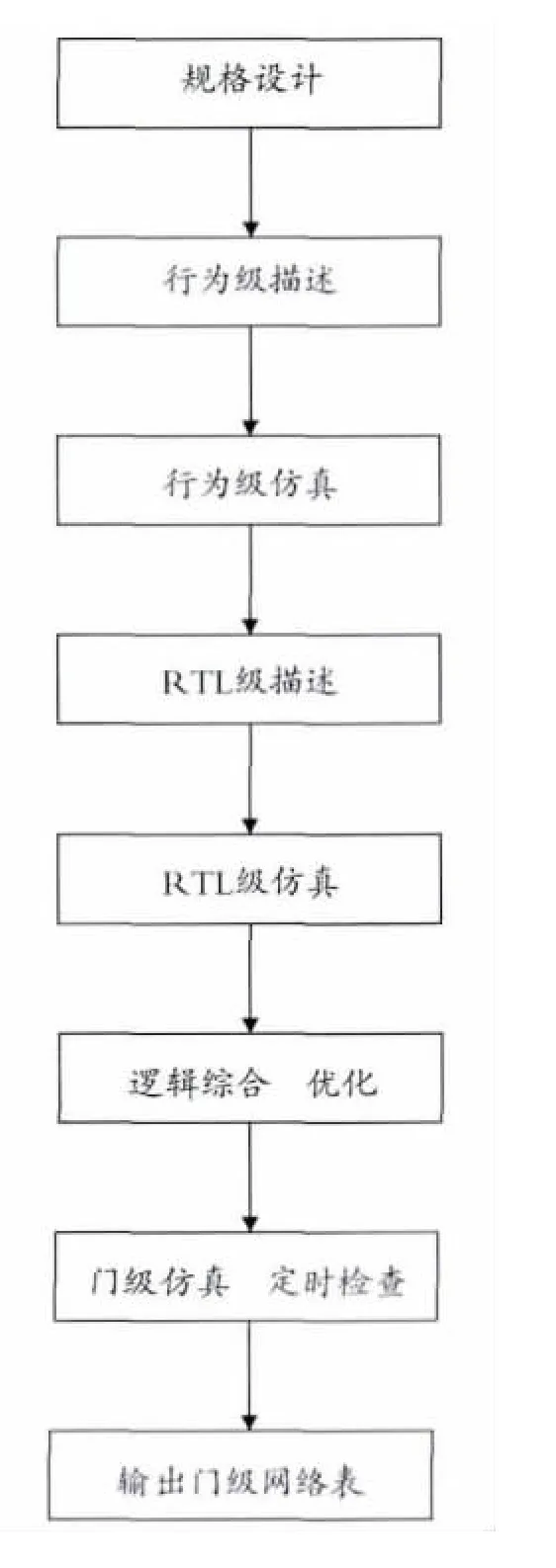

圖2 自頂向下設計流程

在以上的RTL描述方式中,JK觸發器、D觸發器、與門和或非門都可以在庫WORK.NEW.ALL中直接調用,且構造體直接描述了它們之間的連接關系.與行為方式描述相比,RTL描述更接近于實際電路的描述.

在數據流描述的源程序編寫完成后,用仿真軟件對該方式描述的源程序進行仿真.若仿真結果正確,就可進行第三步的邏輯綜合.

第三步邏輯綜合.邏輯綜合的目的是用邏輯綜合工具將數據流描述的程序轉換成門級網絡表,即用基本邏輯部件表示的文件.若需要,可進一步將邏輯綜合的結果以邏輯原理圖方式輸出.這個邏輯原理圖就相當于用傳統方法設計的硬件電路,根據系統功能體系要求畫出系統的全部邏輯電路原理圖.以門級網絡表為基礎,對邏輯綜合結果再次在門級電路上進行仿真,測試信號依存關系和定時關系.若都正常,那么數字系統的硬件設計就此成功完結.若這三步的某一步發現問題則都可隨時返回上一步,查看源程序,尋找和修改出現相應錯誤的模塊、進程或結構,然后繼續下一步.

邏輯綜合結束后,在最終完成硬件設計時,有兩種選擇:第一種是采用自動布線程序將邏輯綜合的結果轉換成相應的ASIC芯片的制造工藝,做出ASIC芯片;第二種是將結果轉化成CPLD(復雜可編程邏輯器件)或FPGA(現場可編程門陣列)的編碼點,而后寫入對應芯片,完成數字系統設計.整個設計過程如圖2所示.

2.2 系統設計合理化、體積微型化

如前所述,眾多ASIC芯片制造商提供的軟件均可支持或兼容HDL語言,所以,電子工程師在設計數字系統的硬件電路時,可根據硬件系統的需求,自行設計ASIC芯片或可編程邏輯器件.這終將會使數字系統的硬件電路趨于合理,體積大為縮小,走向微型化.

2.3 全過程仿真

從自頂向下的三步設計過程可以看出,仿真始終貫穿在系統硬件設計的各環節之中,即行為(頂部數學模型)仿真、數據流(RTL)仿真和門級(門電路原理)仿真.這就使在系統設計各個階段存在的潛伏問題能被及時發現和更正.較之傳統自底向上設計的后期仿真,自頂向下的三步設計最大限度地縮減了系統的設計周期,節省了大量的人力、物力資源.

2.4 系統的設計周期大為縮減

在傳統硬件電路的設計方法中,電子工程師必須在設計前求得電路的邏輯表達式或真值表(或狀態表),這是相當繁雜和困難的過程,尤其是在硬件系統較為復雜時更是如此.而用現代軟件的設計方法設計硬件電路時,設計者無需得到邏輯表達式或真值表.例如六進制計數器,只要知道六進制計數器的6個計數狀態就行了,而無需寫出相關電路的邏輯表達式.這使硬件電路的設計愈來愈便利,難度也大為降低,縮短了硬件系統的設計周期,提高了設計效率.據有關資料統計,就此一項可使系統的設計周期縮短大約1/3 ~1/2[5].

2.5 HDL的源程序是設計的歸檔文件

如1.4所述,在傳統硬件電路的設計中,電路原理圖是最后得到的主要文件,而利用現代軟件設計硬件電路時,得到的設計文件是HDL編寫的源程序,需要時就可轉換成電路原理圖.用源程序作歸檔文件有以下優點:(1)資料量小,便于紙質保存.(2)繼承性好.在設計任何硬件電路時,可利用現有文件中的進程和過程等程序.(3)可閱讀性強.閱讀理解源程序要比理解電路原理圖容易一些.在源程序中能容易找出某部分電路的邏輯關系和工作原理.

3 結語

數字系統硬件設計的兩種方法目前在實際工作中都有使用.傳統的硬件電路設計方法已經沿襲使用了幾十年,是廣大電子設計者所熟悉和掌握的一種方法.但是,隨著計算機技術日新月異、微電子技術的迅速發展,傳統的設計方法已無法跟進現代技術的發展.一種嶄新、采用現代軟件語言設計的硬件電路方法正在蓬勃發展,它的出現使硬件電路設計的難度大為降低,設計周期大為縮短,節省了大量的人力物力,對硬件電路的設計產生了革命性的變化.

[1]侯伯亨,劉凱,顧新.VHDL硬件描述語言與數字邏輯電路設計[M].第3版.西安:西安電子科技大學出版社,2009.

[2]文漢云,劉鵬,胡杰.數字邏輯與數字系統設計[M].北京:清華大學出版社,2012.

[3]譚會生,昌凡.EDA技術及應用[M].西安:西安電子科技大學出版社,2009.

[4]王金明.數字系統設計與Verilog HDL[M].第4版.北京:電子工業出版社,2011.

[5]朱志平.基于VHDL的交通管理器設計[J].渭南師范學院學報,2012,27(6):24-28.