淺談線路板圖形電鍍阻鍍成因及解決之道

林偉東 吳榮萱

(深圳市正天偉科技有限公司,廣東 深圳 518126)

1 前言

印制電路板主要趨勢體現(xiàn)為輕、薄、短、小,其集成密度、層數(shù)不斷增加,可靠性要求不斷加嚴(yán)。特別是孔徑的不斷變小,孔徑也由之前的0.40 mm變小至0.25 mm、0.20 mm,甚至更小。這直接導(dǎo)致在PCB每個(gè)制程的難加大很多,如PTH線沉銅效果不佳,電鍍線灌孔性不行,顯影線、水平線清洗及烘干效果不好等諸如此類的問題層出不窮。在此,引入電鍍阻鍍這個(gè)問題。阻鍍,顧名思義就是阻礙板件銅面正常電鍍,使銅厚不夠或鍍銅錫不良等。

2 電鍍阻鍍的類型

2.1 點(diǎn)狀阻鍍

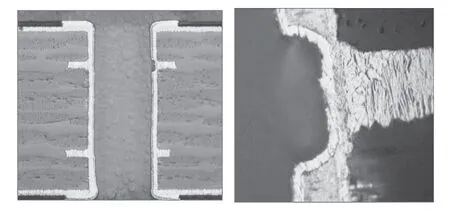

圖1為鍍完二銅及錫的切片(右側(cè)放大圖),點(diǎn)狀位基本無鍍上二銅,只鍍上了錫,所以定義為點(diǎn)狀阻鍍。

圖1 點(diǎn)狀阻鍍

2.2 孔口處流膠阻鍍

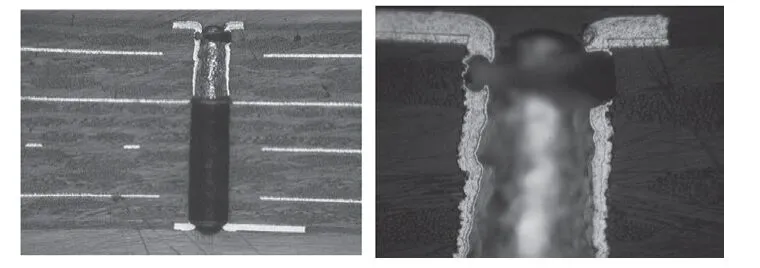

如圖2孔破位置斷口較整齊,內(nèi)層銅箔回蝕現(xiàn)象較嚴(yán)重,孔破位置明顯為二銅及錫皆未鍍上,受蝕刻液攻擊所至,兩端均有孔破,此為孔口處流膠阻鍍。

圖2 孔口處流膠阻鍍

2.3 二銅漸薄型阻鍍

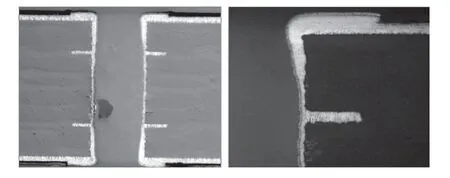

如圖3孔內(nèi)一次銅完整,但二次銅從孔口到孔中心從厚至薄,直至無二次銅的阻鍍模式。

圖3 二銅漸薄型阻鍍

3 驗(yàn)證電鍍阻鍍的根因

按人機(jī)料法環(huán)因素分析,影響電鍍阻鍍的因素有許多,而最主要因素有D/F貼膜后至曝光停留時(shí)間長,D/F顯影后至PPL電鍍停留時(shí)間,D/F顯影干膜殘?jiān)赡で疤幚項(xiàng)l件,干膜翻洗不良等。現(xiàn)就這幾個(gè)因素結(jié)合親身經(jīng)歷的案例進(jìn)行剖析。

3.1 停留時(shí)間的影響

針對板電后,貼干膜后及顯影后不同段的停留時(shí)間,設(shè)計(jì)以下DOE試板驗(yàn)證(萬孔板:56000孔/PNL,板厚2.4 mm,孔徑0.30 mm,厚徑比8:1),結(jié)果見表1。……