一種高性能數(shù)字化采樣新平臺的研制

張 吉,謝 黎,汪世平

(國電南瑞科技股份有限公司,江蘇南京210003)

隨著新一代智能變電站的大力推進,繼電保護裝置數(shù)字化、集成化的趨勢日益明顯,對裝置類產(chǎn)品性能的要求越來越高[1]。GOOSE、采樣值(SV)和制造報文規(guī)范(MMS)三網(wǎng)合一概念的提出,是對裝置類產(chǎn)品平臺處理性能的考驗,高速、大容量的數(shù)據(jù)實時采樣要求使得傳統(tǒng)平臺在實時性及數(shù)據(jù)處理能力上后繼乏力。傳統(tǒng)的繼電保護平臺多采用雙CPU架構(gòu)或多核架構(gòu)。雙CPU架構(gòu)[2,3]在數(shù)據(jù)共享、設(shè)備間隔擴展、時鐘同步上存在很多技術(shù)壁壘,不利于智能變電站的推進和繼電保護的發(fā)展。多核架構(gòu)[4]適合于中低壓保護測控裝置,成本低、功耗少,但數(shù)據(jù)采樣的實時性和處理能力有限,無法滿足大容量、高速數(shù)據(jù)采樣的需求。目前繼電保護技術(shù)的發(fā)展趨勢是向網(wǎng)絡(luò)化、智能化、保護測控一體化、數(shù)據(jù)通信一體化方向發(fā)展,高速數(shù)據(jù)處理已經(jīng)成為評價裝置類產(chǎn)品重要指標之一[5,6]。因此需要一種高性能的采樣平臺,解決高速數(shù)據(jù)傳輸、大容量數(shù)據(jù)采樣、保護算法和數(shù)據(jù)采樣同步等問題。文中提出的高性能平臺采用外設(shè)組件互連標準擴展 (PCIe)高速總線技術(shù) (傳輸速度可達2.5 Gbps)解決了單CPU多路、大容量采樣數(shù)據(jù)實時傳輸問題,并融入了直接內(nèi)存操作(DMA)技術(shù),使得數(shù)據(jù)處理更加高效,完全滿足三網(wǎng)合一對數(shù)據(jù)吞吐率的要求;同時將保護采樣和保護算法放在一塊保護板上實現(xiàn),提高了CPU的利用率,減少了數(shù)據(jù)傳輸延時,增強了平臺的集成化,是適合于智能變電站推進的高性能數(shù)字化采樣新平臺。

1 高性能平臺軟硬件架構(gòu)

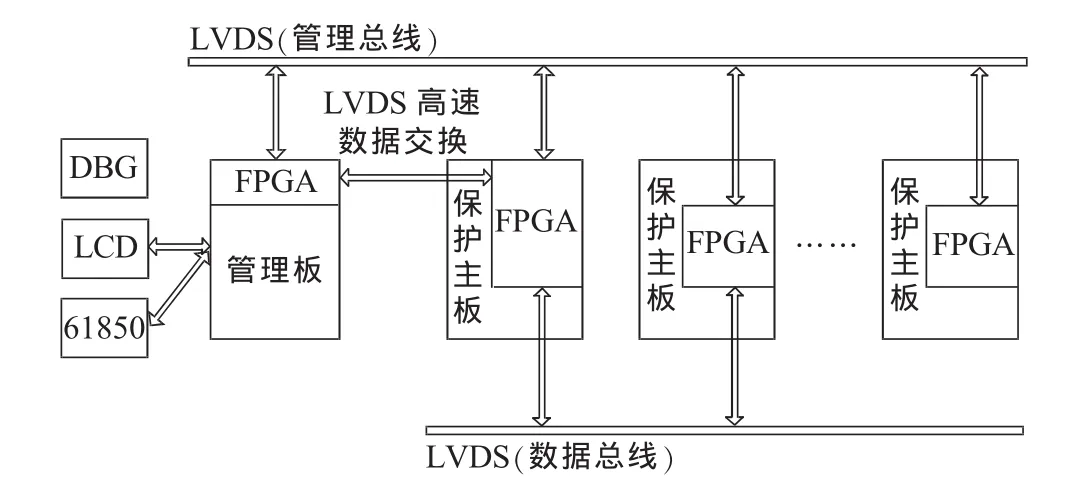

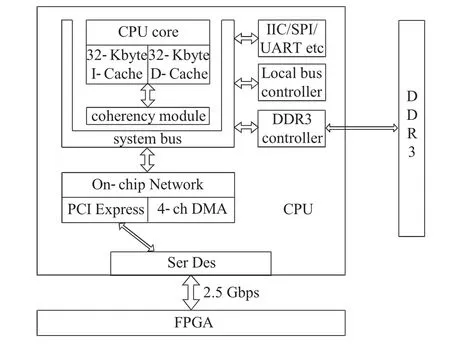

該高性能平臺軟件選擇LINUX 2.6內(nèi)核,硬件以高性能處理芯片P1011為基礎(chǔ)進行擴充,平臺總線框圖如圖1所示。

1.1 軟件架構(gòu)

圖1 平臺總線框圖

軟件架構(gòu)主要采用注冊機制,通過管理板統(tǒng)一管理,并隨時更新保護主板信息。軟件平臺作為硬件與應(yīng)用的接口,設(shè)計采用一體化結(jié)構(gòu),保護程序統(tǒng)一接口,大大提高了保護程序的可移植性。

高速數(shù)據(jù)交換總線是管理板和保護主板之間實時數(shù)據(jù)交換的橋梁。管理板負責對外通信、人機接口、運行信息、錄波文件、日志管理等功能,信息的調(diào)用和獲取都需要通過此接口與保護主板進行通信,實時性要求很高。

管理總線負責傳送配置信息、注冊信息及實時檢測等功能,同時采用節(jié)點拓撲方式,實時檢測是否有新板件加入或原板件移除,以備數(shù)據(jù)庫更新管理。數(shù)據(jù)總線負責將保護從板信息實時傳送給保護主板,由其進行統(tǒng)一管理和邏輯運算,同時保護從板也分擔了一些保護主板的運算邏輯,既減少了主板的負擔,又降低了數(shù)據(jù)交換流量。

1.2 硬件架構(gòu)

新平臺保護板硬件上采用一體化平臺設(shè)計,主從板件硬件統(tǒng)一,兼容性強,且對外接口一致,只需根據(jù)工程實際需要進行配置板件數(shù)量即可;同時機箱底板硬件采用熱插拔技術(shù),可在帶電情況下隨時插拔板件,與軟件架構(gòu)配合,實現(xiàn)不斷電基礎(chǔ)上對裝置間隔數(shù)量進行更改。

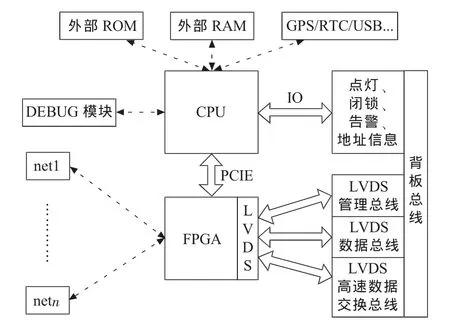

現(xiàn)場可編程門陣列(FPGA)在一體化設(shè)計上發(fā)揮了重要作用,保護主從板的功能區(qū)別通過FPGA得以實現(xiàn)。隨著其在電力系統(tǒng)中的作用日益加大,高速內(nèi)部總線、大容量的邏輯門電路,并且集成鎖相環(huán),可以對外部時鐘進行倍頻,主頻可達幾百兆以上,運算速度快,編程容易,應(yīng)用靈活,高端FPGA芯片內(nèi)部集成了很多模塊,比如串行接口、差分接口、PCIe、介質(zhì)訪問控制層(MAC)等。

保護主從板通過配置不同的FPGA程序,實現(xiàn)硬件一體化設(shè)計,如圖2所示。

圖2 保護主從板一體化框圖

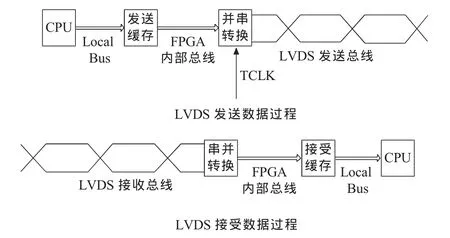

該系統(tǒng)中內(nèi)部通信主要采用低壓差分信號(LVDS)技術(shù),實現(xiàn)開入開出、信號同步等實時性較高的數(shù)據(jù)傳輸。LVDS總線分為發(fā)送總線和接收總線,物理上都由一對差分線構(gòu)成,實現(xiàn)點對點全雙工通信,通信速率為100 Mb/s,其數(shù)據(jù)交換過程如下。

FPGA將LVDS串行數(shù)據(jù)經(jīng)串并轉(zhuǎn)換后寫入FPGA中的接收緩存區(qū),CPU通過自身并行總線訪問接收緩存區(qū)獲取接收數(shù)據(jù)。CPU通過自身并行總線將要發(fā)送的數(shù)據(jù)寫入FPGA中的發(fā)送緩存區(qū),F(xiàn)PGA從發(fā)送緩存區(qū)中取到數(shù)據(jù)后進行并串轉(zhuǎn)換后通過LVDS總線往外發(fā)送。其收發(fā)過程如圖3所示。

圖3 LVDS差分信號傳送

2 PCIe高速總線技術(shù)

隨著現(xiàn)代處理器技術(shù)的發(fā)展,在互連領(lǐng)域中,使用高速差分總線代替并行總線是大勢所趨。與單端并行信號相比,高速差分信號可以使用更高的時鐘頻率,使用更少的信號線,完成之前需要許多單端并行數(shù)據(jù)信號才能達到的總線帶寬。

總線結(jié)構(gòu)根本性的變革主要體現(xiàn)在以下兩方面:一是有并行總線變位串行總線;二是采用點到點的互連獨享帶寬。將原并行總線結(jié)構(gòu)中橋下面掛連設(shè)備的一條總線變成了一條鏈路,一條鏈路可包含一條或多條通路。沒有專用的數(shù)據(jù)、地址、控制和時鐘線,總線上各種事務(wù)組織成信息包來傳送.地址空間、配置機制及軟件上均保持與傳統(tǒng)PCI總線兼容。

PCIe設(shè)備支持3種類型的地址空間,分別是存儲器、IO和配置空間。配置成功后,可以直接通過地址對其他設(shè)備進行訪問,實現(xiàn)數(shù)據(jù)共享。文中采用P1011芯片上的PCIe控制器,外接鏈路一個Lane,總線規(guī)范1.x,速率2.5 Gb/s。下面以LINUX2.6x為例,介紹其配置過程。

2.1 地址信息傳遞

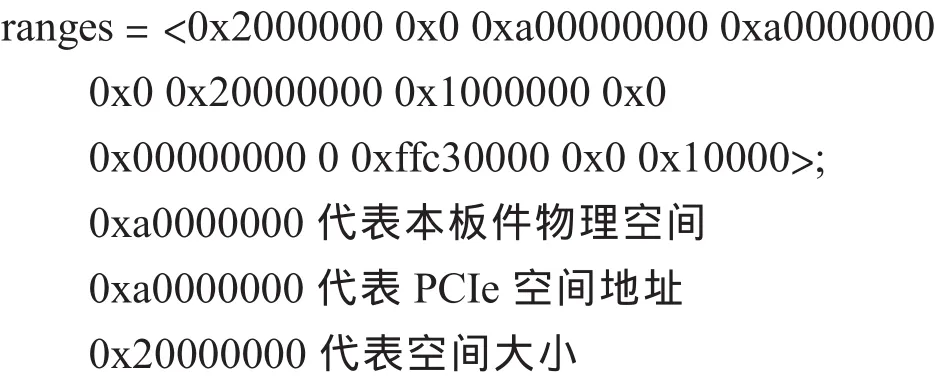

LINUX啟動獲取板件硬件設(shè)備信息是通過設(shè)備生成樹DTB來實現(xiàn),而PCIe空間地址等信息也在其中進行配置,修改p1011rdb.dtc中PCIe對外空間地址及大小:

并通過命令:

dtc–I dts–O dtb p1011rdb.dtc>p1011rdb.dtb生成.dtb文件,寫入指定ROM空間,系統(tǒng)啟動時將按此配置對PCIe進行初始化。

2.2 控制器原理

PCIe采用數(shù)據(jù)包傳輸方式,通過事務(wù)層、數(shù)據(jù)鏈路層和物理層,將數(shù)據(jù)報文發(fā)送到對端,通常將PCIe兩端稱為源端設(shè)備(RC)和終端設(shè)備(EP)。在一些復雜系統(tǒng)中,通過橋接芯片可實現(xiàn)RC對多個EP的訪問。

P1011所提供的PCIe控制器,可以更方便地對外設(shè)空間地址進行訪問。通過配置Outbound寄存器可實現(xiàn)RC對EP的空間直接訪問,通過Inbound寄存器可讓EP直接訪問RC空間。文中將CPU側(cè)作為RC端,配置Inbound。

Inbound包括3個基本參數(shù),由于EP無法對RC進行掃描,故此RC端需手動對Inbound所有參數(shù)進行配置,并要知道EP所有配置的PCIe空間地址,因此在編寫程序前將所有空間進行分配好,統(tǒng)一管理,防止重疊。

PEXITAR:配置本板物理空間地址。

PEXIWBAR:配置PCIe虛擬空間地址。與EP訪問的PCIe空間地址相對應(yīng)。

PEXIWBEAR:Inbound屬性。被訪問的大小不能超過EP的Outbound空間大小,尤其多個EP出現(xiàn)后,要對空間地址及大小嚴格控制。

該平臺CPU作為RC側(cè),首先對EP端進行掃描獲取EP信息,之后對控制器進行初始化,將配置信息通過配置空間地址寫入EP端,建立連接。

2.3 提高PCIe訪問空間速度

UBOOT啟動后初始化PCIe接口,建立與EP連接的高速通道,同時預留一片DDR3空間作為EP的訪問空間,在傳遞給內(nèi)核參數(shù)時保留此物理地址,使其不被MMU管理,這樣RC與EP之間即可在此物理空間內(nèi)進行實時數(shù)據(jù)交換。而在內(nèi)核驅(qū)動中將PCIe操作部分刪除,重新編寫驅(qū)動程序,直接訪問物理空間,減少中間環(huán)節(jié),大大提高了對總線操作效率。

2.4 信號質(zhì)量采集

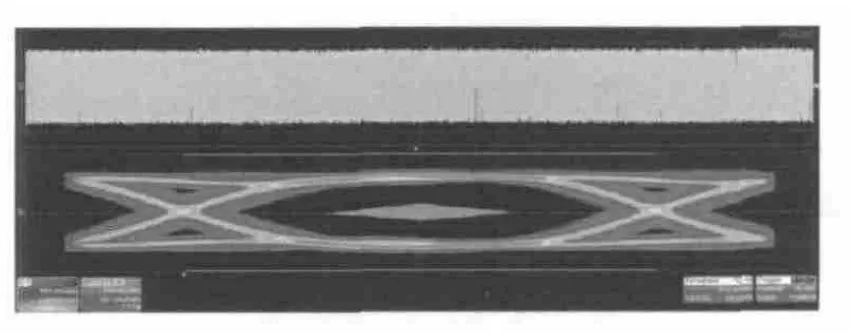

測量高速差分信號線噪音,保持良好的信號質(zhì)量十分重要,文中采用Lecroy的高速示波器SDA系列,帶寬 6 GHz,采樣率為 40 GHz;探頭 wave-link D620,帶寬為6 GHz。常溫下,同步時鐘,預加重-3.5dB,取靠近CPU側(cè)的引腳,基于PCIe1.x-RX眼圖模板的眼圖測試結(jié)果如圖4所示。可以看出眼圖質(zhì)量很好:眼圖比較對稱、眼線很細、消光比適中、Q因子很高。

圖4 PCIe效果眼圖

3 DMA技術(shù)

DMA是現(xiàn)代CPU的重要特色,可對不同速度的外設(shè)進行訪問,而不需要依于CPU的大量中斷負載。DMA傳輸是將數(shù)據(jù)從一個地址空間復制到另外一個地址空間,而PCIe就是對外設(shè)空間的直接訪問,將兩者融合后,大大提升CPU與外設(shè)的交換速度,充分利用高速總線,如圖5所示。

此平臺CPU內(nèi)部包含四路DMA控制器,采用其中一路作為高速數(shù)據(jù)傳輸。當啟動DMA時,CPU將系統(tǒng)總線控制權(quán)交給DMA,建立DDR3控制器與PCIe之間的高速通道,完成數(shù)據(jù)交換后,DMA控制器立即將系統(tǒng)總線控制權(quán)交給CPU。

圖5 DMA&PCIe傳輸框圖

手動控制此過程會增加CPU負荷,因此采用鏈式DMA方式,將收發(fā)緩沖區(qū)按鏈式指針模式做成環(huán)形結(jié)構(gòu),只需將待處理數(shù)據(jù)放入緩沖區(qū),由DMA控制器和CPU之間自行協(xié)商,完成傳輸過程,提高了程序處理效率。

DMA技術(shù)的引入,不僅提高了總線帶寬利用率,還節(jié)省了CPU負荷,大大增強了平臺的數(shù)據(jù)吞吐能力,實現(xiàn)高速數(shù)據(jù)的傳輸。

4 平臺性能驗證

采用此平臺研發(fā)的裝置順利通過了國網(wǎng)就地化測試和六統(tǒng)一測試。高速的總線技術(shù)、強大的CPU處理能力,使GOOSE、SV數(shù)據(jù)共網(wǎng)得以實現(xiàn),并順利通過了新一代智能變電站的三網(wǎng)合一測試。尤其在網(wǎng)絡(luò)風暴測試中,性能體現(xiàn)優(yōu)越,過程層8個共網(wǎng)口接收報文的流量分別可達百兆,處理800 Mb/s流量報文的同時,還能正確處理GOOSE、SV的有效報文數(shù)據(jù),且在此情況下CPU的負荷率遠遠沒有達到此平臺處理能力的上限,充足證明了此高性能平臺的優(yōu)越性。

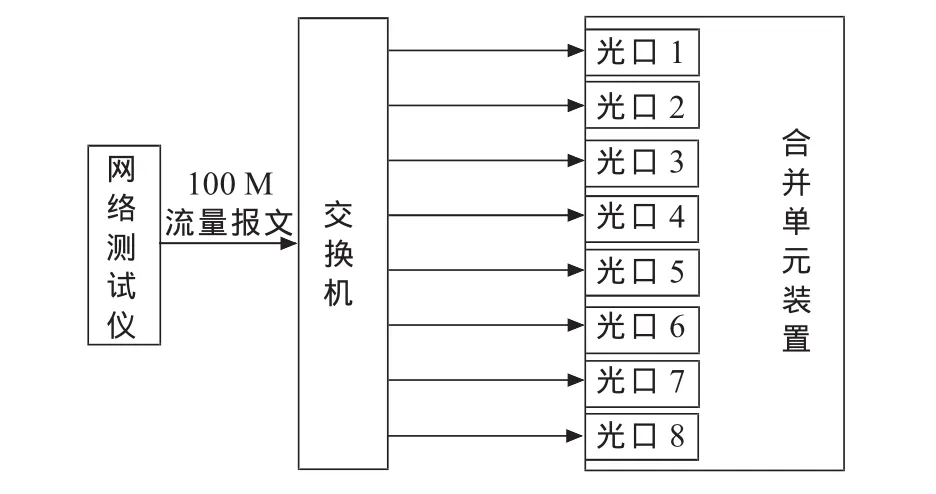

基于此平臺的保護、測控及數(shù)字化裝置,已成功應(yīng)用于現(xiàn)場并已投運,處理能力強、吞吐率高、運行穩(wěn)定,取得了用戶的一致好評。以合并單元裝置為例,測試平臺采樣速率及處理能力如圖6所示。

圖6 采集數(shù)據(jù)測試框圖及數(shù)據(jù)

網(wǎng)絡(luò)測試儀發(fā)送100 M流量報文,報文字長100字節(jié),發(fā)送報文總數(shù)為48 065 480。經(jīng)測試,8個光口接收報文總數(shù)為48 065 480個,丟包率為0,吞吐率達到800 Mb/s,達到測試目的。

5 結(jié)束語

采用高頻差分總線,提高平臺數(shù)據(jù)吞吐能力,是繼電保護的發(fā)展趨勢,文中所提出的高性能采樣新平臺有以下幾大優(yōu)勢:采樣容量大幅提升,PCIe技術(shù)的引入,使得網(wǎng)絡(luò)吞吐能力大大加強,同時LVDS高速總線又使數(shù)據(jù)的實時交互上不存在瓶頸,可滿足GOOSE、SV共網(wǎng)等大容量數(shù)據(jù)吞吐需求;處理速度提高,CPU主頻達800 MHz,并支持硬件雙精度浮點運算,大大提升保護邏輯處理能力,同時外部采用DDR3存儲芯片,使平臺整體性能大幅增強;集成化強,平臺軟件的注冊機制可將各保護功能相互隔離,互不干擾,實現(xiàn)不同保護功能共存于同一臺裝置中,滿足集成化的需求;擴展性能好。熱插拔技術(shù)及軟硬件一體化機制的引入,使裝置平臺對應(yīng)用間隔的擴展可在線實現(xiàn),平臺的軟件設(shè)計采用實時注冊機制,增加間隔單元只需將配置好的保護從板插入機箱任意插槽,保護從板會向保護主板主動進行注冊信息,方便快捷的融入系統(tǒng);成本降低。由于高速總線的引入,使得板件可配光口數(shù)目得到提升,單板可同時處理組網(wǎng)口的最大數(shù)可達8個,大大減少板件數(shù)量,降低了裝置整體功耗。PCIe總線技術(shù)和DMA技術(shù)的引入,無疑會給繼電保護行業(yè)帶來一場新的變革;同時,保護主板和保護從板的軟硬件一體化設(shè)計,可在線實現(xiàn)更改間隔數(shù)量,也緊跟著智能變電站發(fā)展的步伐。

[1]國家電網(wǎng)公司.Q/GDW 393-2009 110(66)kV~220 kV 智能變電站設(shè)計規(guī)范[S].北京:中國電力出版社,2010.

[2]王海燕,徐云燕.一種基于DSP+MPC的數(shù)字化保護測裝置[J].電力系統(tǒng)自動化,2010,34(9):112-114.

[3]彭志強,張小易,高 磊,等.智能變電站二次系統(tǒng)雙重化配置技術(shù)應(yīng)用分析.江蘇電機工程,2012,31(4):34-39.

[4]周華良,夏 雨,汪世平,等.多核處理器在中低壓保護測控一體化裝置中的應(yīng)用[J].電力系統(tǒng)自動化,2011,35(24):84-87.

[5]李 響,劉國偉,馮亞東,等.新一代控制保護系統(tǒng)通用硬件平臺設(shè)計與應(yīng)用[J].電力系統(tǒng)自動化,2012,36(14):52-55.

[6]張小飛,李佩娟,王潔松,等.智能變電站網(wǎng)絡(luò)應(yīng)用及測試技術(shù)研究.江蘇電機工程,2012,31(4):34-39.