3DSoC的多頻測試架構(gòu)設(shè)計

劉 蓓,汪千松,余 雷,陳 陽

(安徽工程大學(xué) 現(xiàn)代教育技術(shù)中心,安徽 蕪湖 241000)

2012年ITRS發(fā)布數(shù)據(jù),隨著集成電路(integrated circuit,IC)特征尺寸不斷減小,預(yù)計2020~2025年期間特征尺寸會跨越10nm的閾值,當減小至5~7nm時,將很難操作任何結(jié)構(gòu)的晶體管.三維集成技術(shù)充分利用了垂直空間,通過硅直通(Through-Silicon-Via,TSV)解決層與層之間的相連,打破了傳統(tǒng)平面布局中由于晶體管數(shù)目的增加導(dǎo)致連線長、功耗高、設(shè)計復(fù)雜度大的種種局限.由于不同類型的微電子系統(tǒng)可以堆疊在不同層[1],芯片的獨立性也大大提高.目前三維片上系統(tǒng)的研究已成為IC發(fā)展的重要趨勢.

在集成電路的實現(xiàn)過程中,測試是必不可少的一個環(huán)節(jié),芯片通常需要依次進行裸片測試和產(chǎn)品測試來確保合格率.芯片的測試時間是影響測試成本的重要因素,而測試時間在很大程度上依賴于測試訪問機制(Test Access Mechanism,TAM)的設(shè)計,因此在3DSoC的各項研究中,可測性設(shè)計(Design for Test,DFT)被認為是研究的重點[2].相關(guān)研究提出了傳統(tǒng)多頻SoC的測試方案并給出相應(yīng)研究成果.文獻[3]等研究了三維片上系統(tǒng)的測試優(yōu)化技術(shù),但在單一頻率下對所有不同種類的IP核進行測試,很難滿足異構(gòu)系統(tǒng)的需求.本文設(shè)計了一種多頻3DSoC的IP核測試外殼,并提出了相應(yīng)的TAM解決方案,在功耗限制下實現(xiàn)了對各IP核的測試,給出了具體的測試方法和結(jié)果.

1 SoC測試結(jié)構(gòu)

圖1 SoC測試結(jié)構(gòu)

SoC測試結(jié)構(gòu)如圖1所示.由圖1可知,測試源可以提供被測電路所需的測試激勵;測試宿通過對比預(yù)期結(jié)果和測試響應(yīng)來確定測試電路功能正常與否;測試源和測試宿都由自動測試設(shè)備(Automatic Test E-quipment,ATE)提供.TAM是測試數(shù)據(jù)傳輸?shù)耐罚捎脧?fù)用機制實現(xiàn)深嵌在SoC內(nèi)部的IP核的測試,TAM是解決SoC測試的根本方法.IP核的測試外殼本質(zhì)上是IP核與外部的硬件電路接口,負責(zé)將測試激勵移入IP核,并及時移出測試響應(yīng).當IP核正常工作時,測試外殼不起作用;當IP核被測試時,它作為IP核和TAM之間的接口,為測試數(shù)據(jù)提供傳送通道;當同一TAM的其他IP核測試時,它起到隔離作用,從而不影響其他IP核的測試.

2 3DSoC多頻測試架構(gòu)設(shè)計

目前針對IP核的測試都是在統(tǒng)一的工作頻率下進行的,即測試訪問接口Wrapper的設(shè)計基本上都是假設(shè)所有IP核在同一頻率下被測試.但是針對3DSoC芯片中的不同功能模塊,運行的時脈頻率也不盡相同,為了降低測試成本,需采用并行測試方法來減少測試時間,這就要求ATE提供多種速率對其進行測試,使得原本就昂貴的ATE更是增加了設(shè)備投資成本.本方案擬對3DSoC中不同種類的IP核在封裝時加入多頻控制器,通過測試訪問機制的優(yōu)化,使得ATE在單一頻率下就能對芯片進行測試.

2.1 測試掃描鏈設(shè)計

圖2 細粒度掃描鏈結(jié)構(gòu)

3DSoC中IP核的設(shè)計可分為2種[4]:粗粒度設(shè)計和細粒度設(shè)計.粗粒度設(shè)計不改變IP核原有的任何結(jié)構(gòu),采用平面布局的設(shè)計方法,內(nèi)部掃描鏈和輸入、輸出單元都在同一層上;細粒度設(shè)計是根據(jù)需要將IP核的掃描單元分割到不同層芯片上,更科學(xué)地對掃描單元進行布局,在功耗和性能上與IP核粗粒度設(shè)計相比具有更多優(yōu)勢.本文在3DSoC的設(shè)計架構(gòu)中采用IP核的細粒度設(shè)計方法,如圖2所示.圖2是一條掃描鏈,采用細粒度設(shè)計方案,將掃描鏈的7個掃描單元分別分布在兩層芯片上,層1上有3個掃描單元,層2上有4個掃描單元,不同層之間的掃描單元通過4根TSV連接,構(gòu)成一條掃描序列為1→2→3→4→5→6→7的掃描鏈.由于三維芯片的層間距離相對于掃描單元之間的距離非常短,因此可以忽略不計,通過這種方式構(gòu)成的電路與傳統(tǒng)電路相比就可以大大減少連線的長度,降低測試功耗.

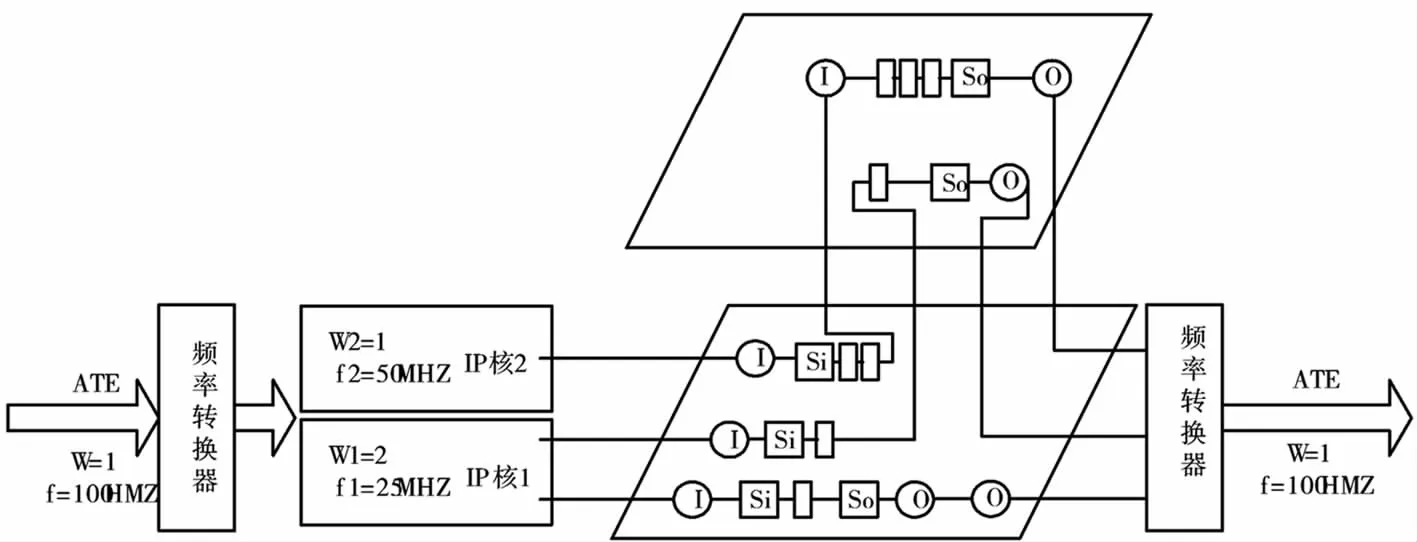

2.2 多頻測試架構(gòu)設(shè)計

假定ATE的工作頻率與所有IP核的內(nèi)部掃描鏈測試頻率都相同,那么ATE的端口可以直接將測試數(shù)據(jù)送入芯片進行測試.但實際情況是,ATE的工作頻率越來越高,而IP核的掃描鏈由于并行測試時功耗的約束,通常會設(shè)置的比較低,如果整個測試過程依賴IP核掃描鏈的測試頻率,勢必會造成ATE大量處于空閑狀態(tài)而導(dǎo)致測試時間的增加,進而影響到測試代價.

要讓高速ATE和低速TAM之間互連,并充分利用測試資源,就需要讓其兩者的帶寬匹配.帶寬B可定義為數(shù)據(jù)位寬度W與頻率f的乘積,即:B=W*f.通過使用串并/并串結(jié)構(gòu)的頻率轉(zhuǎn)換器,使得高帶寬的ATE可以同時與多個低帶寬低速率的TAM相連,從而充分利用測試資源.假定測試過程中ATE提供的數(shù)據(jù)位寬度和頻率分別是WATE和fATE,TAM的數(shù)據(jù)總線寬度和頻率分別是WTAMi和fTAMi(i是TAM的個數(shù)),通過頻率轉(zhuǎn)換器后有下式成立:WATE*fATE=∑WTAMi*fTAMi.WATE和fATE是由ATE確定的,各子TAM通過調(diào)整各自的頻率和數(shù)據(jù)位寬度來滿足與ATE之間的帶寬匹配.

圖3 多頻3DSoC的TAM架構(gòu)

多頻3DSoC的TAM架構(gòu)如圖3所示.由圖3可知,被測電路包括IP核1與IP核2.假定ATE設(shè)備的工作頻率是100MHZ,TAM的數(shù)據(jù)位寬度為1,經(jīng)過頻率轉(zhuǎn)換器后,兩個子TAM的工作頻率分別設(shè)定為50HMZ和25MHZ.由于要滿足帶寬匹配原則,ATE的帶寬和TAM的帶寬在頻率轉(zhuǎn)換前后要保持一致,故IP核1和IP核2要進行測試外殼的封裝以滿足需要,外殼掃描鏈的個數(shù)分別調(diào)整為2和1,重構(gòu)后的IP核測試外殼和TAM滿足了頻率轉(zhuǎn)換的需要.頻率轉(zhuǎn)換器的實質(zhì)是封裝在IP核測試外殼上的硬件設(shè)備,本方案采用的是在IEEE1500測試外殼架構(gòu)中加入多頻控制器(Multiple Frequency Controller,MFC)來控制每個IP核的頻率變化.

掃描控制器是多頻控制器(見圖4)的重要組成部分,主要的功能是產(chǎn)生門控時鐘信號Gate_clk和使能信號Scan_en.門控時鐘信號用來控制測試激勵的移入,測試向量的執(zhí)行以及測試響應(yīng)的移出.掃描使能信號將每個IP核的測試向量按順序執(zhí)行,消除測試時鐘傾斜問題.這兩種信號的產(chǎn)生使低速TAM的時鐘可以取代高速ATE的時鐘成為可能.如果TAM的移位頻率fTAM小于ATE的測試頻率fATE,那么內(nèi)部控制FSM就要為控制狀態(tài)機FSM產(chǎn)生多路選擇信號.

圖4 掃描控制器

2.3 算法實現(xiàn)

假設(shè)一個3DSoC芯片有若干個IP核,IP核的參數(shù)包括輸入輸出單元個數(shù)、測試向量個數(shù)、掃描鏈條數(shù)以及掃描鏈的長度等.給定ATE提供的測試頻率fATE和測試數(shù)據(jù)位寬度WATE,由于各IP核的測試頻率不同,為了滿足帶寬匹配,必須對IP核進行測試外殼的封裝,重構(gòu)被測電路的TAM,在不同TAM數(shù)據(jù)位寬的限制下,結(jié)合各IP核的功耗,減少3DSoC的測試時間.

將IP核的測試掃描鏈按細粒度劃分布局在3DSoC中,并對其進行測試.首先對所有IP核進行測試時間估算,把所有內(nèi)部掃描鏈的輸入輸出端口串聯(lián)成一條外殼掃描鏈,沒有內(nèi)部掃描鏈的IP核將其輸入輸出端口串接,計算一條外殼掃描鏈的IP核的測試時間.測試一個IP核的時間可以表示為:T={1+max(Si,So)}*P+min(Si,So),其中Si是輸入外殼掃描鏈的長度,So是輸出外殼掃描鏈的長度,P為測試向量的個數(shù).根據(jù)IP核的估算測試時間進行三維空間布局,滿足每個子TAM上的IP核的測試時間盡可能均衡,這樣在并行測試中才能保證整個芯片的測試時間最短.這個問題在實現(xiàn)過程中可以轉(zhuǎn)變?yōu)镮P核的測試時間集合中選取任意個IP核的測試時間之和SUM與子TAM的個數(shù)之比的取法是否存在,這是一個NP完全問題.例如將IP核集分為2組,每組在其子TAM上進行測試,找出k個IP核的測試時間,使其之和最接近SUM/2,那么這k個IP核就是最優(yōu)解,滿足最優(yōu)化原理.包含2個子TAM的最優(yōu)化集合算法如圖5所示.

被測IP核在并行測試時要考慮到功耗的約束,因此ATE工作頻率fATE與被測電路的TAM的測試頻率fTAM相比要高很多.為了在硬件中實現(xiàn)方便,本方案中將fATE設(shè)置為fTAM的偶數(shù)倍.例如fATE的頻率設(shè)定為200MHZ,那么2個子TAM頻率可分別設(shè)定為100MHZ,50MHZ,3個子TAM頻率可分別設(shè)定為100MHZ,50MHZ,25MHZ.同一TAM中的IP核,在相同頻率下測試.

整個芯片的測試時間取決于各個并行測試的子TAM的測試時間的最大值.由于各TAM的測試頻率不同,對頻率較低的TAM分配較多的測試數(shù)據(jù)位數(shù),對頻率較高的TAM分配較少的測試數(shù)據(jù)位數(shù),采用均衡分配測試時間的原則,保證各子TAM的測試時間接近,那么芯片總測試時間最短,分配過程中保證每個子TAM的測試帶寬要匹配.此外,在測試過程中還需考慮到功耗的約束,由于采用并行測試,那么各并行測試的IP核的總功耗不能超過系統(tǒng)的額定功耗,相應(yīng)的算法如圖6所示.

圖5 最優(yōu)化集合算法

圖6 功耗限制下同一TAM的IP核測試調(diào)度

圖7 本方案測試時間

文獻[3]指出額定功率在1500~2500之間對d695的測試時間影響不大,故本文選擇在額定功耗為2000,WTAM設(shè)置為32,40,48,56,64下d695的測試時間,實驗結(jié)果如圖8所示.由圖8可知,隨著測試數(shù)據(jù)位寬的增加,測試時間呈現(xiàn)遞減趨勢;2-TAM和3-TAM多頻通道相比,2-TAM在測試時間上略占優(yōu)勢.因為在給定TAM下,多頻通道3-TAM比2-TAM在部分數(shù)據(jù)位寬中的分配減少,導(dǎo)致在這些TAM中的測試時間增加,因此影響了整體的測試時間.此外,本文與文獻[5-6]相比,平均測試時間分別減少了12.7%,3.5%和6.4%.

3 結(jié)論

本文提出了一種符合工業(yè)實際的3DSoC多頻測試架構(gòu)方案,并針對該測試架構(gòu)給出了功耗限制下的測試算法.通過仿真實驗的結(jié)果可以得出,在同樣的數(shù)據(jù)位寬度數(shù)限制下,本方案比傳統(tǒng)SoC相比可以獲得更少的測試時間.

[1] Y Xie,G Loh,B Black,et al.Design space exploration for 3Darchitectures[J].ACM Journal on Emerging Technologies in Computing Systems(JETC),2006(2):65-103.

[2] Lee H-H S,Chakrabarty K.Test challenges for 3Dintegrated circuits[J].IEEE Design & Test of Computers,2009,26(5):26-35.

[3] 歐陽一鳴,劉蓓.一種三維SoC綁定前的測試時間優(yōu)化方法[J].電子測量與儀器儀表,2011,2,164-168.

[4] Noia B,Chakrabarty K.Test-wrapper optimization for embedded cores in through-silicon via-based three-dimensional system on chips[J].Computer & Digital Techniques,IET.,2011,5(3):186-197.

[5] Iyengar V,Chakrabarty K,Marinissen.Test access mechanism optimization,test scheduling,SoC and tester data volume reduction for system-on-chip[J].IEEE Tran.On Computers,2003,52(12):1 619-1 632.

[6] Zhao D,Upadhyaya S.Dynamically partitioned test scheduling with adaptive TAM configuration for power-constrained SoC testing[J].IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems,2005,24(6):956-965.