基于FPGA的數字正交檢波的實現

靳鵬

【摘要】闡述了數字正交檢波的基本原理,設計完成了數字正交檢波在FPGA中的實現,最后給出了測試結果,驗證了設計的正確性。

【關鍵詞】正交檢波;FPGA

Implementation of Digital Orthogonal Demodulation based on FPGA

Jin Peng

Abstract:The basic principle of digital orthogonal demodulation is introduced.Later,it expounds the implementation of digital orthogonal demodulation in FPGA.Finally,the measurement is performed to verify the correctness of the design.

Keywords:Orthogonal Demodulation;FPGA

隨著軟件無線電技術的發展,傳統的模擬接收機已經被數字接收機所取代。相對于模擬接收機中所使用的模擬正交檢波,現在的數字接收機中普遍使用數字正交檢波,直接對中頻信號進行采樣,將模擬中頻信號轉換為數字信號,之后在數字域對信號進行處理,得到兩路正交的基帶信號[1]。這種方法相較于傳統的模擬正交檢波方法,具有非常高的精度和穩定性,并且可以提高系統的靈活性。目前,數字正交檢波主要是通過使用專用可編程芯片、DSP和FPGA這三種方式來實現。FPGA具有出色的并行處理能力,適用于相關運算和濾波等各種復雜的數字信號處理運算。此外,FPGA的可編程性使其具有極大的靈活性,非常便于系統的功能擴充和升級,是目前被普遍采用的一種數字正交檢波實現方法。本文基于Altera公司的StratixⅢ系列中的EP3SE110F1152來實現對一中頻窄帶信號的數字正交檢波及后續處理。

1.數字正交檢波的原理

對于一個實的窄帶信號,其可以表示為:

(1)

上式中xI(t)和xQ(t)分別是信號的同相分量和正交分量,為信號載頻,a(t),(t)分別為信號包絡和相位,并且有如下關系:

(2)

(3)

(4)

(5)

信號同相分量和正交分量構成的復包絡信號為:

(6)

它包含了信號的所有有用信息。I、Q分量的幅度和相位關系反應了期望信號的幅度和相位關系。因此,在正交解調過程中,I、Q分量的相對關系必須嚴格保持,以確保能得到高質量的信號。

在傳統的模擬處理方式中,正交I、Q兩路信號的解調是通過模擬復解調來實現的,其基本原理是用壓控振蕩器和鎖相環產生兩路正交的中頻載波信號[2]。使用模擬乘法器將輸入的中頻信號與兩路正交的中頻載波信號分別相乘來實現信號在頻域的搬移,然后通過低通濾波器得到I、Q兩路正交的基帶信號。受限于模擬器件的性能,模擬復解調方法的性能和穩定性都不夠理想。

使用數字正交檢波技術,可以很好地解決模擬處理方式中存在的I、Q兩路信號幅度不一致和正交誤差等問題,從而為后續的數字信號處理提供高質量的信號。在對中頻窄帶信號進行采樣時,如果根據Nyquist采樣定理[3]來進行采樣,則采樣速率要不低于信號最高頻率的兩倍。采樣速率過高會加大實現的難度,并且會增加后級信號處理的負擔。利用中頻采樣定理,可以用較低的采樣速率來實現對中頻窄帶信號的采樣,從而解決這一問題,且采樣后的數字信號沒有發生頻譜混疊現象,能準確地還原信號。根據中頻采樣定理,采樣率fs、信號中心頻率f0和信號帶寬B滿足以下關系[3]:

(7)

中頻正交采樣常用的方法有以下四種:低通濾波法、Hilbert變換法、數字插值檢波方法和函數插值法。這些方法的基本原理是一致的,只是在具體的實現方式上有所不同,都可以看作統一的低通濾波形式,下面僅僅介紹低通濾波法。

對式(1)中的窄帶中頻信號做正交解調處理:

(8)

(9)

上述處理是一個下變頻的過程,對其進行低通濾波:

(10)

(11)

其中:。

將上述過程映射到數字域,就可以得到中頻正交采樣的低通濾波法。以對式(1)和,進行采樣,并結合中頻采樣定理可以得到:

(12)

(13)

(14)

式(13)和(14)是分別以{1,0,-1,0}和{0,-1,0,1}為周期的兩個循環序列。低通濾波法的框圖如圖1所示。

圖1 低通濾波法框圖

2.數字正交檢波基于FPGA的實現

根據前文所述的數字正交檢波原理,其在FPGA中的實現主要有以下三個過程:數字混頻、低通濾波和抽取。

2.1 數字混頻

數字混頻通過將數字中頻信號分別與兩個正交的數字本振相乘來完成數字混頻。根據前文所述,數字本振可以使用{1,0 -1 0}和{0,1 0 -1}這兩個周期序列來代替。這樣就可以用數據本身、數據取反和0來取代傳統的乘法運算,然后通過選擇器將數據選擇輸出,完成數字混頻。采用這種方法可以簡化運算,同時還能夠節約乘法器資源。數字混頻的實現框圖如圖2所示。

圖2 數字混頻的實現框圖

2.2 低通濾波

在完成數字混頻之后,需要對信號進行低通濾波處理,以抑制掉鏡頻分量,保留正頻分量,從而得到I、Q兩路基帶信號。低通濾波通過FIR濾波器來實現。

在FPGA中,FIR濾波器通常使用FIR濾波器IP核或者乘法器來實現。在本設計中,先根據性能指標要求仿真計算得出一組濾波器系數,之后調用FIR濾波器IP核加載濾波器系數來實現FIR低通濾波器。

2.3 抽取

為了降低后級信號處理的壓力,需要通過抽取來對數據進行降速處理。抽取主要是根據系統要求選擇合適的抽取率,通過抽取時鐘實現對信號的降采樣。對數據的抽取可以通過FIFO、雙口RAM或者D觸發器來實現。

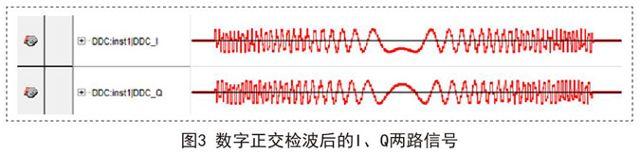

圖3 數字正交檢波后的I、Q兩路信號

3.測試驗證

根據前文所述,本設計在Altera公司的FPGA芯片上實現,使用ADI公司的A/D芯片AD6645來完成對中頻模擬信號的中頻采樣,實現模數轉換。測試中輸入的中頻模擬信號為一個線性調頻信號,使用signaltap在線邏輯分析儀采集到的經過數字正交檢波得到的I、Q兩路信號如圖3所示。

本文主要研究了數字正交檢波的基本原理以及其基于FPGA的實現方法。FPGA在設計和修改上的靈活性,可以使其滿足各種不同應用場合的要求,非常適合用來替代專用芯片實現數字正交檢波。經過測試驗證,本文中的設計達到了預期的結果。

參考文獻

[1]Pellon.L.E.A Double Nyquist Digital Product Detector for Quadrature Sampling.Signal Processing IEEE Trans on SP.1992,7,Vol.40(7):1670-1681.

[2]劉樹彬,吳義寶,安琪,等.一個雷達中頻信號數字復解調系統的實現[J].核電子學與探測技術,2003,7,Vol.23(7):364-366.

[3]楊小牛,樓才義,徐建良.軟件無線電原理與應用(第一版)[M].北京:電子工業出版社,2001.