簡單實用并有記憶功能的外同步系統

張永水 邢建力

【摘要】本文介紹了一種簡單實用并具有記憶功能的外同步系統。該系統主要應用于電源管理中,并且能夠提供三個功能:一是在未加同步信號時提供自身的內部振蕩頻率;二是當存在外同步信號時,系統利用數字技術能夠對外部信號進行準確的同步頻率輸出;三是在同步過程中,系統將會記住這一外加信號頻率值,并且在外部信號突然斷開之后使電路繼續工作在與原本所加的外同步信號幾乎相等的頻率值上。其中的誤差為5%以下,并且這一誤差是可以不斷改進縮小的。系統能鎖定的外同步頻率范圍為350KHZ到770KHZ。利用CSMS 0.6um CMOS工藝庫對所設計的電路進行仿真,能夠得到較好的預想效果。

【關鍵詞】外同步;簡單實用;記憶功能

一、引言

電源管理應用中,很多時候需要用到多塊芯片進行同時操作,而由于工藝和制造產生的失配誤差會使得即使是相同型號的芯片,其內部的振蕩頻率也會出現一些誤差。為了消除多個頻率接近的芯片并聯或者串聯產生的差頻噪聲問題,需要通過芯片的同步功能使得各個芯片間能夠同時工作在一個頻率上[1]。同時外同步功能也可以控制芯片工作在某一特定需要的頻率上,以控制電路性能呈現某種“八邊形法則”上的參數平衡。

本系統正是基于這種實際需求,設計了一個可以應用于電源管理等高頻應用中的外同步電路。雖然同步也可以使用常規鎖相環等精確的同步電路,但這一類的應用對于同步外部頻率可以不需要那么精確的頻率,因為芯片本身就可以是同步一個范圍的頻率,所以對于芯片內部的工作頻率不必那么精確。注意兩個易混淆的詞,一個是片間頻率需要準確相等,才用到同步單元;另一個是片內工作頻率則由于芯片工作特性,可以不需要非常精確的頻率。

二、具有記憶功能的同步系統的功能及架構

本系統設計有三個功能,這也是對于純同步單元或者是利用常規鎖相環進行鎖相同步所擁有的三個優勢:

(1)當外部沒有同步頻率時,電路自身能夠產生一個工作頻率,以供電源管理芯片系統使用。而常規鎖相環雖然內部也有振蕩電路,但更多的是用于鎖相外部頻率,當外部沒有加信號時,本身是不能提供一個穩定的工作頻率的[2]。對于純粹的同步單元也是如此。

(2)利用數字技術,實現對外部頻率的準確同步。相對于常規鎖相環所需要的鑒相器、濾波器、壓控振蕩器等復雜電路的設計[3],雖然系統不能對外部頻率實現像常規鎖相環那樣非常精確的鎖相同步,但是對于芯片工作來說誤差是可以接受的范圍,這就使得本系統對于實現外部同步的電路顯得簡單、實用。

(3)當系統加外部同步信號一段時間后,由于未知原因使得所加同步信號出現斷開或者短路,系統可以繼續維持工作在已經調整后的與之前所加外部頻率幾乎相等的頻率上(誤差5%以下,且可以繼續減小),這就是本系統的記憶功能。而普通同步單元或者是常規鎖相環則是在外部頻率存在時才同步或鎖相,而當斷開外部信號時,電路就將停止工作。記憶功能的存在,使得系統在外部電路產生一定錯誤后能夠繼續工作在原本所需的頻率上,使得系統的持續性、穩定性增強。

當然,本同步系統電路相對于常規鎖相環而言也有其缺點,一個是鎖定頻率不如常規鎖相環精確;另一個是沒有常規鎖相環那么大的鎖定范圍。但是,基于電源管理芯片的實際特性,這兩點都是可以忽略的。首先,對于片內工作頻率,芯片本身就是設定為一個可接受的范圍,所以與外同步頻率相比,很小的誤差幾乎不影響芯片的任何性能;其次,電源管理芯片一般工作在較高頻率,所以對于鎖相環的鎖定范圍從幾赫茲到幾百千赫茲或者是更高,完全沒有必要這么寬的鎖定范圍[4]。同時為了保證外圍電路和工作芯片本身的性能平衡,本系統也設計了一個頻率限制的單元,限定可以同步的頻率在350KHZ~770KHZ之間。而當未加同步信號時,系統自身振蕩工作頻率是560KHZ。

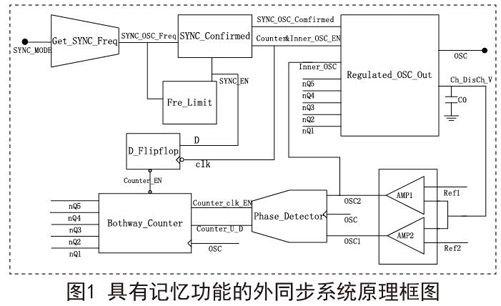

本系統的設計框圖如圖1所示:

圖1 具有記憶功能的外同步系統原理框圖

系統框圖所展現的原理是,若同步信號端SYNC_MODE沒有加同步信號,而只是接穩定的高電平或低電平,則整形取樣模塊的輸出SYNC_OSC_Freq單純為0;頻率限制模塊輸出SYNC_EN也為0;同步確認模塊SYNC_Comfirmed的輸出SYNC_OSC_Comfirmed為1,表示沒有外同步信號;使能信號Counter&Inner_OSC_EN為1,表示內部振蕩頻率可用,并且該信號經過D觸發器輸出一個計數器使能信號Counter_EN=1給雙向計數器模塊Bothway_Counter,表示計數器使不能。此時的計數器初始輸出值nQ5~nQ1是被內部的RS觸發器置定為01111,此五個信號接到調整頻率輸出模塊Regulator_OSC_Out中,作為五個給電容C0充電的電流源的開關控制端。01111,即表示只有nQ5控制的電流源是導通可充電的。并且nQ5~nQ1所控制五個電流源的電流值設置比例為16:8:4:2:1,以此來表示每次計數減少一位,只增加一個單位的總充電電流。因為放電電流設置為一個固定的較大值,所以總充電電流的大小在一定程度上可以表示頻率的快慢。電容C0上的鋸齒波輸出電壓Ch_DisCh_V信號接到比較器[5]的輸入端,與所加的偏置電壓進行比較后輸出一個方波脈沖OSC2,然后經過Regulated_OSC_Out模塊中的調整形成一個負反饋而輸出最終脈沖OSC。

當有加外同步信號時,如果信號是在頻率限制范圍內,那么頻率限制模塊輸出SYNC_EN將為1,表示可以同步。同步確認模塊SYNC_Comfirmed會用四個周期來確認是否是真實的有加外同步信號,而不是一時的噪聲或者是其他影響,若四個周期后確認了是有加同步信號,則SYNC_Comfirmed模塊將輸出經過整形和取樣的外同步信號,即為SYNC_OSC_Comfirmed確認同步信號。并且使能信號Counter&Inner_OSC_EN變為0,意味著內部頻率將被屏蔽。在確認是否同步的四個周期內,電路還是按照原本的內部振蕩頻率進行工作。而在四個周期之后,電路同步工作只是利用Regulated_OSC_Out模塊中幾個簡單的數字門電路來屏蔽之前的內部振蕩頻率,轉而將外同步頻率確認信號SYNC_OSC_Comfirmed輸出到最終的OSC輸出端。

由于SYNC_EN變為1,且Counter&Inner_OSC_EN信號變為0,D觸發器觸發使得雙向計數器的使能信號Counter_En變為0,使得雙向計數器[6]可以工作。Counter_EN為0,表示計數器內部的RS_D觸發器中的R、S兩端同時都為0,輸出nQ5~nQ1將可以隨著振蕩周期而計數(但是此時的計數器啟動信號Counter_clk_EN還沒確定狀態,這留待下文討論)。值得注意的是,屏蔽掉內部信號,只是屏蔽掉內部振蕩頻率在Regulated_OSC_Out模塊中對最終輸出OSC的影響,但是內部振蕩頻率還是會根據計數器對五個給C0充電的電流源的開關狀態來調整頻率,使之不斷與外部所加的信號頻率相等。正是由于內部振蕩頻率會調整等于外部同步頻率值,并且系統將重新使用內部振蕩頻率,才使得系統能夠在外同步信號斷開之后繼續工作在原來的頻率上。這就是上述所提到的系統化記憶功能。

由圖1可知,電容上的電壓Ch_DisCh_V信號與兩個輸出極性相反的比較器相連。其中比較器AMP1的比較門檻值設置的會比AMP2大一點,并且當電容電壓大于比較器AMP1的門檻值Ref1時,輸出OSC1將變低;相反,當電容電壓大于比較器AMP2的門檻值時,輸出OSC2將變高。輸出的兩個振蕩信號OSC1和OSC2進入到鑒相器進行鑒相以決定計數器是實現加法或者是減法的功能。

三、鑒相器模塊

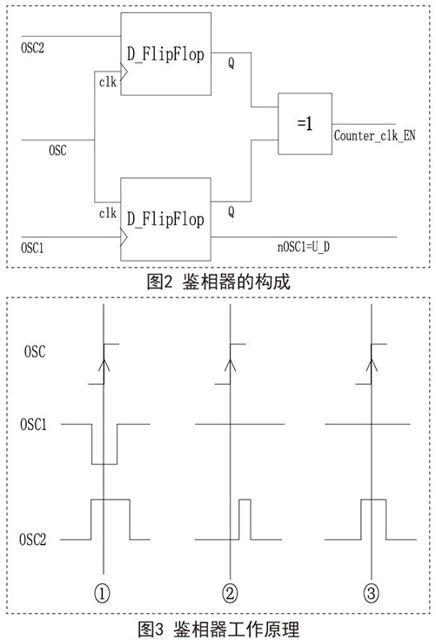

系統中設置了一個鑒相器,其架構和工作原理分別如圖2和圖3所示。

圖2 鑒相器的構成

圖3 鑒相器工作原理

由圖2可以知道鑒相器由兩個上升沿D觸發器和一個異或門構成,D觸發器的觸發時鐘邊沿是最終輸出的頻率OSC。值得注意的是,此時的同步過程,實際上跟其余模塊,比如計數器、鑒相器和比較器,甚至是調整輸出模塊中的五個充電電流源都無關。此時的同步,只是在Regulated_OSC_Out模塊中,簡單的利用幾個數字門電路,將從確認模塊來的SYNC_OSC_Comfirmed外同步信號直接調整輸出。而鑒相器利用此時的輸出同步頻率對OSC1和OSC2進行取樣和比較,其實就是一個外部頻率和內部頻率比較的過程。在OSC上升沿時,對OSC1和OSC2進行比較,當是圖3第一種情況時,采樣得到OSC1和OSC2為0、1,表示此時在所給的同步信號的一個周期內,電容C0的充電電流過大,導致電容C0上的電壓升到很大的值。異或門得到的計數器計數使能信號Counter_clk_EN為1,表示計數器模塊開始計數,而得到的U_D=nOSC1=1,對于nQ5~nQ1而言,表示計數器進行加計數,這樣就會控制給C0的總充電電流減小,從而可以知道內部振蕩頻率減小,以逐漸向外同步頻率靠近。

而若是采樣到的OSC1和OSC2是圖3中的第二種情況,為1、0,則表示在所給的同步信號的一個周期內,電容C0的充電電流過小,幾乎都不足以讓兩個比較器的輸出翻轉。異或門同樣得到Counter_clk_EN為1,計數器開始計數,而此時的U_D為0,表示計數器進行減計數,如此控制給電容C0的總充電電流增大,使得內部振蕩頻率增大,以逐漸趨向外部同步頻率。當經歷幾個周期的調整后,內部振蕩頻率幾乎等于外部同步頻率時,OSC對OSC1和OSC2的采樣才會出現第三種情況,表示內部振蕩頻率已經調整完畢,即對外部同步信號的頻率記憶完畢,隨時可以為系統提供持續性的與所加同步信號頻率大小相等的振蕩頻率。

顯然,這里是不可能出現采樣的OSC1和OSC2同時為0的情況,因為上述提過這兩個比較器對于同樣的輸入比較值,輸出的極性是相反的。只有當電容C0上的電壓大于AMP1的比較電壓Ref1,時,AMP1才將輸出0,而由于AMP2的比較電壓Ref2的值比Ref1小,所以如果AMP1翻轉,則AMP2必將翻轉,得到OSC2為1,這就變成了圖3中的第一種情況。所以,不會出現在采樣時,OSC1和OSC2為0、0的情況。

四、系統中的頻率限制模塊

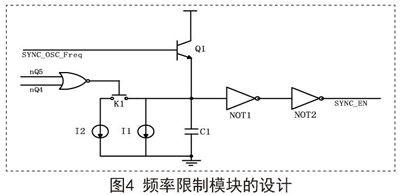

上文提過本系統主要是為高頻上的應用而設計,比如電源管理中的DC/DC應用。針對于此,系統設計了一個頻率限制的模塊用來限制同步的頻率,以滿足實際應用中對于芯片外圍元器件和芯片性能的要求。頻率限制的原理如圖4所示。

圖4 頻率限制模塊的設計

由于不管外同步信號的占空比是多大,經過整形和取樣模塊后,得到SYNC_OSC_Freq信號都只是一個占空比很小的窄脈沖。在脈沖為高電平時,晶體管Q1將導通,Q1作為一個大電流源在一瞬間將電容C1充至高電平,使得輸出同步使能信號SYNC_EN為1。對于頻率較低時,外同步信號的一個周期內除了窄脈沖為高電平時,其他更多的時間Q1是處于關閉狀態,這時電容將通過電流源I1進行放電(注意,圖中I1是處于常開狀態,而電流源I2是處于常閉狀態的)。在設置好合適的放電電流和電容大小后,可以保證在一個周期內,電容C1上的電壓值不會下降到反相器NOT1的翻轉門檻值,這樣就能保證同步使能信號SYNC_EN一直維持在高電平。由上述可知,此時系統的后續電路就將進行同步的一系列操作;而若超過了一定周期,這就意味著C1將會放電更久,C1上的電壓值就會而下降到使反相器NOT1翻轉的值,如此同步使能信號SYNC_EN就無法輸出持續為1,這表示電路無法對此外同步信號進行同步。這時候的電路是工作在上面分析過的第一種狀態,即系統產生的振蕩頻率是自身的振蕩頻率,為560KHZ。

高頻限制的原理跟低頻限制差不多,不同的是當SYNC_MODE端加高頻外同步信號時,在信號的前幾個周期,電路會依照前面所介紹的原理對外補信號進行同步。并且系統會通過調整計數器的輸出nQ5~nQ1,使內部振蕩頻率的大小趨向于外同步頻率。由于外同步頻率過高,系統在調整過程中,計數器的輸出nQ5~nQ1已經達到00111,而系統的內部振蕩頻率還未達到與外同步頻率一致。這時,由于nQ5和nQ4同時為0,圖4中電流源I2也將因為開關K1的導通而起作用,所以C1變成將通過I1和I2兩個電流源放電。在設置好適當的I2放電電流大小后,電容C1上的高電平原來不能降到NOT1的翻轉值,現在在同樣的周期內可以放電到致使反相器NOT1翻轉的門檻值,外同步信號SYNC_EN將不再保持為高電平。這也就意味著系統不再對外同步頻率進行同步。此時的系統是工作在內部振蕩頻率上,其值等于頻率限制的最高值上,本系統將其設置為770KHZ。