基于CPCI總線的數(shù)字板邊掃設(shè)計(jì)?

(中國(guó)電子科技集團(tuán)公司第三十八研究所,安徽合肥230088)

0 引言

數(shù)字化雷達(dá)系統(tǒng)是雷達(dá)發(fā)展的主要方向之一,發(fā)射和接收數(shù)字波束形成(DBF)技術(shù)是數(shù)字化雷達(dá)的關(guān)鍵[1],利用先進(jìn)的FPGA和DSP設(shè)計(jì)的實(shí)時(shí)數(shù)字多波束形成電路板,其集成度、復(fù)雜度、故障排查難度都遠(yuǎn)遠(yuǎn)高于常規(guī)數(shù)字電路板。隨著集成電路的發(fā)展,先進(jìn)的FPGA和DSP都支持IEEE 1149.1邊界掃描設(shè)計(jì)標(biāo)準(zhǔn)[2]。邊界掃描技術(shù)是針對(duì)數(shù)字多波束形成電路板等此類復(fù)雜電路板的有效測(cè)試手段,在行業(yè)內(nèi)可測(cè)性設(shè)計(jì)(DFT)[3]規(guī)范逐漸成型的情況下,該技術(shù)所具有的低廉成本和高效測(cè)試準(zhǔn)確率等優(yōu)勢(shì),得到了更好更充分的展現(xiàn)。

CPCI是臺(tái)式機(jī)外圍組件互連接口規(guī)范(PCI)的改版,因?yàn)樵诠I(yè)應(yīng)用和/或嵌入式應(yīng)用中,需要更強(qiáng)壯的機(jī)械結(jié)構(gòu),所以產(chǎn)生了CPCI這種緊湊型PCI的接口規(guī)范,而且CPCI和PCI有很好的電氣兼容性,使得復(fù)雜的CPCI系統(tǒng)中也能使用低成本的PCI組件[4]。CPCI使用工業(yè)級(jí)的機(jī)械組件和高性能的連接頭,能夠用于復(fù)雜的系統(tǒng)應(yīng)用,在本文探討的邊掃測(cè)試程序集(Test Project Set,TPS)設(shè)計(jì)的某數(shù)字板中,CPCI接口被用于進(jìn)行系統(tǒng)連接和數(shù)據(jù)傳輸。

1 可測(cè)試性分析

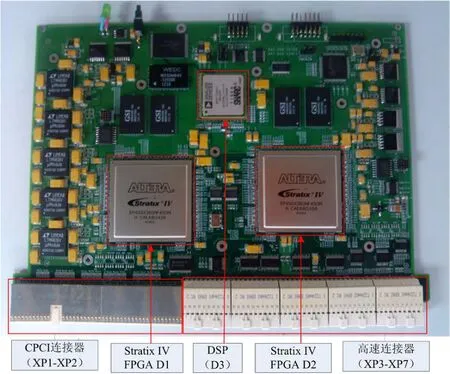

由于需要適應(yīng)大陣面的波束形成,系統(tǒng)某數(shù)字板上設(shè)計(jì)了兩片F(xiàn)PGA(EP4SGX360K)和一片DSP(TS201)處理器,用來(lái)完成收發(fā)校正、接收波束加權(quán)計(jì)算以及發(fā)射波束控制信息的計(jì)算[5]。其實(shí)物圖如圖1所示。

圖1 電路板實(shí)物圖

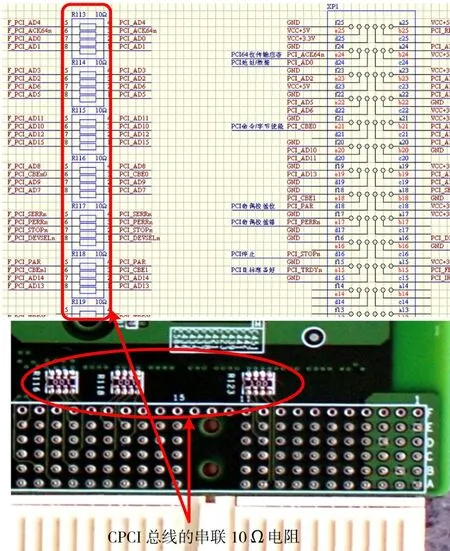

在信號(hào)接口上所有的PCI總線信號(hào)在CPCI板卡的連接頭處都要有一個(gè)10Ω的端接電阻[6]。端接電阻可以減小每塊板卡對(duì)PCI背板的影響,電阻設(shè)置在信號(hào)連接器引腳的15.2 mm(0.6英寸)內(nèi)。由于串聯(lián)的10Ω匹配電阻在該板上通過(guò)排阻的形式,分布在接口附近,尺寸極小,很容易出現(xiàn)焊接故障,如圖2所示。如果出現(xiàn)故障則會(huì)導(dǎo)致計(jì)算機(jī)無(wú)法識(shí)別該插件的ID號(hào)或數(shù)據(jù)傳輸錯(cuò)誤,通過(guò)邊掃測(cè)試可以有效排除排阻故障。

圖2 CPCI總線的匹配電阻

邊界掃描測(cè)試可以通過(guò)邊界掃描單元的互聯(lián)進(jìn)行短路、開(kāi)路的測(cè)試,簡(jiǎn)稱為“互聯(lián)測(cè)試”。在測(cè)試TPS設(shè)計(jì)時(shí),要仔細(xì)分析被測(cè)電路板的互聯(lián)結(jié)構(gòu),例如該板的互聯(lián)結(jié)構(gòu)分析如下。

(1)FPGA與片外存儲(chǔ)器

每片F(xiàn)PGA外接兩片GS864436B-166I同步靜態(tài)存儲(chǔ)器,存儲(chǔ)器容量為9 MB,讀寫速度最大為166 MHz,119-pinBGA封裝,支持IEEE 1149.1 JTAG邊界掃描。

(2)FPGA與DSP

DSP與兩片F(xiàn)PGA之間通過(guò)32 bit地址、64 bit數(shù)據(jù)共享總線互連,總線數(shù)據(jù)率為60 MHz。另外,DSP與每一片F(xiàn)PGA之間還通過(guò)2路鏈路口方式互連,以彌補(bǔ)FPGA與DSP數(shù)據(jù)交換帶寬的不足,鏈路口最快可以達(dá)到480 MHz。

(3)FPGA與FPGA

為了保證兩片F(xiàn)PGA之間數(shù)據(jù)傳輸有足夠的帶寬,在兩片F(xiàn)PGA之間有8路高速接口,每路高速信號(hào)最高可達(dá)6 Gbit/s,另外還有79路LVDS接口,速度達(dá)到1.2 Gbit/s,除此之外還保留了85個(gè)TTL電平的備份總線,因此兩片F(xiàn)PGA之間的數(shù)據(jù)帶寬將近150 Gbit/s。

(4)時(shí)鐘管理芯片

時(shí)鐘管理芯片ispPAC-CLK5620AV-01T100I,通過(guò)FPGA控制可以在兩個(gè)輸入時(shí)鐘(外時(shí)鐘和本地晶振)之間自由切換。時(shí)鐘管理芯片有多個(gè)單端時(shí)鐘輸出管腳,內(nèi)部嵌入鎖相環(huán),通過(guò)軟件PAC-Designer可以方便地設(shè)置時(shí)鐘的分頻、倍頻、使能、相位,還可以獨(dú)立設(shè)置每個(gè)時(shí)鐘輸出的使能、終端匹配和抖動(dòng)等參數(shù)。時(shí)鐘芯片單獨(dú)構(gòu)成JTAG鏈路,支持邊界掃描測(cè)試。

2 邊界掃描測(cè)試設(shè)計(jì)

邊界掃描測(cè)試技術(shù)的基本思想是在靠近邊界掃描芯片(本文以FPGA為例)的輸入輸出管腳上增加一個(gè)移位寄存器單元。因?yàn)檫@些移位寄存器單元都分布在FPGA的邊界上(周圍),所以被稱為邊界掃描寄存器。當(dāng)FPGA處于調(diào)試狀態(tài)時(shí),這些邊界掃描寄存器可以將FPGA和外圍的輸入輸出隔離開(kāi)來(lái)。通過(guò)這些邊界掃描單元,可以實(shí)現(xiàn)對(duì)FPGA輸入輸出信號(hào)的觀察和控制。

該板由于使用的FPGA芯片、TS201芯片和DDR2芯片均是BGA封裝,且板卡設(shè)計(jì)集成度很高,采用邊界掃描測(cè)試是較為合適的方法。通過(guò)比較,本文選擇了ASSET公司的Scanworks工具作為邊界掃描的開(kāi)發(fā)工具。ASSET公司是一家專業(yè)從事邊界掃描技術(shù)開(kāi)發(fā)與研究的公司,它參與了IEEE 1149.1、IEEE 1149.4、IEEE 1532、IEEE 1149.6等有關(guān)JTAG標(biāo)準(zhǔn)的制定,其開(kāi)發(fā)的邊界掃描工具Scanworks在銷售市場(chǎng)的占有率第一,并且與摩托羅拉、諾基亞、思科、Aglient等知名公司有著長(zhǎng)期良好的深度合作關(guān)系,如Aglient公司研制的i3070,采用針床測(cè)試的同時(shí)嵌入了Scanworks作為邊界掃描測(cè)試的工具。

邊界掃描測(cè)試設(shè)計(jì),首先要對(duì)該板的JTAG鏈路結(jié)構(gòu)進(jìn)行分析。經(jīng)過(guò)鏈路分析后,提取鏈路相關(guān)的邊掃器件,去掉不相干的器件,這樣板卡的系統(tǒng)框圖變得很清晰,如圖3所示。圖中,板卡上的兩片Altera公司的FPGA(型號(hào)為EP4SGX360NF45I3)用跳線設(shè)置為串行鏈,可以通過(guò)遠(yuǎn)程加載口控制,1片ADI公司的DSP(TS201)單獨(dú)構(gòu)成一條鏈,通過(guò)面板上的加載口進(jìn)行控制。

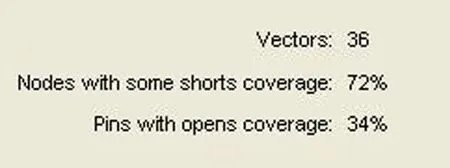

由于邊界掃描測(cè)試速率目前最高只有40 MHz,很難匹配該板數(shù)百兆的工作頻率,因此只能用于檢測(cè)板卡的硬件焊接連接性。高速電路涉及的信號(hào)網(wǎng)絡(luò)在該板中占了較少的一部分。通過(guò)網(wǎng)絡(luò)分析,該板共有網(wǎng)絡(luò)791個(gè),邊界掃描測(cè)試未能覆蓋的有222個(gè),占比28.1%,如圖4所示。

圖4 信號(hào)網(wǎng)絡(luò)故障覆蓋分析

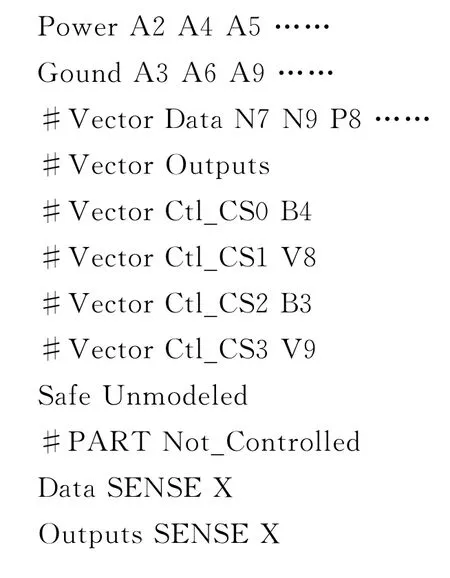

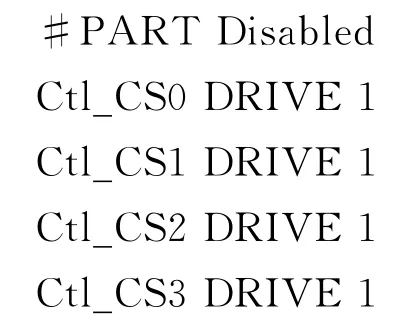

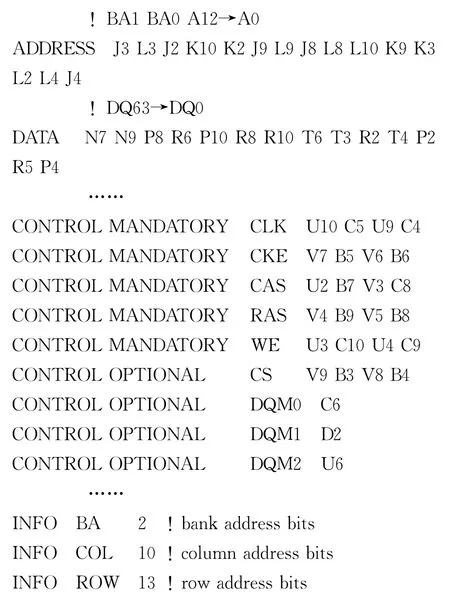

邊界掃描測(cè)試可以通過(guò)邊界掃描單元的互聯(lián)進(jìn)行短路、開(kāi)路的測(cè)試,也可以通過(guò)訪問(wèn)存儲(chǔ)器,對(duì)存儲(chǔ)器的地址、數(shù)據(jù)總線以及內(nèi)部存儲(chǔ)單元進(jìn)行測(cè)試,簡(jiǎn)稱為“存儲(chǔ)器測(cè)試”。在互聯(lián)測(cè)試時(shí),需要對(duì)不相關(guān)的器件進(jìn)行屏蔽,消除功能性的影響,這個(gè)時(shí)候就需要設(shè)計(jì)各種器件的模型,根據(jù)器件的要求給相關(guān)管腳施加“0”或“1”信號(hào),從而起到屏蔽的效果,例如針對(duì)該板的DDR2存儲(chǔ)器(型號(hào)為W332M64)設(shè)計(jì)模型如下:

在測(cè)試算法上可以有很多選擇,例如全“0”、全“1”,走步“0”和走步“1”,瓦格納算法等,全“0”、全“1”算法在測(cè)試準(zhǔn)確性上明顯不足,而走步“0”和走步“1”算法能有效排除短路、開(kāi)路故障,準(zhǔn)確度很高,但是在節(jié)點(diǎn)數(shù)量巨大、信號(hào)復(fù)雜的電路板上,走步算法顯得效率低下。瓦格納算法優(yōu)化了測(cè)試向量的種類,在保證覆蓋率達(dá)到99%以上的情況下,所需測(cè)試向量?jī)H為log2(2?n+1)個(gè),其中n為信號(hào)網(wǎng)絡(luò)的數(shù)量。例如1 000個(gè)信號(hào)網(wǎng)絡(luò)只需要11個(gè)測(cè)試向量,5 000個(gè)信號(hào)網(wǎng)絡(luò)只需要14個(gè)測(cè)試向量,大幅提高了測(cè)試效率,是一個(gè)較好的選擇。

互聯(lián)測(cè)試已經(jīng)能夠解決大部分的硬件故障,除了互聯(lián)測(cè)試之外,還進(jìn)行了專門的存儲(chǔ)器測(cè)試,以提高故障覆蓋率。存儲(chǔ)器測(cè)試也需要設(shè)計(jì)相應(yīng)的測(cè)試模型,仍以DDR2存儲(chǔ)器(型號(hào)為W332M64)為例,設(shè)計(jì)模型如下:

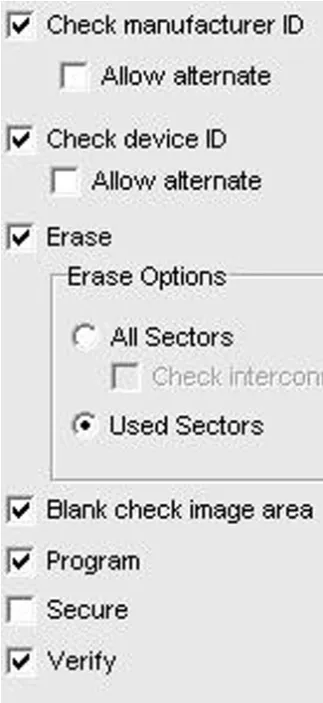

除了存儲(chǔ)器之外,FLASH也是一種專門的測(cè)試。FLASH測(cè)試時(shí)需要提供FLASH的協(xié)議,如讀寫序列、讀寫地址、ID號(hào)、單元大小等,邊界掃描測(cè)試可以對(duì)FLASH進(jìn)行擦除、寫入、加密、比較等一系列操作,如圖5所示。

圖5 FLASH操作

3 效果驗(yàn)證

經(jīng)過(guò)邊界掃描測(cè)試設(shè)計(jì),該板在互聯(lián)測(cè)試中短路故障覆蓋率達(dá)到72%,開(kāi)路覆蓋率達(dá)到34%,除了高速部分的信號(hào)網(wǎng)絡(luò)外,其余部分基本都覆蓋。經(jīng)過(guò)試用,該測(cè)試工程能夠在調(diào)試過(guò)程中發(fā)揮重要的作用,例如常見(jiàn)的小電阻虛焊、細(xì)間距芯片管腳粘連等肉眼難以發(fā)現(xiàn)的故障,基本都能定位并予以排除,這在一定程度上不僅挽救了這些動(dòng)輒數(shù)十萬(wàn)的昂貴電路板,也進(jìn)一步排除了故障隱患,提升了產(chǎn)品可靠性。波束形成板的邊界掃描測(cè)試故障覆蓋率參考圖如圖6所示。

圖6 互聯(lián)測(cè)試故障覆蓋率

4 結(jié)束語(yǔ)

數(shù)字電路板的可測(cè)試性設(shè)計(jì),尤其是對(duì)邊界掃描測(cè)試的支持很大程度上決定了該電路板的故障檢測(cè)率、可維護(hù)性和批量生產(chǎn)的能力。本文通過(guò)對(duì)某數(shù)字板的可測(cè)試性分析,以及對(duì)其采用的CPCI接口分析,并通過(guò)邊掃TPS的設(shè)計(jì),驗(yàn)證了其具備了良好的可測(cè)試性設(shè)計(jì),另外也給出了該板上某具有代表性的存儲(chǔ)器的模型,并對(duì)板上的FLASH進(jìn)行了測(cè)試開(kāi)發(fā)。綜合多種測(cè)試方法,其故障覆蓋率能有效滿足實(shí)際需求,對(duì)該板的維修、批量生產(chǎn)和保障都有重要的意義。

[1]朱子平,呂繼榮,洪一.數(shù)字波束形成在雷達(dá)中的應(yīng)用與分析[J].中國(guó)電子科學(xué)研究院學(xué)報(bào),2006,1(3):244-247,272.

[2]張峻.利用邊界掃描測(cè)試和SVT改善基于Haswell的電腦主板的測(cè)試覆蓋率[J].國(guó)外電子測(cè)量技術(shù),2014,33(1):17-21.

[3]朱振軍,林明,宋月麗.基于邊界掃描技術(shù)的板級(jí)測(cè)試分析[J].電子設(shè)計(jì)工程,2012,20(9):127-129,133.

[4]譚劍波,尤路,黃新,等.邊界掃描測(cè)試技術(shù)[M].北京:國(guó)防工業(yè)出版社,2013:5-10.

[5]鄔伯才,施晉生,孫龍,等.寬帶DBF SAR/MTI雷達(dá)典型工作模式設(shè)計(jì)[J].雷達(dá)科學(xué)與技術(shù),2014,12(1):20-28.WU Bo-cai,SHI Jin-sheng,SUN Long,et al.Typical Design of Operating Mode for Wideband Digital Array SAR/MTI Radar[J].Radar Science and Technology,2014,12(1):20-28.(in Chinese)

[6]宋秀芬,李宏,周偉.基于CPCI標(biāo)準(zhǔn)的6U信號(hào)處理平臺(tái)的設(shè)計(jì)[J].中國(guó)科技信息,2014(8):137-138.