基于FPGA的數(shù)字秒表設(shè)計(jì)

唐家博

摘 要:利用FPGA制作數(shù)字秒表,外圍電路簡(jiǎn)單,可靠性高,集成度高。本設(shè)計(jì)方法主要采用VerilogHDL語言進(jìn)行仿真與設(shè)計(jì),集成開發(fā)環(huán)境是Altera公司的quartusII。并把最終的結(jié)果用數(shù)碼管進(jìn)行顯示。

關(guān)鍵詞:FPGA;VerilogHDL;數(shù)字秒表;quartusII

1 引言

FPGA,全稱是Field-Programmable Gate Array,即現(xiàn)場(chǎng)可編程門陣列,顧名思義該芯片的內(nèi)部電路邏輯是不確定的,可以通過軟件進(jìn)行編程,這與傳統(tǒng)的cpu、mcu等存在著明顯的差異,而后者的內(nèi)部電路邏輯是確定的。對(duì)FPGA的編程也與普通的軟件編程是不一樣的,對(duì)FPGA的編程實(shí)際上是對(duì)FPGA內(nèi)部的電路邏輯進(jìn)行編程,也就是所謂的HDL(hardware description language),即硬件描述語言。

目前主流的HDL包括VHDL與VerilogHDL,使用更為廣泛的是VerilogHDL,在開發(fā)者中占80%左右的份額,而本文也將以VerilogHDL為例,介紹利用該硬件描述語言來實(shí)現(xiàn)數(shù)字秒表的設(shè)計(jì)。

2 設(shè)計(jì)要求與目標(biāo)

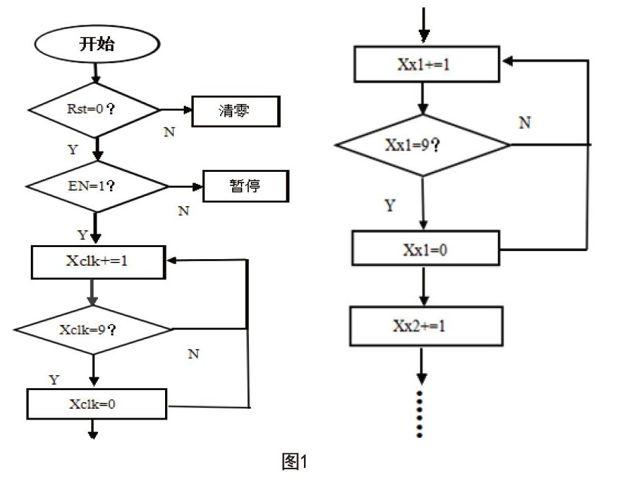

a、能夠從0.00秒一直計(jì)時(shí)到59.99秒

b、精度要求是10ms

c、設(shè)有清零鍵,能夠一鍵清零

d、設(shè)有使能鍵,能夠提供計(jì)時(shí)暫停功能

3 硬件系統(tǒng)的搭建

時(shí)鐘信號(hào):由于數(shù)字秒表對(duì)時(shí)間精度的要求度高,所以我們采用晶體振蕩器來提供時(shí)鐘信號(hào),晶體振蕩器具有頻率穩(wěn)定、受外界影響小等特點(diǎn)。我們可以通過利用數(shù)字電路元件對(duì)晶體振蕩器進(jìn)行分頻,并得到一個(gè)1MHz的時(shí)鐘信號(hào),并利用該時(shí)鐘信號(hào)進(jìn)行后面的設(shè)計(jì)。

譯碼與顯示:我們利用譯碼器進(jìn)行譯碼,通過數(shù)碼管進(jìn)行顯示。其中譯碼管我們采用74HC164顯示譯碼管。由于每個(gè)數(shù)碼管要顯示的數(shù)字從0開始最大到9為止,所以我們輸出信號(hào)的位寬設(shè)計(jì)為4位即可。

使能鍵與清零鍵:為提高系統(tǒng)的可靠性,我們采用電平觸發(fā)的按鍵,并且我們采用異步使能與異步清零的方式,并且清零端的優(yōu)先級(jí)要高于使能端的優(yōu)先級(jí)。

計(jì)時(shí)與計(jì)數(shù)功能:這部分是整個(gè)秒表的核心部分,將通過對(duì)FPGA的編程來實(shí)現(xiàn)。芯片采用altera公司的Cyclone系列,該系列的芯片價(jià)格適中,足以實(shí)現(xiàn)秒表系統(tǒng)的設(shè)計(jì)。

5 結(jié)語

本數(shù)字秒表的實(shí)現(xiàn)主要是利用文本輸入來完成,通過VerilogHDL設(shè)計(jì)若干10進(jìn)制計(jì)數(shù)器和6進(jìn)制計(jì)數(shù)器來完成對(duì)時(shí)鐘信號(hào)的計(jì)數(shù)和計(jì)時(shí)的功能,然后通過譯碼管進(jìn)行譯碼并最終用數(shù)碼管顯示出來。由于本設(shè)計(jì)方法中采用晶體振蕩器,震蕩頻率穩(wěn)定,所以計(jì)時(shí)精確,可靠性高。

參考文獻(xiàn)

[1]潘松 黃繼業(yè) 潘明 《EDA技術(shù)實(shí)用教程》第四版 科學(xué)出版社 2010

[2]周立功 《EDA實(shí)驗(yàn)與實(shí)踐》 北京航天航空大學(xué)出版社 2007