基于多通道技術的數字收發單元設計

秦 穎,謝書珊

(南京電子技術研究所, 南京210039)

0 引言

數字陣列雷達是近年來隨著數字技術發展出現的一種新體制相控陣雷達,其特點是每個收發通道都由數字方式完成。該體制雷達具有靈活的波形、波束變化能力,并應用先進處理方法優化對目標的跟蹤質量,提高了時間、能量、資源的利用效率,賦予雷達更好的反隱身性能[1]。

隨著數模混合集成技術的飛速發展,模數轉化器(ADC)采樣率和直接數字頻率合成(DDS)輸出頻率均不斷提高,數模信號的轉換越來越靠近天線,數字信號處理已完全實現軟件化,這些均意味著數字陣雷達將逐漸向全數字化邁進。同時,數字陣雷達具有通道數量多、設備量大、調試復雜等特點,其系統的集成度、經濟性、可靠性也是設計過程中需要考慮的問題。

1 數字收發單元設計原理及關鍵技術

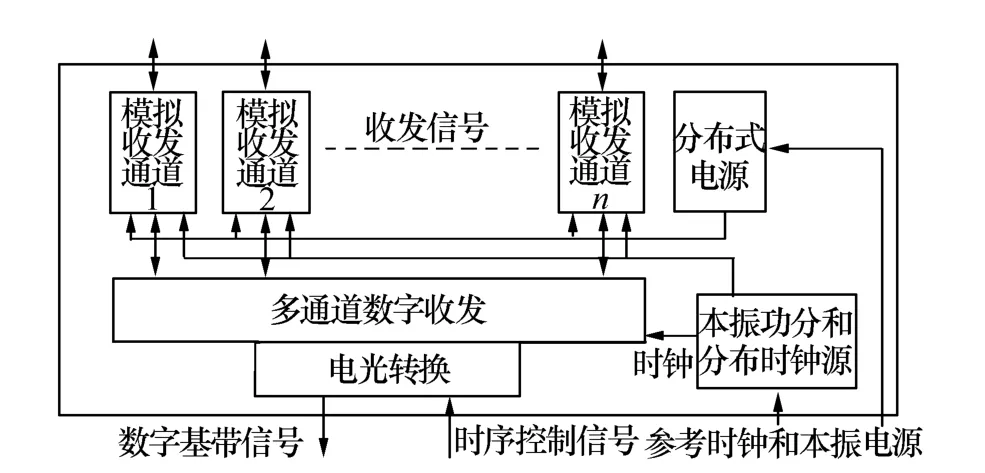

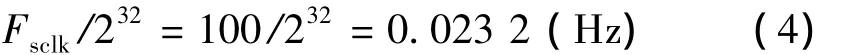

本文介紹了基于多通道技術的數字收發單元設計原理及關鍵技術,其功能框圖見圖1。

圖1 數字收發單元原理框圖

數字收發單元位于數字陣雷達的天線陣面上,是整部雷達的關鍵部件。發射時,數字收發單元接收頻率源產生的本振信號和時鐘信號,并分配給每個通道;系統根據雷控指令計算出每個組件中各通道對應的控制碼,通道中的DDS根據控制碼產生雷達工作的波形信號,再通過選頻、濾波、混頻、放大等模擬處理后,產生所需頻率的激勵信號。接收時,雷達回波信號由模擬電路處理為中頻信號,經數字中頻采樣產生并行數字信號,重組、打包后由光纖送到后端的數字波束形成(DBF)繼續進行信號數據處理[2]。

2 基于多路集成ADC的數字接收技術

數字中頻采樣是基于高分辨率的ADC芯片完成從模擬信號到基帶信號的一種數字正交下變頻技術,同時通過軟件編程靈活地實現各種數字下變頻器、數字濾波、信道均衡等功能,通過加載新的軟件模塊即可實現模式切換。這種以軟件為核心的處理方式極大地提高了系統靈活性,也有效降低了硬件成本。

理想的中頻采樣是要利用高速ADC芯片和高性能可編程處理器,使采樣頻率盡量接近激勵信號頻率,在盡量寬的帶寬上完成模/數(A/D)變換并送入現場可編程門陣列(FPGA)進行處理。由于A/D變換后的處理均通過軟件實現,從而給系統帶來了巨大的靈活性,這是以往模擬電路處理方式所無法比擬的。因此,數字中頻采樣具有可編程、可重配置、開放性和穩定性好等諸多優點,但現階段工程實踐中會受到模擬信號的輸入頻率、帶寬,以及實時的數字信號處理能力的限制。因此,實際工程設計時通常在數字中頻采樣前先進行少量模擬變頻、濾波等處理[3],本設計也將采用此處理方式。

以往的設計中,每路模擬接收通道都對應一個單獨的ADC器件,每個ADC的時鐘及其輸出信號都需要謹慎處理,這給通道數量龐大的數字陣雷達帶來巨大的工作量。近年來,針對高性能、多功能、低成本、小尺寸的應用,各芯片廠商都推出了多款多通道集成的ADC芯片,本文采用的是ADI公司出品的雙通道集成的AD9268。該芯片可同步采集2路模擬信號,轉換精度16位,最高采樣率105 MS/s。

根據帶通采樣定理,ADC采樣率只取決于信號的載波頻率和帶寬。對于數字陣雷達來說,多通道的同步性能和一致性能非常關鍵,因此,ADC采樣時鐘頻率應低于信號載波頻率。針對本文信號載波頻率130 MHz和帶寬5 MHz,綜合考慮多個數字收發單元的同步要求和可實現方式,系統的時鐘選擇為100 MHz。

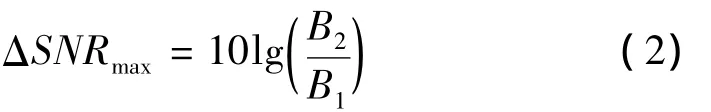

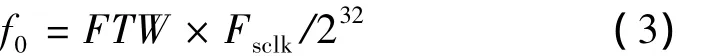

理論上,中頻采樣模塊(ADC+數字下變頻(DDC))可以得到的信噪比(SNR)按下式計算

式中:fs為采樣頻率;b為A/D轉換位數;B為輸入模擬信號帶寬。SNRmax一般由實驗測試結果進行標定。輸入信號的帶寬由 B1變化為 B2時,所能取得的SNRmax也隨之變化。

器件資料中,該芯片的動態指標在輸入中頻999 MHz、采樣時鐘100 MHz時,SNR=64.7 dB。5 MHz信號帶寬時,還能得到10 dB的處理得益(10lg(fs/2B)=10lg(100/2×5)=10 dB),中頻數字正交處理(ADC+DDC)的輸出動態最大可達74.7 dB,滿足系統所要求的動態范圍。

中頻模擬信號在中放放大后通過匹配濾波器去除帶外雜波信號,再經單端-差分處理后送入ADC,被時鐘采樣后轉換為數字信號,送入FPGA進行DDC處理,如圖2所示。首先,用全局時鐘鎖存16位AD數據;然后,與數控振蕩器(NCO)產生的數控I/Q正交本振信號混頻,經積分梳狀濾波器(CIC)完成抗混疊(去鏡像)和抽取降速;再針對不同的數據率,采用對應的有限脈沖響應(FIR)低通濾波器進行匹配抽取和數據位截取,輸出16位的并行數據;最后,通過數據緩存、重組轉換為高速串行信號,由光纖送到后端的DBF繼續進行信號數據處理。

圖2 A/D采樣的處理流程圖

我們對偏離載頻0.125 MHz的點頻信號對ADC和整個DDC通道進行了數據錄取和分析,圖3顯示了DDC基帶信號快速傅里葉變換(FFT)分析的結果。由圖可見,FFT分析出的ADC有效位數13.1位,滿足系統需求,無雜散動態范圍(SFDR)、諧波抑制度、鏡像抑制度等指標也很理想。

圖3 DDC處理后的基帶數據FFT分析

由于ADC器件的非線性特性,實際噪聲功率通常會比理論的量化噪聲功率高,尤其在單元電磁兼容環境不理想時,會影響收發通道的噪聲系數[4]。同時,高性能的ADC是非常敏感的器件,其自身也會被環境中的雜散信號影響。因此,如何保證信號的完整性,對模擬、數字電源隔離和濾波時數字地與模擬地應該如何劃分,對參考時鐘的處理等都是數模集成系統設計中不可忽視的問題。

3 多通道信號產生技術

DDS是目前廣泛應用于電子領域的全數字結構新型信號產生技術。與模擬頻率合成技術相比,DDS具有靈活性高、分辨率高及頻率轉換時間超高速等突出優點,在雷達應用中能更快捷、更靈活地控制發射波形轉換和波束掃描,更簡單方便地實現各通道間的幅相一致性[5]。隨著數字芯片技術的發展,多路集成DDS技術日趨成熟,應用單芯片產生多路輸出信號,可極大簡化電路設計和印制電路板布局布線,降低組件的復雜度、體積和成本。

針對實例系統中采樣時鐘100 MHz、中頻130 MHz、帶寬5 MHz的多路調頻、調相信號,本方案選用的DDS芯片型號為AD9959。它是一款各通道獨立受控,能產生4路不同輸出信號的多通道集成DDS芯片,最高工作頻率可達500 MHz。

DDS輸出頻率為

式中:FTW為頻率控制字,且0≤FTW≤231;Fsclk為時鐘頻率。

DDS輸出頻率分辨率為

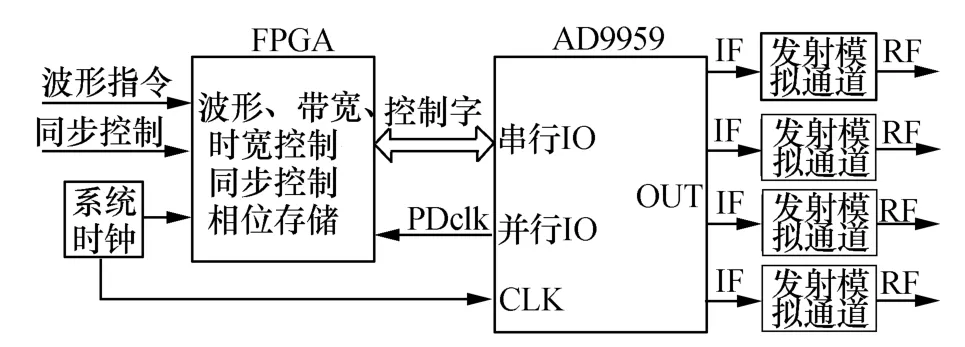

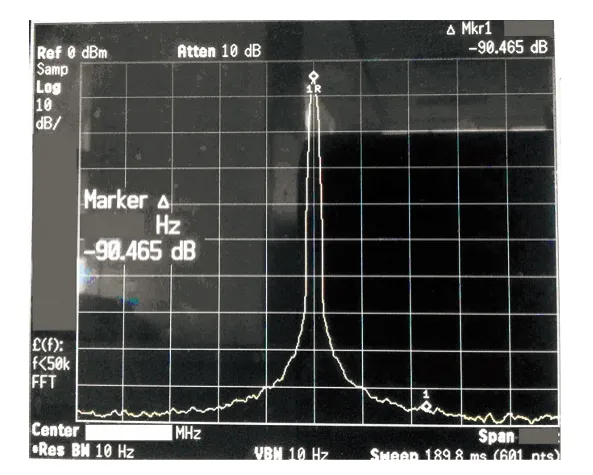

由此可見,僅用1片AD9959芯片,就能在小型化數字收發組件中同時產生4路獨立可控的中頻輸出信號,系統結構框圖如圖4所示。雷達工作中,FPGA根據雷控指令計算出各通道所需的波形碼、頻率字、相位字、幅度字等,控制AD9959產生多路雷達中頻信號。圖5和圖6即為其中一個通道的輸出信號在頻域的測試結果。

圖4 信號產生系統結構框圖

圖5 LFM信號頻譜圖

圖6 LFM信號脈內頻譜圖

AD9959的寄存器采用串口方式進行配置,具體有1線操作、2線操作和4線操作的配置方式,如圖7所示。采用1線操作方式時,數據線僅有一根,能有效避免數據線間相互干擾,此系統中采用該方式配置芯片內部寄存器。對AD9959的控制流程如下:在各通道初始化后,先配置通用寄存器激活想要配置的DDS通道,再根據通道寄存器列表的地址對各寄存器進行配置。進行多路DDS操作時,同一個地址和值可同時寫入共用的寄存器地址內,控制4路DDS輸出相同信號。也可以通過設置通道使能位分別向每個通道寫入不同的數據,獨立控制不同通道DDS輸出[6]。

圖7 多路信號產生軟件處理流程圖

DDS技術的發展為頻率合成系統帶來了極大的便利,但是器件固有的非線性使得產生輸出信號的同時也會產生大量的雜散。因此,必須分析并解決DDS對系統噪聲和雜散的影響。

1)DDS芯片內部集成了時鐘倍頻器,可以將較低頻率的參考時鐘倍頻到高頻的工作時鐘,但是信號倍頻M次后相位噪聲就會惡化20lgM。因此,應該盡量放棄使用倍頻器,而直接采用高頻譜純度的參考時鐘作為DDS的系統時鐘;

2)在合成信號的頻率較高時,為了實現良好的SFDR指標,DDS輸出的差分信號應當采用等終端匹配的方式連接;

3)DDS輸出頻率分辨率取決于時鐘頻率和相位累加器位數。因此,一般相位累加器位數N會盡可能做大,但實際波形存儲器的容量卻有限,用來尋址的位數通常小于N,尋址時相位累加器的低B位就被截去,此時產生的相位舍位誤差就會帶來大量雜散。如果使B=0,則可以避免出現此類雜散,從而提高輸出信號質量。所以,在DDS輸出點頻信號時,應盡量使頻點設計在能被時鐘整除的頻率。

4 多通道同步技術

在數字相控陣雷達中,多通道之間的同步十分關鍵,它是目前所研究的難點和熱點之一。對數字陣雷達系統而言,同步分為收發單元之間的同步和單元內通道間的同步。數字收發單元中的各功能模塊通常采用同一基準時鐘觸發,從而保證各通道在相位和時序上的一致性,這些通道間的同步就屬于單元內同步;而若干個獨立的數字收發單元間的同步則屬于單元間同步。因此,如何調整系統時鐘與控制邏輯之間的相對觸發關系是雷達設計中必須解決的問題。

對于本方案100 MS/s的時鐘系統,要保證上行DDS和下行ADC的多通道同步,同步精度需達到ns級,則必須嚴格控制各路采樣時鐘之間的延遲差異。在電路、系統、軟件設計上,我們多方面綜合考慮了同步性,主要措施有:

(1)電路設計。單元內部各通道對觸發脈沖的同步響應直接影響上行信號相位控制的穩定性、下行信號采樣時刻的一致性,對時鐘(FPGA時鐘、DDS系統時鐘、ADC采樣時鐘)和定時脈沖的硬件通路必須控制等長、減小延遲,并盡量減少相位隨環境溫度的器件(比如模擬濾波器等);

(2)系統設計。多通道信號產生、信號采樣的同步性最基本的條件是收發單元同時響應觸發脈沖,數字陣雷達各組件的定時脈沖是同一個信號,而時鐘是同源、同頻、相參的,所以系統必須保證時鐘、定時脈沖到各單元的相位延遲盡可能相同,也就是盡量等距離傳輸;

(3)軟件設計。在硬件上是很難做到多路高速時鐘完全同步的,而FPGA的軟件化、數字化處理,使得我們可以靈活地控制FPGA內部的時鐘相位,從而改變了DDS、DDC的控制碼與同步脈沖之間的時序關系,完善系統的同步設計。

5 結束語

本文基于多通道ADC、DDS和多通道同步技術,通過集成、高效的設計方案,完成數字收發單元的原理分析和電路集約化設計,對設計中的要點、難點及主要參數進行了簡要闡述,為數字收發單元中的關鍵技術突破提供了可靠的工程實踐支撐。

數字陣雷達是當前雷達技術的前沿,而多通道技術的發展是其最大的推動力之一。近年來,隨著高速數字器件的發展,射頻直接采樣和DDS產生射頻信號技術日趨成熟,通道中模擬處理部分逐漸消失。再加上射頻集成芯片和系統級芯片的出現,數字收發單元逐漸向芯片化、小型化、低成本、高可靠性方向發展,數字陣雷達也正向著全數字化的方向邁進。

[1]陳文英,陳 玲.海用雷達技術及其進展[J].艦船電子對抗,2008,31(4):25-28,31.Chen Wenying,Chen Ling.Marine radar technology and its progress[J].Shipboard Electronic Countermeasure,2008,31(4):25-28,31.

[2]蘇力爭,鐘劍鋒,張建增,等.S波段八通道數字T/R組件研究與設計[J].現代雷達,2013,35(9):66-68,72.Su Lizheng,Zhong Jianfeng,Zhang Jianzeng,et al.Study and design of eight-channel digital T/R module at S band[J].Modern Radar,2013,35(9):66-68,72.

[3]白 晶,陳 翔.米波段數字接收機的設計[J].現代雷達,2005,27(8):71-73.Bai Jing,Chen Xiang.Design for metre wave band digital receiver[J].Modern Radar,2005,27(8):71-73.

[4]張志強,阮黎婷,倪 濤,等.ADC模數轉換器有效位計算[J].電子科技,2010,23(3):84-85,110.Zhang Zhiqiang,Ruan Liting,Ni Tao,et al.Calculation of effective numbers of bits for the analog-to-digital converter[J].Electronic Science and Technology,2010,23(3):84-85,110.

[5]張德平,王 超,袁乃昌.基于DDS陣列的發射數字波束形成系統設計[J].現代防御技術,2011,39(1):126-128.Zhang Deping,Wang Chao,Yuan Naichang.Design of transmit digital beam-forming system based on DDS array[J].Modern Defence Technology,2011,39(1):126-128.

[6]陳 菡,譚劍美,吳 兵.應用于數字陣列的多通道波形產生系統設計[J].現代電子技術,2012,35(9):19-21,24.Chen Han,Tan Jianmei,Wu Bing.Design of multi-channel waveform generation system applied in DAR[J].Modern E-lectronic Technique,2012,35(9):19-21,24.