寄生電感對Buck變換器中SiC MOSFET開關特性的影響

范春麗, 趙朝會, 余成龍, 龍覺敏

(上海電機學院 電氣學院, 上海 200240)

?

寄生電感對Buck變換器中SiC MOSFET開關特性的影響

范春麗,趙朝會,余成龍,龍覺敏

(上海電機學院 電氣學院, 上海 200240)

摘要:為了研究高開關速度下寄生電感對SiC MOSFET開關特性的影響,以Buck變換器為例,依據電力電子技術的基本理論,借助于Saber軟件,分析了漏極寄生電感Ld和源極寄生電感Ls對Buck變換器中SiC MOSFET開關特性的影響。仿真結果表明,隨著寄生電感的增大,SiC MOSFET的電壓應力加大,開關損耗增加。

關鍵詞:碳化硅;金屬氧化物半導體均效應晶體管; Buck變換器; 寄生電感; 開關特性

隨著能源問題的日益凸顯,應用場合對電力電子變換器的要求朝著高頻率、高效率、高功率密度的方向發展。作為傳統電力電子變換器開關器件的硅(Si)器件經過幾十年的長足發展,性能接近其理論極限,已難以取得大幅度提升[1-2]。自20世紀90年代起,一種新型半導體材料碳化硅(SiC)以其優良的性能逐漸受到人們的關注。與Si材料相比,SiC材料具有禁帶寬度高(3.0eV)、飽和電子漂移速度高(200km/s)、臨界電場擊穿強度高(2.4MV/cm)、導通電阻低(1mΩ/cm2)和熱導率高(3.3~4.9W/(cm·K))等特征[3-8],為高性能的功率變換器的發展提供了條件。

然而,隨著開關速度的提高,在低頻下可以忽略的某些寄生參數,如印制電路板(Printed Circuit Board, PCB)布線和器件封裝的寄生電感會與SiC MOSFET的寄生電容一起產生劇烈振蕩[9],給開關器件帶來過高的電壓、電流應力,嚴重時可損壞器件,使變換器不能正常工作。高開關速度雖然降低了器件的開關損耗,但也帶來了惡化器件應力和電磁干擾(Electromagnetic Interference, EMI)問題[9-10],因而,有必要對高開關速度下寄生電感對器件開關特性的影響進行研究。雖然寄生電感對單極性功率器件的影響是一個普遍性問題,但由于SiC MOSFET的開啟電壓較低,且負溫度系數較大,使得柵極對噪聲電壓的抗擾能力降低,更容易受到由電路中寄生電感引起的電壓振蕩的影響。

近年來,為了更加深入地探究寄生電感對功率器件開關特性的影響,國內外一些學者做了一些研究。文獻[9]中針對并聯型常閉SiC JEFT的均流問題,在并聯的左、右兩個功率管的柵源回路和漏源回路上分別加電感,研究其對功率管開關特性的影響;文獻[10]中在研究寄生電感對SiC JFET開關特性影響的基礎上,提出了有效的吸收電路;文獻[11]中綜合考慮了輸入、輸出電感、開關管內部寄生電感和二極管陰、陽極電感對矩陣變換器中SiC MOSFET電壓過沖和開關損耗的影響;文獻[12]中研究了包括寄生電容、寄生電感、驅動電阻等參數對MOSFET開關波形的影響,并對計算結果和實驗結果進行了比較;文獻[13]在文獻[12]的基礎上增加了在漏源、柵源回路電感耦合和解耦時,寄生電感對器件應力、開關損耗的影響以及漏源電感對EMI影響的研究;文獻[14]中集中分析了寄生電感對高頻同步DC-DC Buck變換器開關損耗的影響。

盡管與Si MOSFET相比,SiC MOSFET是一個性能更為優越的開關器件,但不能理解為它能夠直接替代現有電力電子器件中的硅器件;文獻[14]中寄生電感對變換器開關損耗影響的研究值得借鑒。

本文在文獻[9-14]的基礎上,基于電力電子技術基本理論,研究了高開關速度下漏極寄生電感Ld和源極寄生電感Ls對Buck變換器中SiC MOSFET開關特性的影響。在對考慮了寄生參數時的Buck變換器進行理論分析的基礎上,通過Saber仿真,探究了寄生電感對器件應力和開關損耗的影響。

1Buck變換器開關過程分析

1.1 SiC MOSFET的寄生電感

電感是閉合回路的一種屬性,即是由具有電感的導線組成的封閉電流環,而不是導線本身。從本質上講,開關回路電感是一個集總參數,它包括: ① 晶片和封裝之間的Bonding線的電感;② 引腳及PCB走線的電感。傳統的封裝由于Bonding線與外部引腳線而存在較大的寄生電感,不同封裝類型器件的寄生參數也不相同,因而,選擇器件時應優先考慮封裝引起的寄生參數小的器件[15-16]。在變換器分析時,主要考慮引腳和PCB走線電感。SiC MOSFET寄生電感具體可以分為漏極寄生電感Ld、源極寄生電感Ls、柵極寄生電感Lg。由于Lg對母線側電壓、電流波形影響不大,在分析開關管開關特性時可以忽略。本文所要研究的寄生參數為SiC MOSFET的Ld和Ls,Ld存在于漏極電流回路中,Ls存在于柵極電流回路和漏極電流回路中。

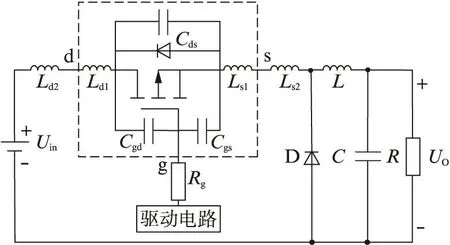

圖1 考慮了寄生電感的Buck變換器Fig.1 Buck converter with parasitic inductance

圖1為考慮寄生電感的Buck變換器。輸入電壓Uin、輸出電壓Uo、驅動電壓Ug(圖中未標出)模型中虛線框內為包含引腳寄生電感與SiC MOSFET極間寄生電容的器件模型,其中,Ld1、Ls1分別為器件漏極與源極引腳寄生電感;Ld2、Ls2分別為PCB走線引起的寄生電感;Rg為驅動電阻,包括SiC MOSFET器件內部的寄生柵極電阻、器件外部驅動電阻以及驅動芯片的輸出電阻;Cgs、Cgd、Cds分別為SiC MOSFET的寄生柵源、柵漏和漏源電容。設續流二極管D為理想二極管,故分析時不考慮續流D對變換器工作過程的影響。

為了方便計算,定義漏極電感為

Ld=Ld1+Ld2

(1)

共源極電感為

Ls=Ls1+Ls2

(2)

1.2 工作過程分析

本文從開通和關斷2個方面分析考慮了寄生電感的Buck變換器的工作過程。

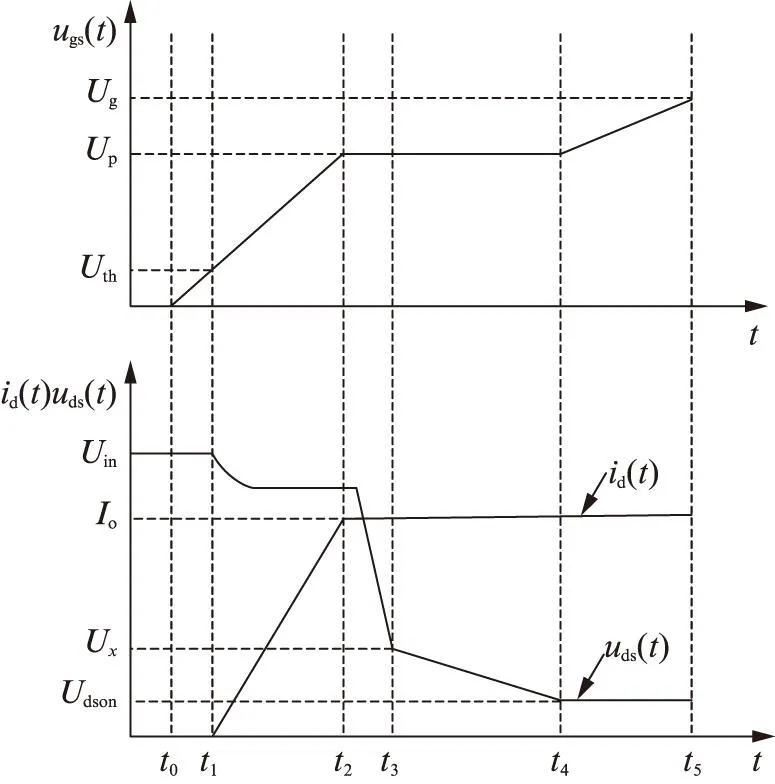

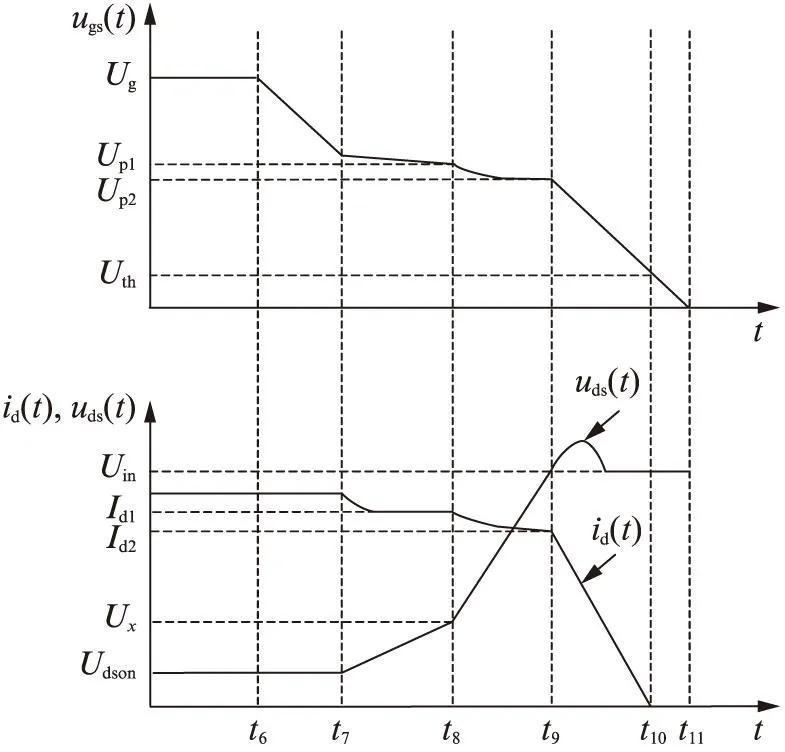

1.2.1開通過程圖2給出了SiC MOSFET開通過程的電壓和電流波形。其中,ugs為柵源極電壓;Up為米勒平臺電壓;Uth為閾值電壓;id為漏極電流;uds為漏源極電壓;Io為負載電流;Ux為SiC MOSFET線性區與飽和區分界點的漏源極電壓;Udson為通態電壓。

圖2 SiC MOSFET開通過程的電壓和電流波形Fig.2 Voltage and current waveforms of SiC MOSFET in turn-on process

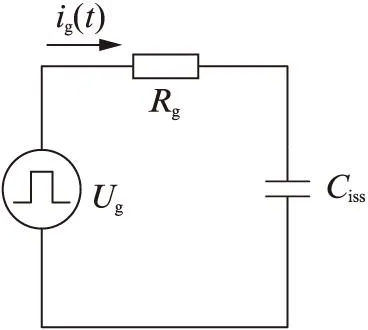

階段1(t0~t1)當柵源極電壓ugs達到閾值電壓Uth之前,漏極電流id=0,故可以忽略Ld和Ls的影響;漏源極電壓uds等于輸入電壓Uin。階段1的等效電路如圖3所示。

圖3 階段1等效電路Fig.3 Equivalent circuit of stage 1

SiC MOSFET的柵源極電壓為

(3)

式中,

τ=RgCiss

(4)

Ciss為SiC MOSFET輸入電容。

Ciss=Cgs+Cgd

(5)

當驅動電壓在時刻t1達到閾值電壓Uth時,階段1結束。

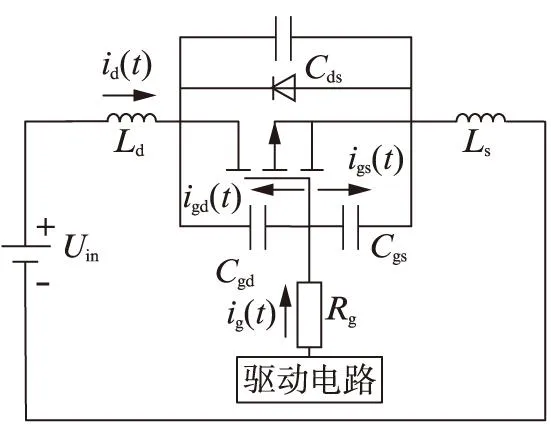

階段2(t1~t2)在該階段ugs>Uth,id從零開始增大,由于電路中存在寄生電感,變化的電流會在寄生電感上產生壓降,引起uds下降。同時,Ls處于驅動回路與主功率回路中,此電感形成SiC MOSFET漏極電流負反饋,抑制主功率電流的變化。階段2等效電路如圖4所示。

圖4 階段2等效電路Fig.4 Equivalent circuit of stage 2

此時,漏源極電壓和漏極電流分別為

(6)

id(t)=gfs(ugs(t)-Uth

(7)

式中,gfs為SiC MOSFET的跨導。

當id=Io時,該階段結束。此時,ugs=Up,Up為米勒平臺電壓。

階段3(t2~t3)當id(t)降至負載電流Io時,ugs=Up,因此,柵源電容不再產生放電電流,uds下降速率較階段2低。由于id(t)維持不變,故ugs也不變,

(8)

漏源極電壓為

(9)

當uds降至Ux時,該階段結束。

階段4(t3~t4)該階段與階段3類似,然而uds降至Ux以下,故開關管已經工作于線性區。此時,uds(t)以較低的速率下降,直至降至通態電壓Udson處。

階段5(t4~t5)該階段為過驅動狀態,SiC MOSFET已經完全開通,uds(t)與id(t)不再發生變化,柵源極電壓ugs在時刻t5升至Ug。

開通過程的開通損耗為

(10)

1.2.2關斷過程圖5為SiC MOSFET關斷過程的電壓與電流波形。

圖5 SiC MOSFET關斷過程的電壓與電流波形Fig.5 Voltage and current waveforms of SiC MOSFET in the turn-off process

階段6(t6~t7)該階段ugs下降,但是未降至Up,故id(t)和uds(t)保持不變,

(11)

階段7(t7~t8)此階段開關管工作于線性區,uds(t)從通態電壓升至ux。ugs(t)維持米勒平臺電壓不變,uds(t)升高。由于ugs(t)不變,故uds(t)變化速率不變,此時有Io流過輸出濾波電容,因此,流過SiC MOSFET的漏極電流較Io降低。該階段SiC MOSFET的漏極電流下降至Id1,米勒平臺電壓下降至Up1。

階段8(t8~t9)該階段與階段8類似,uds(t)上升速率加大,漏極電流降至更低的Id2。米勒平臺電壓降至Up2,當uds(t)上升至輸入電壓Uin時,該階段結束。

階段9(t9~t10)該階段id(t)繼續下降,SiC MOSFET與輸出二極管進行換流,由于電路中寄生電感的存在,變化的電流會在寄生電感上產生壓降,引起uds(t)繼續上升,超出輸入電壓Uin。該階段與開通時階段2類似,當id(t)=0時,該階段結束。

階段10(t10~t11)該階段ugs由SiC MOSFET閾值電壓Uth逐漸降至零。

關斷過程的關斷損耗為

(12)

由以上分析可見,由于寄生電感的存在,在開通和關斷初期阻礙了柵極電流的變化,使得驅動器對柵極電容充、放電時間變長,即功率開關管的開通和關斷時間變長。另外,由于寄生電感的存在,當線路流過的電流變化時,便會在寄生電感上感應出電壓,此感應電壓處于功率回路或驅動回路中,影響開關管的工作波形,進而影響開關管開關的損耗。

2仿真與分析

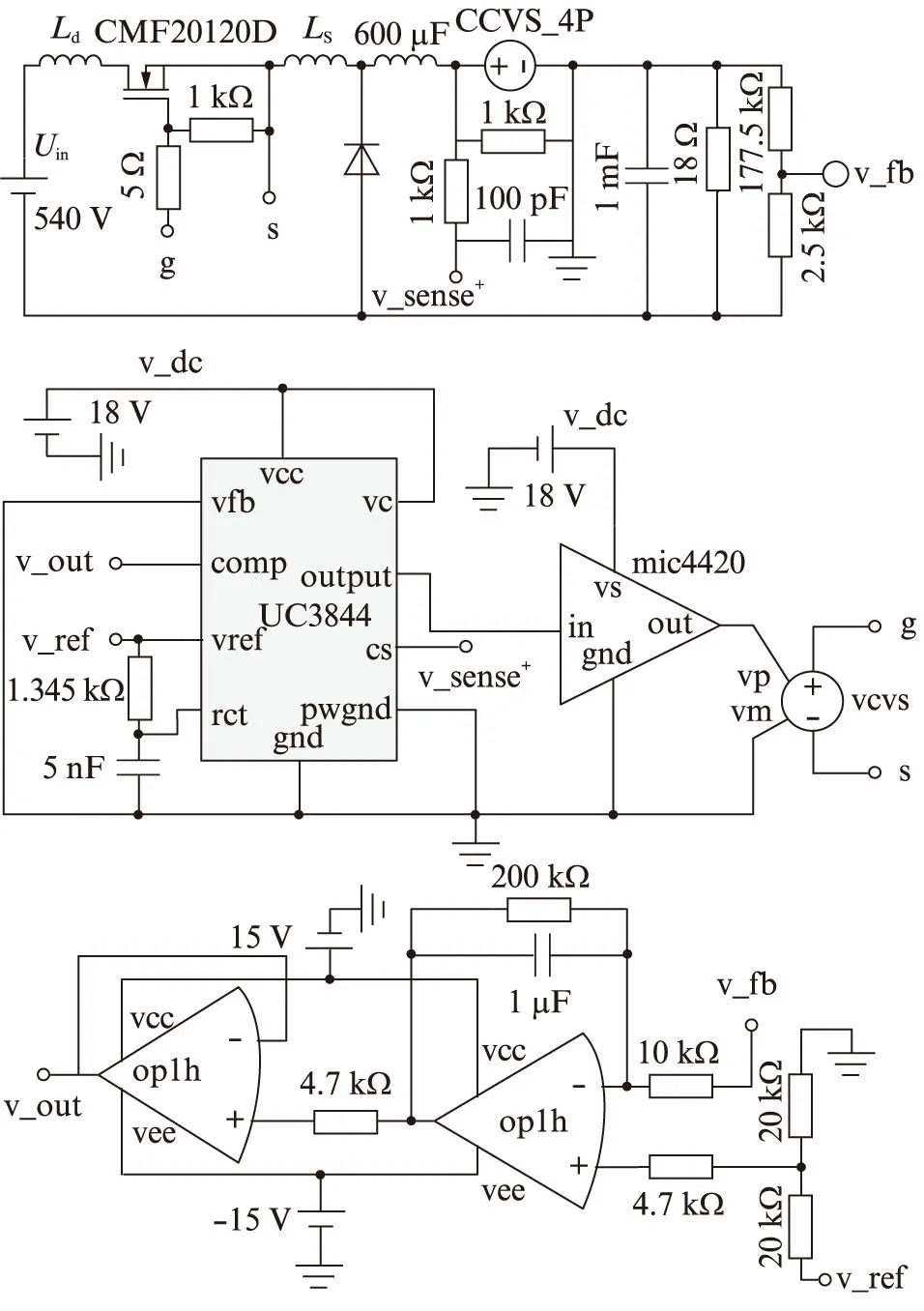

本文選用Cree公司TO247封裝的CMF20120D[17](漏源極擊穿電壓為12kV,最大漏極電流Idmax=42A)作為SiC MOSFET,根據文獻[18]中對SiC MOSFET建模的方法建立器件模型。變換器參數設計如下:Uin=540V (DC),Uo=180V (DC),輸出電流Io=10A,紋波率γ=0.2,工作頻率f=100kHz,電路工作于電流連續模式(Continuous Conduction Mode, CCM)時,控制芯片選用UC3844[19],續流二極管選用理想二極管。仿真電路如圖6所示。

圖6 仿真電路圖Fig.6 Simulation circuit

為了探究不同寄生電感對SiC MOSFET開關特性的影響,本文使用Saber仿真軟件,分別取Ls、Ld為0,50,100,150和200nH進行仿真實驗。

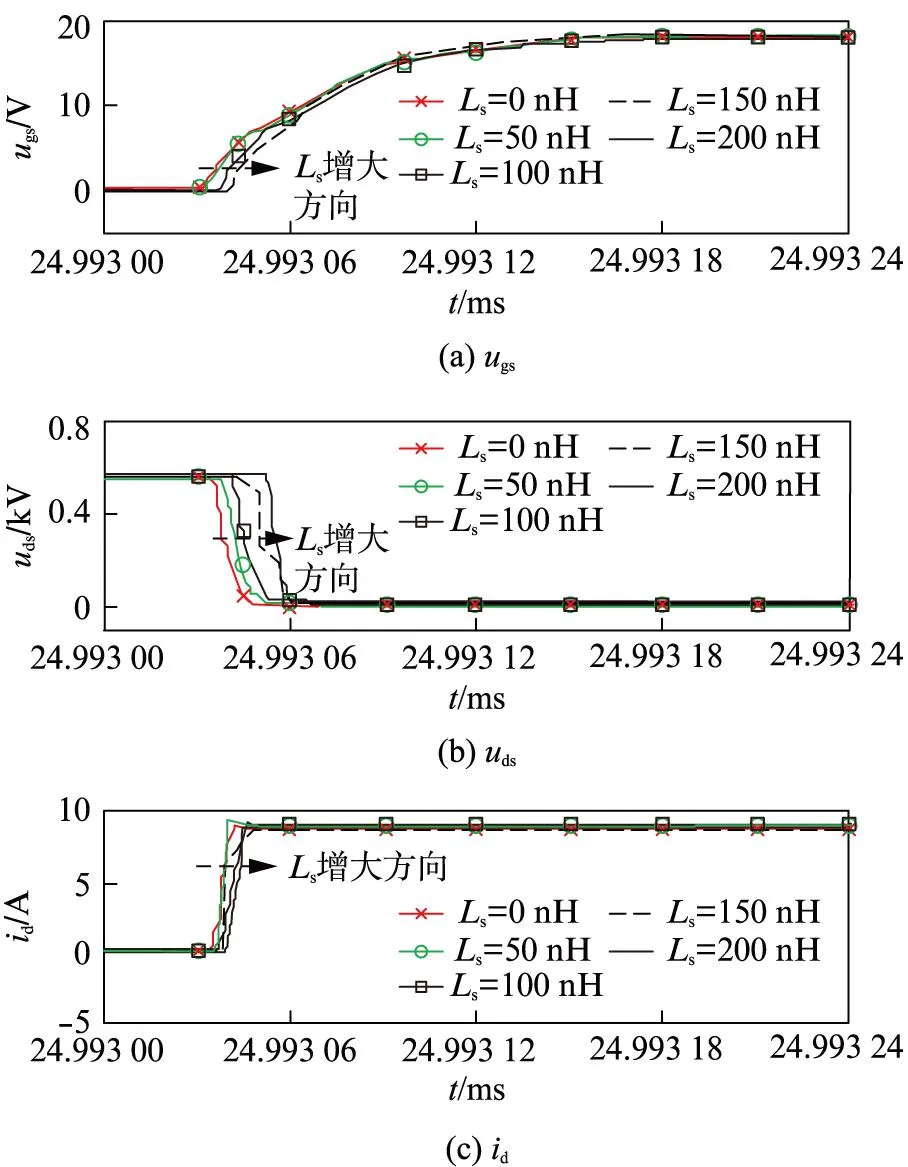

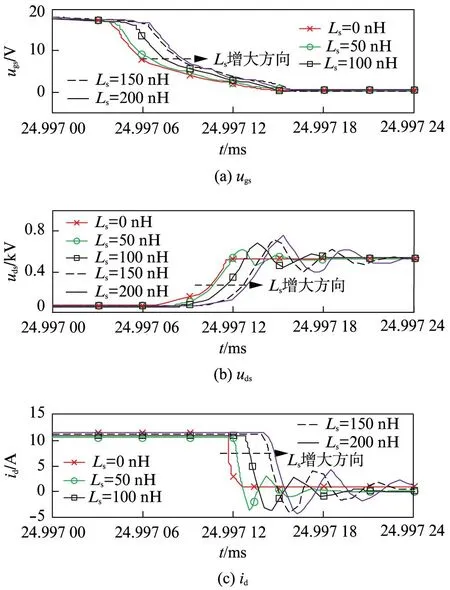

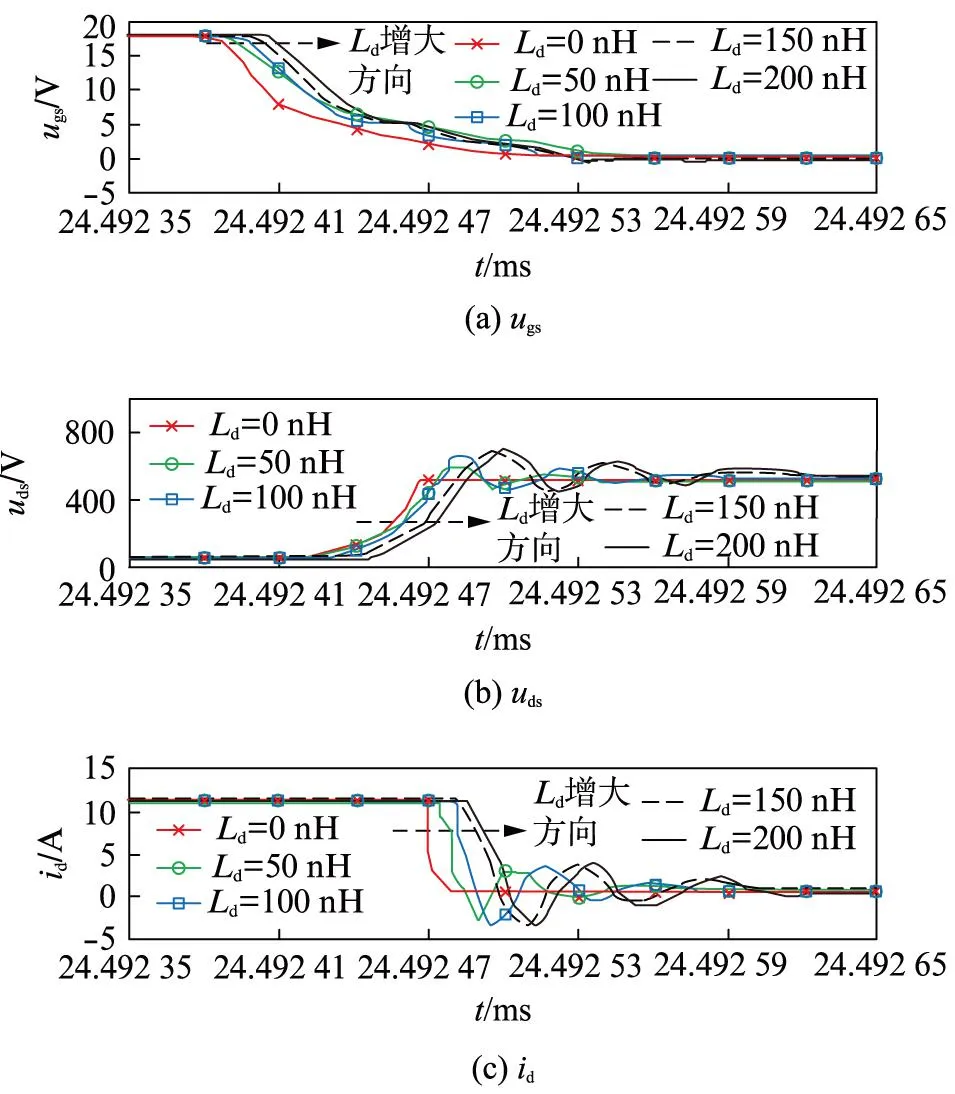

圖7、8分別為SiC MOSFET開通和關斷時,Ls對其電壓和電流波形的影響。由仿真對比可知,當SiC MOSFET開通時,增加Ls使加在柵源極上的驅動電壓ugs的上升速度有所減慢,導致SiC MOSFET的id上升的時間稍有滯后;又由于Ls的存在,使id上升速率減慢,開關管的開通過程變長。當SiC MOSFET關斷時,增加Ls使SiC MOSFET的漏源電壓uds過沖和漏極電流id下沖都會增加,如當Ls從50nH增大到200nH時,uds過沖由20%加大到48%,id下沖由35%加大到40%,關斷過程也變長。

圖7 Ls對SiC MOSFET開通時波形的影響Fig.7 Influence of source stray inductance Ls in the turn-on process

圖8 Ls對SiC MOSFET關斷時波形的影響Fig.8 Influence of source stray inductance Ls in the turn-off process

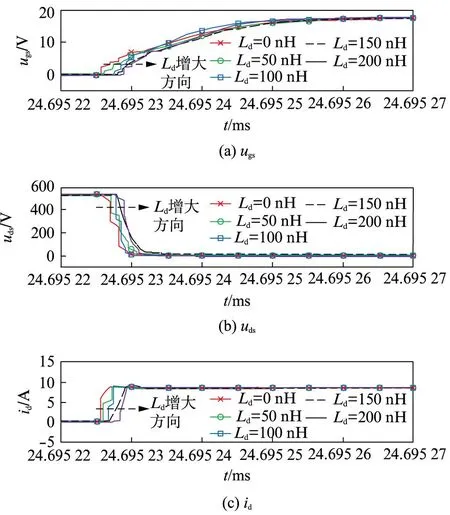

圖9、10中分別給出了Ld對SiC MOSFET開通和關斷時電壓、電流波形的影響。同理,當SiC MOSFET開通時,增加Ld使SiC MOSFET的id上升的速率減慢,開通過程變長;當SiC MOSFET關斷時,增加Ld使SiC MOSFET的uds過沖和id下沖都會增加,如當Ld由50nH增大到200nH時,uds過沖從19%加大到46%,id下沖從37%加大到43%,關斷過程也變長。

圖9 Ld對SiC MOSFET開通時波形的影響Fig.9 Influence of drain stray inductance Ld in the turn-on process

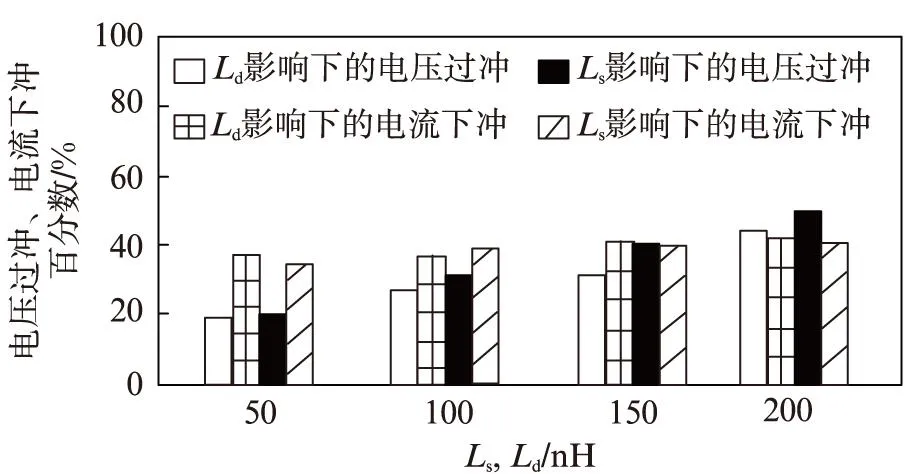

為了量化寄生電感的影響,本文對器件應力和開關損耗進行了研究。圖11給出了寄生電感對器件應力的影響圖。由圖可見,增加SiC MOSFET的Ls和Ld,漏源電壓過沖和漏極電流下沖相應增加。

圖10 Ld對SiC MOSFET關斷時波形的影響Fig.10 Influence of source stray inductance Ld in the turn-off process

圖11 寄生電感對器件應力的影響Fig.11 Influence of parasitic inductance to stress of the device

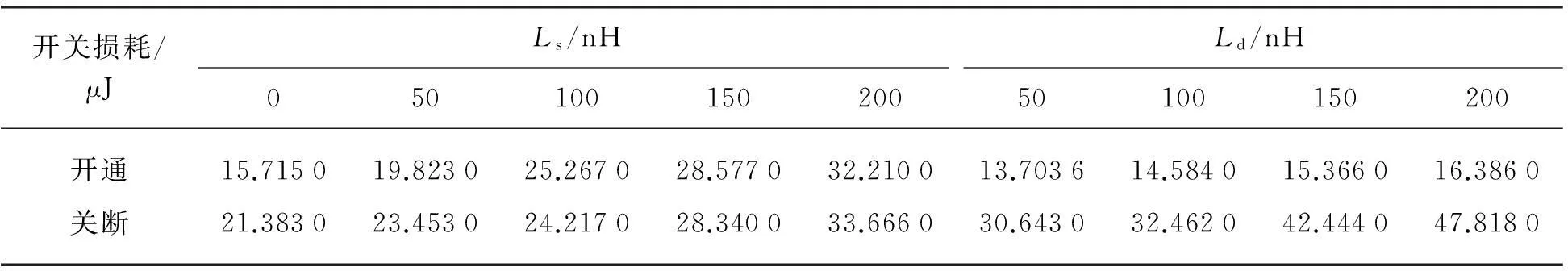

表1給出了單獨考慮寄生電感Ls和Ld時的開通損耗和關斷損耗。很明顯,隨著SiC MOSFET的Ls和Ld的增加,開通和關斷損耗也有相應增加。

表1 單獨考慮Ls和Ld時的開通損耗和關斷損耗Tab.1 Switching loss when parasitic inductance Ls and Ld are considered separately

3結語

本文研究了高開關速度下,漏極電感Ld和源極電感Ls對Buck電路中SiC MOSFET開關特性的影響,重點探討了其對器件應力和開關損耗的影響,結果表明: 隨著寄生電感Ld或Ls的增大,SiC MOSFET的電壓過沖、電流下沖都加大,開關損耗增加。如Ls由50nH增大到200nH時,電壓過沖由20%加大到48%,電流下沖由35%加大到40%,開通損耗從19.823μJ增加到32.210μJ,關斷損耗由23.453μJ增加到33.666μJ;Ld由50nH增大到200nH時,電壓過沖由19%加大到46%,電流下沖由37%加大到43%,開通損耗由13.7036μJ增加到16.3860μJ,關斷損耗由30.643μJ增加到47.818μJ。因此,在選擇器件、設計電路時需要特別留意,可以通過減小Ls和Ld,既減少了開關損耗又減小了振蕩。

參考文獻:

[1]馬策宇,陸蓉,袁源,等.SiC功率器件在Buck電路中的應用研究[J].電力電子技術,2014,48(8): 54-57.

[2]王旸文,趙彪,嚴干貴,等.新型SiC功率器件在Boost電路中的應用分析[J].電力電子技術,2013,47(11): 106-108.

[3]Ostling M, Ghandi R,Zetterling C.SiC power devices-present status, applications and future perspective[C]∥Proceedigs of the 23rd International Symposium on Power Semiconductor Devices and ICs(ISPSD).San Diego,CA: IEEE,2011: 10-15.

[4]Safari S,Castellazzi A,Wheeler P.Evaluation of SiC power devices for a high power density matrix converter[C]∥Energy Conversion Congress and Exposition(ECCE).[S.L.]: IEEE,2012: 3934-3941.

[5]王學梅.寬禁帶碳化硅功率器件在電動汽車中的研究與應用[J].中國電機工程學報,2014,34(3): 371-379.

[6]McNutt T,Hefner A,Mantooth A,et al.Silicon carbide power MOSFET model and parameter extraction sequence[J].IEEE Transactions on Power Electronics,2007,22(2): 353-363.

[7]張玉明,湯曉燕,張義門.SiC功率器件的研究和展望[J].電力電子技術,2008,42(12): 60-62.

[8]陸玨晶.碳化硅MOSFET應用技術研究[D].南京: 南京航空航天大學,2013: 1-2.

[10]Stewart C,Escobar-Mejía A,Balda J C.Guidelines for developing power stage layouts using normally-off SiC JFETs based on parasitic analysis[C]∥2013 IEEE.Energy Conversion Congress and Exposition(ECCE).Denver: IEEE,2013: 948-955.

[11]Safari S,Castellazzi A ,Wheeler P.Experimental and analyticed performance evaluation of Sic power devices in matrix converter[J].IEEE Transactions on Power Electronics,2014,29(5): 2584-2596.

[12]Wang Jianjing,Chung Shuhung,Li R T.Characterization and experimental assessment of the effects of parasitic elements on the MOSFET switching performance[J].IEEE Transactions on Power Electronics,2012,28(1): 573-590.

[13]Chen Zheng,Boroyevich D,Burgos R.Experimental parametric study of the parasitic inductance influence on MOSFET switching characteristics[C]∥Proceedings of the 2010 International Power Electronics Conference(IPEC).Sapporo,Japan: IEEE,2010: 164-169.

[14]Meade T,O’Sullivan D,Foley R,et al.Parasitic inductance effect on switching losses for a high frequency DC-DC converter[C]∥Applied Power Electronics Conference and Exposition(APEC).Austin,USA: IEEE,2008: 3-9.

[15]Balogh L.Design and application guide for high speed MOSFET gate drive circuits[J].Power Supply Design Seminar(SEM 1400),2001: 1-37.

[16]史修德.考慮電路寄生參數的BOOST變換器開關特性研究[D].哈爾濱: 哈爾濱工業大學,2012: 1-2.

[17]Cree,Inc.CMF20120D-Silicon Carbide Power MOSFET[EB/OL].[2014-05-25].http:∥www.cree.com/~/media/Files/Cree/Power/Data Sheets/CM-F20120D.pdf.

[18]孫凱,陸玨晶,吳紅飛,等.碳化硅MOSFET的變溫度參數建模[J].中國電機工程學報,2013,33(3): 37-43.

[19]Texas Instruments,Inc.Current Mode PWM Controller[EB/OL].[2014-01-25].http:∥www.ti.com.cn/cn/lit/ds/symlink/uc3844.pdf.

Simulation of Parasitic Inductance Influence on SiC MOSFETSwitching Performance in Buck Converter

FANChunli,ZHAOChaohui,YUChenglong,LONGJuemin

(School of Electrical Engineering, Shanghai Dianji University, Shanghai 200240, China)

Abstract:To study the influence of parasitic inductance on SiC MOSFET switching behavior at high switching speed, this paper studies the buck converter. Based on the basic theory of power electronics, the switching process of SiC MOSFET in a buck converter under the influence of the drain parasitic inductance and source parasitic inductance is analyzed, and demonstrated with the simulation software Saber. The simulation results show that, by increasing parasitic inductance, voltage and current stress of SiC MOSFET increase, the turn on time and turn off time become longer, and switching loss increases accordingly.

Key words:SiC; metal-oxide semiconductor field effect transistor(MOSFET); Buck converter; parasitic inductance; switching performance

文章編號2095-0020(2015)02-0070-07

通信作者:高桂革(1968-),女,教授,博士,主要研究方向為電氣工程、測控系統、分布參數系統、小波理論及應用等,E-mail: gaogg@sdju.edu.cn

作者簡介:肖浩(1990-),男,碩士生,主要研究方向為風電柔性直流并網,E-mail: xhshdj@126.com

基金項目:上海市教育委員會科研創新項目資助(11YZ267)

收稿日期:2015-02-25

中圖分類號:TM 564.3;TN 386.1

文獻標志碼:A