基于電流復(fù)用技術(shù)的亞mW級(jí)CMOS VCO設(shè)計(jì)

,

(1.南陽(yáng)理工學(xué)院, 河南南陽(yáng) 473004;2.鄭州大學(xué)信息工程學(xué)院, 河南鄭州 450001)

0 引言

移動(dòng)收發(fā)機(jī)逐漸向高數(shù)據(jù)速率、多頻帶以及多標(biāo)準(zhǔn)化的特性發(fā)展,單個(gè)收發(fā)機(jī)就具有用于多種標(biāo)準(zhǔn)的發(fā)送和接收通道,為了盡快使其實(shí)用化,對(duì)收發(fā)機(jī)中相關(guān)模塊的功耗提出了越來(lái)越嚴(yán)格的要求[1]。壓控振蕩器(VCO)作為收發(fā)機(jī)中的主要模塊,在對(duì)其進(jìn)行設(shè)計(jì)時(shí),需要同時(shí)考慮相位噪聲、調(diào)諧范圍以及功耗等性能指標(biāo)。

目前,CMOS VCO主要可分為環(huán)形VCO和LC VCO兩類(lèi),LC VCO的相位噪聲通常優(yōu)于環(huán)形VCO,因此得以廣泛應(yīng)用。LC VCO主要由負(fù)阻產(chǎn)生器以及諧振回路組成,負(fù)阻產(chǎn)生器由交叉耦合晶體管對(duì)實(shí)現(xiàn),諧振回路由在片電感和變?nèi)荻O管實(shí)現(xiàn)。

為了降低射頻電路的功耗,提高能源效率,研究者提出了電流復(fù)用技術(shù),例如文獻(xiàn)[2-3]所設(shè)計(jì)的放大器,文獻(xiàn)[4]更是利用該技術(shù)設(shè)計(jì)了一款功耗僅為1 mW的電流復(fù)用技術(shù)(CR) VCO。典型的CR VCO電路是非對(duì)稱(chēng)的,因此它的輸出振幅平衡度較差。針對(duì)該缺點(diǎn),文獻(xiàn)[4]提出了電阻補(bǔ)償技術(shù),然而該技術(shù)只適用于特定的頻率范圍。為了克服此缺陷,本文提出了一種先進(jìn)的補(bǔ)償技術(shù),該技術(shù)能夠在足夠?qū)挼念l率范圍內(nèi)改善輸出振幅的平衡性。

1 CR VCO的補(bǔ)償技術(shù)

圖1為不包含有振幅補(bǔ)償技術(shù)的典型CR VCO電路圖,由于電路的非對(duì)稱(chēng)特性,導(dǎo)致A點(diǎn)和B點(diǎn)處的阻抗不相等,進(jìn)而導(dǎo)致振幅非平衡,因而出現(xiàn)了多種補(bǔ)償技術(shù)。

圖1 典型CR VCO的電路圖

圖2(a)給出了一種振幅補(bǔ)償技術(shù),在NMOS的源端插入補(bǔ)償電阻RC[4-5]。由于該技術(shù)易于實(shí)現(xiàn),得以廣泛應(yīng)用。然而,節(jié)點(diǎn)A和B處的阻抗隨著振蕩頻率的變化而變化,使其僅適用于特定的頻率范圍,并且,在片電阻也會(huì)受到工藝波動(dòng)的影響。

為了消除工藝波動(dòng)的影響,可用MOS晶體管代替電阻,如圖2(b)所示[6]。通過(guò)調(diào)節(jié)VB,將圖2(b)中的補(bǔ)償晶體管MC偏置于線(xiàn)性區(qū)域,相當(dāng)于可變電阻,因而消除了在片電阻的工藝波動(dòng)影響。為了實(shí)現(xiàn)每個(gè)振蕩頻率對(duì)應(yīng)特定的VB,應(yīng)該采用數(shù)模轉(zhuǎn)換器(DAC)電路產(chǎn)生VB,導(dǎo)致了較大的功率消耗。

圖2(c)為自發(fā)式跨導(dǎo)匹配(STM)技術(shù)的示意圖[7],在傳統(tǒng)的CR VCO電路中插入兩個(gè)補(bǔ)償晶體管M3和M4,兩個(gè)晶體管都被偏置在線(xiàn)性工作區(qū),使其等效為電壓控制的電阻器。它的工作原理為首先探測(cè)非平衡振幅,然后將振幅誤差反饋回補(bǔ)償晶體管的柵極,實(shí)現(xiàn)補(bǔ)償。STM能夠在不額外增加DAC的前提下,實(shí)現(xiàn)整個(gè)振蕩頻率范圍內(nèi)的補(bǔ)償,然而由于STM技術(shù)存在4個(gè)堆疊的晶體管,使其工作時(shí)需要采用較高的工作電壓,限制了功耗的降低。

(a)電阻技術(shù)

(b)晶體管技術(shù)

(c)STM技術(shù)圖2 補(bǔ)償技術(shù)

2 設(shè)計(jì)理論

2.1 CR回路

圖3給出了典型CR VCO的小信號(hào)模型,經(jīng)計(jì)算,可得有效輸入導(dǎo)納Yin為

(1)

式中,gmn和gmp分別為晶體管NMOS和PMOS的跨導(dǎo),n和p分別定義為

(2)

(3)

式中,gmbn和gmbp分別為晶體管NMOS和PMOS的體跨導(dǎo),VBSn和VGSn分別為NMOS管的襯底-源極間電壓和柵-源極間電壓,VSBp和VSGp分別為PMOS管的襯底-源極間電壓和柵-源極間電壓,ηn和ηp為與晶體管工藝相關(guān)的參數(shù),正比于體效應(yīng)系數(shù)γ。

圖3 CR VCO的小信號(hào)模型

假設(shè)晶體管NMOS和PMOS完全對(duì)稱(chēng),那么式(1)可簡(jiǎn)化為

(4)

由上式可見(jiàn),如果消除晶體管的體效應(yīng),Yin等于-gm/2,此刻等效于交叉耦合晶體管對(duì)。

為了使電路可工作于低電壓下,可采用體偏置技術(shù),該技術(shù)能夠減小晶體管的閾值電壓,使其可在低電壓下工作。然而,體偏置電壓的引入增大了電路的直流電流,增加了功耗。在VCO電路設(shè)計(jì)中,需要綜合考慮相位噪聲、工作電壓、調(diào)諧范圍以及功耗等指標(biāo)。

通常情況下,將Yin的絕對(duì)值設(shè)置成LC諧振回路總跨導(dǎo)的3倍大小,以確保VCO在任何狀態(tài)下都能開(kāi)啟振蕩狀態(tài)。自偏電壓VGSn和VSGp的大小決定于晶體管的尺寸,最優(yōu)化柵極電壓設(shè)置成漏極供電電壓的一半大小,以取得最大的輸出電壓擺幅,降低相位噪聲。

2.2 基于STM的改進(jìn)技術(shù)

圖1中,節(jié)點(diǎn)A和B處的電壓分為

vA(t)=zA(t)[gMp(t)+gMBp(t)]·vSG(t)

(5)

vB(t)=zB(t)[gMn(t)+gMBn(t)]·vGS(t)

(6)

式中,zA(t)和zB(t)分別為節(jié)點(diǎn)A和B處的有效阻抗,這兩者的大小取決于MOS晶體管的尺寸和LC諧振回路。由于圖1電路結(jié)構(gòu)的非對(duì)稱(chēng)性,導(dǎo)致zA(t)≠zB(t),進(jìn)而導(dǎo)致輸出信號(hào)振幅的非平衡性。

為了保持兩個(gè)輸出信號(hào)的一致性,應(yīng)該使得vA(t)=vB(t),因此有

[gMn(t)+gMBn(t)]zB(t)=[gMp(t)+gMBp(t)]zA(t)

(7)

其中,為了使電路保持穩(wěn)定振蕩,上式假設(shè)了vGS(t)和vSG(t)的相位差為180°。

在振蕩狀態(tài)下時(shí),在振蕩頻率ω處持續(xù)輸出差分信號(hào)。當(dāng)兩個(gè)輸出信號(hào)發(fā)生電壓幅度不一致的情況時(shí),電路將會(huì)產(chǎn)生誤差反饋電壓vN,表達(dá)式為

vN(ωt)=V0cos(ωt)+(V0-δV)cos(ωt-π)=

δVcos(ωt)

(8)

vN(ωt)與振幅偏差成正比,而振幅偏差可由中心抽頭電感獲取。如圖2(c)所示的STM技術(shù)中,引入補(bǔ)償PMOS晶體管M3和NMOS晶體管M4,通過(guò)從電感LT獲取的誤差電壓來(lái)保持輸出振蕩電壓幅度的平衡狀態(tài),然而由于STM技術(shù)存在4個(gè)堆疊的晶體管,使其工作時(shí)需要采用較高的工作電壓。

為了使電路能夠在較小的電壓下工作,本文對(duì)STM技術(shù)進(jìn)行了改進(jìn),改進(jìn)后的技術(shù)僅包含有一個(gè)補(bǔ)償晶體管,如圖4所示。改進(jìn)的STM(m-STM)技術(shù)不僅可以保持輸出信號(hào)振幅的平衡,還可以消除掉原STM技術(shù)中M4晶體管的噪聲,進(jìn)而優(yōu)化VCO相位噪聲。

圖4 改進(jìn)STM CR VCO的電路圖

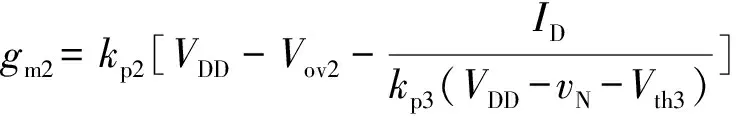

圖4中M2的有效跨導(dǎo)gm2為

式中,kp2和kp3為器件工藝相關(guān)參數(shù),與柵極寬長(zhǎng)比成正比例關(guān)系,Vth3為晶體管M3的閾值電壓,VDD和ID分別為直流電壓和電流。電路中M3偏置在線(xiàn)性區(qū)域,作為受電壓控制的可變電阻,vN用于控制晶體管M2的柵源間電壓,進(jìn)而決定M2的跨導(dǎo)。

當(dāng)發(fā)生振幅偏差時(shí),電路產(chǎn)生誤差電壓vN,M3的柵極電壓向反方向改變,也就是gm2對(duì)于vN的偏導(dǎo)數(shù)小于零。因而,gm2被誤差電壓vN所補(bǔ)償進(jìn)而發(fā)生改變,直至兩個(gè)輸出信號(hào)幅度相等。

3 亞毫瓦級(jí)CR VCO設(shè)計(jì)與測(cè)試

本文所提出的采用m-STM技術(shù)的CR VCO如圖4所示,晶體管M1和M2構(gòu)成負(fù)導(dǎo)納產(chǎn)生電路,并且M1和M2分別通過(guò)電阻R1和R2采用體偏置方式。由式(1)可見(jiàn),采取體偏壓方式改善了電路負(fù)導(dǎo)納并且降低了晶體管的閾值電壓[8],電路節(jié)點(diǎn)A和B處的電壓設(shè)置成0.42 V,反饋給M1和M2的體端。

在片螺旋電感LT和累積型MOS變?nèi)莨蹸V構(gòu)成諧振回路,并且電感需要有中心抽頭以用于檢測(cè)節(jié)點(diǎn)A和B處的電壓幅度偏差,進(jìn)而在節(jié)點(diǎn)N處產(chǎn)生誤差電壓vN。補(bǔ)償晶體管M3的柵極受誤差電壓vN控制,進(jìn)而自動(dòng)調(diào)節(jié)M3的跨導(dǎo)以保持輸出信號(hào)的平衡性。

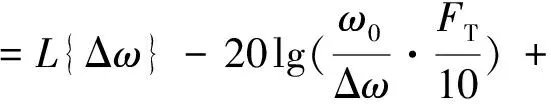

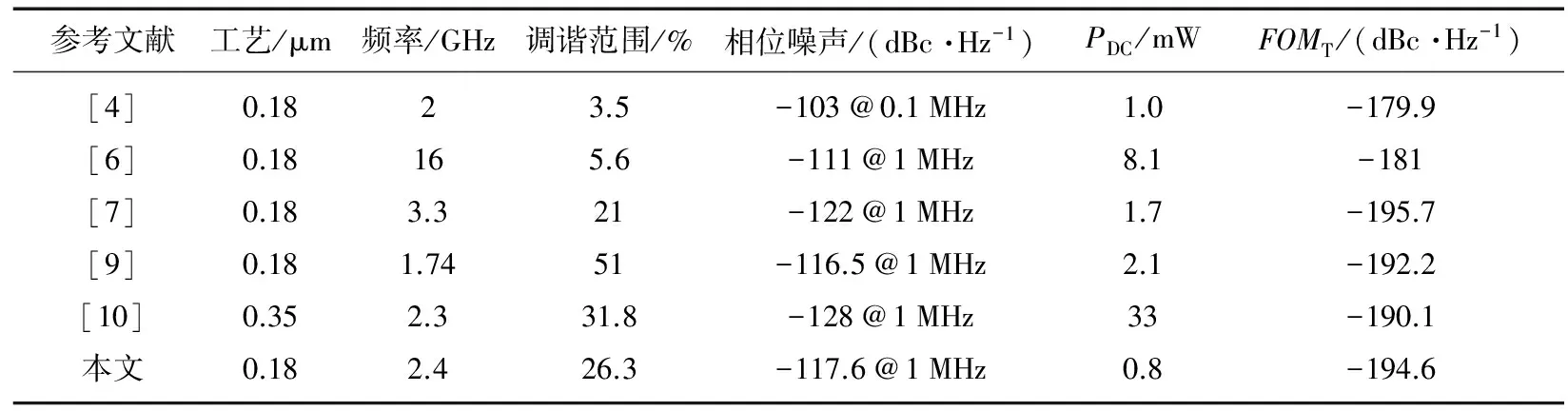

基于SMIC 0.18 μm RF CMOS工藝對(duì)圖4所示的VCO進(jìn)行流片實(shí)現(xiàn),圖5所示即為該VCO的芯片照片,大小為0.62 mm×0.73 mm。該VCO在1 V電壓供電下,消耗了0.8 mW的功耗,版圖后仿真結(jié)果顯示功耗為0.74 mW,與實(shí)測(cè)結(jié)果相接近。測(cè)試數(shù)據(jù)采用頻譜分析儀Agilent N9030A對(duì)VCO的振蕩頻率和相位噪聲進(jìn)行在片測(cè)試,隨著控制電壓VT從0 V到1 V變化時(shí),測(cè)試的輸出振蕩頻率為2.05~2.68 GHz,調(diào)諧范圍為26.3%,如圖6所示。相位噪聲的測(cè)試采用頻譜分析儀Agilent N9030A中固有的相位噪聲測(cè)試模式,圖7給出了在振蕩頻率2.4 GHz處VCO相位噪聲的測(cè)試結(jié)果,由圖可見(jiàn),相位噪聲達(dá)到-117.6 dBc/Hz@1 MHz。圖8給出了VCO輸出功率的測(cè)試結(jié)果,可見(jiàn)輸出功率為-1.3~2 dBm,具有較高的功率,足以驅(qū)動(dòng)下一級(jí)電路。

表1總結(jié)了本文所設(shè)計(jì)的VCO的性能,并且與其他文獻(xiàn)所報(bào)道的VCO性能進(jìn)行了比較[4,6-7, 9-10],表中FOMT采用式(10)的表達(dá)式計(jì)算得到。由表可見(jiàn),本文所提出并設(shè)計(jì)的VCO的綜合性能優(yōu)于其他文獻(xiàn)。

(10)

圖5 m-STM CR VCO的芯片照片

圖6 振蕩頻率的測(cè)試結(jié)果

圖7 相位噪聲的測(cè)試結(jié)果

圖8 輸出功率的測(cè)試結(jié)果

表1 CMOS VCO比較結(jié)果

4 結(jié)束語(yǔ)

本文首先研究了CR VCO的振幅補(bǔ)償技術(shù),然后提出了m-STM技術(shù)以保持振蕩輸出信號(hào)的平衡性。相比較于傳統(tǒng)的STM技術(shù)而言,m-STM技術(shù)通過(guò)移除一個(gè)晶體管的方式,使VCO能夠工作于較低的電壓下,消耗的功耗較低,并且采用體偏置技術(shù),減小了晶體管的閾值電壓,進(jìn)一步降低了工作電壓,降低了功耗。芯片實(shí)測(cè)結(jié)果表明,本文所提出的VCO在僅消耗0.8 mW功耗的情況下,振蕩頻率為2.05~2.68 GHz,調(diào)諧范圍高達(dá)26.3%,并且相位噪聲低至-117.6 dBc/Hz@1 MHz。

[1] 劉秉策,柴文乾,代傳堂,等. X波段便攜式情報(bào)雷達(dá)集成化接收機(jī)設(shè)計(jì)[J]. 雷達(dá)科學(xué)與技術(shù), 2016, 14(2):206-209.

LIU Bingce, CHAI Wenqian, DAI Chuantang, et al. Design Method for the Integrated Receiver of an X-Band Portable Battlefield Surveillance Radar[J]. Radar Science and Technology, 2016, 14(2):206-209.(in Chinese)

[2] CRUZ H, HUANG H Y, LEE S Y, et al. A 1.3 mW Low-IF, Current-Reuse, and Current-Bleeding RF Front-End for the MICS Band with Sensitivity of -97 dBm[J]. IEEE Trans on Circuits and Systems I:Regular Papers, 2015, 62(6):1627-1636.

[3] PARVIZI M, ALLIDINA K, EI-GAMAL M N. Short Channel Output Conductance Enhancement Through Forward Body Biasing to Realize a 0.5 V 250 μW 0.6—4.2 GHz Current-Reuse CMOS LNA[J]. IEEE Journal of Solid-State Circuits, 2016, 51(3):574-586.

[4] YUN S J, SHIN S B, CHOI H C, et al. A 1 mW Current-Reuse CMOS Differential LC-VCO with Low Phase Noise[C]∥IEEE International Solid-State Circuits Conference, San Francisco, CA:IEEE, 2005:540-541.

[5] ZHANG Y, LIAO L, WEI M D, et al. A 2.4-GHz Low Power High Performance Frequency Synthesizer Based on Current-Reuse VCO and Symmetric Charge Pump[C]∥IEEE Radio Frequency Integrated Circuits Symposium, Seattle, WA:IEEE, 2013:119-122.

[6] YANG C L, CHIANG Y C. Low Phase-Noise and Low-Power CMOS VCO Constructed in Current-Reused Configuration[J]. IEEE Microwave and Wireless Components Letters, 2008, 18(2):136-138.

[7] WEI M D, CHANG S F, HUANG S W. An Amplitude-Balanced Current-Reused CMOS VCO Using Spontaneous Transconductance Match Technique[J]. IEEE Microwave and Wireless Components Letters, 2009, 19(6):395-397.

[8] 甘學(xué)溫,趙寶瑛,陳中建,等. 集成電路原理與設(shè)計(jì)[M]. 北京:北京大學(xué)出版社, 2006:87-91.

[9] 陳華,郭桂良,張玉琳,等. 1.3~2.2 GHz低噪聲低功耗CMOS LC VCO的設(shè)計(jì)[J]. 微電子學(xué)與計(jì)算機(jī), 2015, 32(1):24-28.

[10] 丁理想,吳洪江,盧東旭,等. 寬帶LC壓控振蕩器的相位噪聲優(yōu)化設(shè)計(jì)[J]. 半導(dǎo)體技術(shù), 2015, 40(2):89-92.