基于CPLD可編程邏輯控制器件FIFO的設計

2016-04-06 00:48:52周慶芳

文理導航

2016年9期

周慶芳

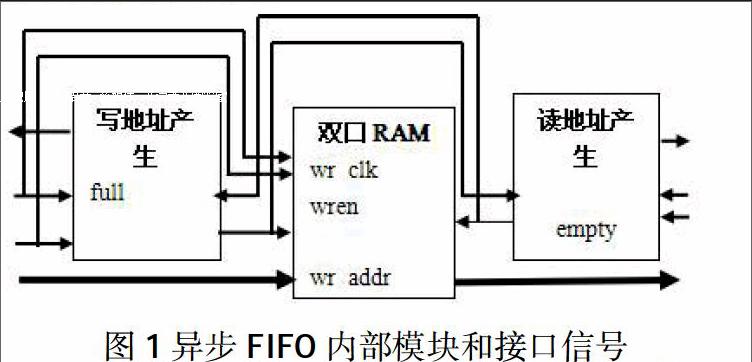

【摘 要】隨著電子技術的不斷發展與進步,電子系統的設計方法發生了很大的變化,那些只提供特定的邏輯功能,不能夠由用戶根據具體設計的需要修改的成品邏輯器件已經慢慢被可編程邏輯控制器件所替代。本文介紹PLD可編程邏輯器件的設計開發及相關軟件的使用。并通過PLD的應用設計FIFO。在傳統設計的基礎上提出一種新穎的電路結構并對其進行綜合仿真和實現。首先介紹異步FIFO的概念、應用及其結構,然后分析實現異步FIFO的難點問題及其解決辦法;詳細介紹了每一個過程的設計思想和處理過程。使用Max+plusII和ALTERA公司的實驗箱對FIFO進行設計。

【關鍵詞】CPLD;Max+plusII;異步FIFO

一、引言

當前電子系統的設計正朝著速度快、容量大、體積小、質量輕、用電少的方向發展。推動該潮流迅猛發展的決定性的因素就是使用了現代化的EDA設計工具,使電子系統的電路設計變得更簡單,設計周期大大縮短。設計人員在不必更改硬件電路設計的前提下,只須要修改可編程邏輯電路的功能和用戶軟件,就可以完成面向不同應用需求的系統設計了。PLD(Programmable Logic Devices)是可以由用戶進行編程實現所需邏輯功能的數字集成電路。利用PLD內部的邏輯結構可以實現任何布爾表達式或寄存器函數。它能完成任何數字器件的功能,上至高性能CPU,下至簡單的74電路,都可以用PLD來實現。FIFO (First In First Out)是一種在電子系統得到廣泛應用的器件,通常用于數據的緩存和用于容納異步信號的頻率或相位的差異。

二、PLD和……

登錄APP查看全文