基于FPGA的音頻信號采集處理系統設計

基于FPGA的音頻信號采集處理系統設計

李佳希 王才敏 北京航天控制儀器研究所通信系統事業部

本文介紹一種基于FPGA的音頻采集處理系統。系統以FPGA器件為控制核心,通過AD/DA控制模塊實現數據采集功能;通過SDRAM控制模塊實現對SDRAM的數據讀寫功能;通過FIR濾波器模塊,實現信號低通濾波處理功能。本設計具有速度快、成本低、體積小等優勢。

FPGA;SDRAM讀寫;FIR濾波

引言

隨著微電子和信號處理技術的發展,數字音頻采集處理技術在眾多領域得到廣泛應用,以FPGA為核心的音頻采集處理系統,在現代數字系統設計中具有廣闊的應用空間。

1.總體設計方案

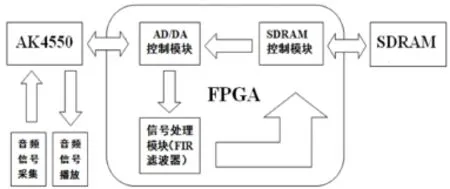

系統總體設計方案如圖1所示,FPGA為系統的控制核心,負責控制AK4550和SDRAM芯片,使它們能夠按特定的時序工作,并且在需要的時候進行調用,也負責對采樣回來的信號進行濾波處理。AK4550負責對采集的音頻信號進行模數轉換。SDRAM負責數據的存儲。

2.硬件控制模塊

2.1 AD/DA控制模塊

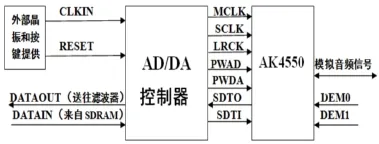

AK4550分別采用兩路模擬信號輸入和輸出,使用簡單靈活。AK4550與FPGA之間通過I2S總線連接,其中MCLK是主時鐘,SCLK是移位時鐘,LRCK是幀時鐘,用于切換左右聲道數據。

AD/DA控制模塊主要由分頻模塊、I2S模塊、系統控制模塊和移位寄存器模塊4部分組成。

分頻模塊:由FPGA的時鐘分頻得到所需要的主時鐘信號MCLK,再由主時鐘分頻得到SCLK和LRCK信號。

I2S模塊:通過分頻得到的MCLK、SCLK和LRCK信號配置AK4550。當LRCK為高電平時,采集16位左聲道數據;反之則采集16位右聲道數據。

圖1 系統結構框圖

圖2 AK4550控制模塊原理圖

系統控制模塊:通過控制PWAD與PWDA來控制AK4550當前的工作狀態,其中高電平代表工作,低電平代表空閑;通過控制DEM0和DEM1來選擇采樣頻率,本設計選擇將DEM0和DEM1同時置高,即采樣頻率選擇為32kHz。

移位寄存器模塊:由于采集的數據為16位,而芯片輸入輸出接口SDTI和SDTO均為1位,故需通過以SCLK為控制時鐘的計數器控制數據的傳輸,每檢測到16個SCLK上升沿信號進行一次數據傳輸。

2.2 SDRAM控制模塊

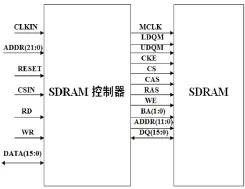

SDRAM控制模塊除了時鐘分頻、數據接口等部分外,主要由一個狀態機來實現,整個狀態機根據需要設計了8個主要狀態,分別為初始化狀態、空閑狀態、刷新狀態、激活狀態、讀、寫等待狀態、讀狀態和寫狀態,通過時鐘上升沿時刻CS、CAS、RAS、WE的不同組合確定當前狀態。狀態機的工作流程為系統上電,對SDRAM進行初始化之后進入空閑狀態,當收到寫命令時,觸發行激活,進入寫等待狀態,執行寫操作。同理當收到讀命令時,觸發行激活,進入讀等待狀態,執行讀操作。當準備打開新的行時進行預充電,與此同時,每當刷新時間到時,控制模塊進入自刷新狀態。

圖3 SDRAM控制模塊原理圖

如圖3所示,SDRAM控制模塊通過外部RD和WR信號控制SDRAM的讀寫,并通過地址輸入確定數據的內容和存放位置。時鐘分頻模塊將外部晶振提供的時鐘信號CLKIN分頻得到MCLK時鐘信號;接口模塊負責數據接口DATA和SDRAM數據接口DQ之間的通信;狀態機模塊負責在各工作狀態提供相應的CKE、CS、CAS、RAS、WE信號,使SDRAM按照正確的狀態運行。

3.信號處理模塊

在FPGA中實現FIR濾波器,首先要確定濾波器的階數及各階的系數,本設計選擇了16位32階、截止頻率為1kHZ的低通濾波器。濾波器的主體部分由總控制器、加法樹、移位累加器、移位寄存器和位選1×16乘法器5個部分組成。

總控制器:總控制器有接受復位信號、產生位移時鐘、產生運算控制時鐘等功能。濾波器是16位的,再加一個移數時鐘脈沖,總共17個時鐘脈沖周期,所以運算控制時鐘是由一個17進制的計數器產生的。

移位寄存器:在一次序列運算結束后,原先存放x(n+1)的寄存器存入x(n+2),而原先存放x(n+2)的寄存器存入x(n+3),以此類推。原先存放x(n)的寄存器存入由AD控制器移位寄存器端口新進來的數據。

位選1×16乘法器:當運算控制時鐘信號到來時,數據h(n)的相應位與x(n)相乘,并把結果送給加法樹。

加法樹:加法樹把所有加數兩個一組分別進行相加,然后將所得到的和值兩個一組繼續相加直到只剩下一個數,即為所有數相加的和。

移位累加器:移位累加器將加法樹得出的結果進行逐個累加。

4.結論

按以上描述設計的基于FPGA的音頻信號采集處理系統經過了FPGA下載驗證,正確配置了AK4550和SDRAM芯片,濾波器運行正常,存儲和播放聲音效果良好,播放無失真。本設計實現了AK4450和SDRAM在FPGA上的應用及FIR濾波器的算法,提出了一種非DSP或單片機應用的做法,提高了系統運行速度,節約了空間和成本。

[1]潘松、王國棟.VHDL實用教程.電子科技大學出版社,2001.7

[2]ALTERA SDR SDRAM Controller White Paper. http://www.altera.com,2002