基于FPGA八位小型ALU的設計

陳燕鳳

摘 要:基于可編程邏輯器件FPGA和硬件描述語言VHDL的8位ALU的設計方法,該ALU單元有四個寄存器,其中三個為數據寄存器,一個為狀態寄存器。任意三個數據寄存器均可作為輸入操作數(操作數均為補碼)和輸出操作數。該ALU單元可實現左移、右移、加法、減法、乘法、與、或、非,指令的加載通過仿真代碼實現。

關鍵詞:FPGA;VHDL;ALU;算術邏輯運算

引言

目前FPGA技術正處于高速發展時期,新型芯片的規模越來越大,成本也越來越低,低端的FPGA已逐步取代了傳統數字元件,高端的FPGA不斷在爭奪ASIC市場份額。算術邏輯單元ALU應用廣泛,是芯片上可編程系統不可缺的一部分,本文利用VHDL語言在FPGA芯片上設計8位算術邏輯運算單元ALU,通過VHDL語言實現ALU的功能,并用MAXPLUSII軟件進行仿真。

一、設計概述

一種基于可編程邏輯器件FPGA和硬件描述語言的8位的ALU的設計方法。該ALU采用模塊設計方法,有寄存器模塊、控制模塊和顯示模塊組成,能實現8位無符號數的左移,右移,加,減,乘,與、或、非。該ALU在MAXPLUSII軟件環境下進行功能仿真。

二、設計工作原理

ALU中包含4個寄存器,其中A,B,C為8位數據寄存器,其中A,B寄存器為輸入數據寄存器,C為操作數寄存器。D為狀態寄存器。

輸入的第一組數據(運算數),存儲在寄存器A中;輸入的第二組數據(運算數),存儲在B中;數據的第三組數據存儲在C中,根據C存儲器的數值,決定操作數A,B的運算方式(000->左移,001->右移,010->加法,011->減法,100->乘法,101->與,110->或,111->非)。當C寄存器數據為000,001時,分別對寄存器A,B中的數值進行移位后輸出,狀態寄存器無變化。當C寄存器數據為101,110,111時,把A,B進行對應與,或,非操作,若運算結果為0,則改變狀態寄存器的值為0,若運算結果為非0值,狀態寄存器值不變。當C寄存器數據為010,011,100時,把A,B進行對應的加,減,乘運算,當運算結果為0,溢出,負數時,改變狀態寄存器數據,否則,狀態寄存器數值不變。

三、設計流程圖

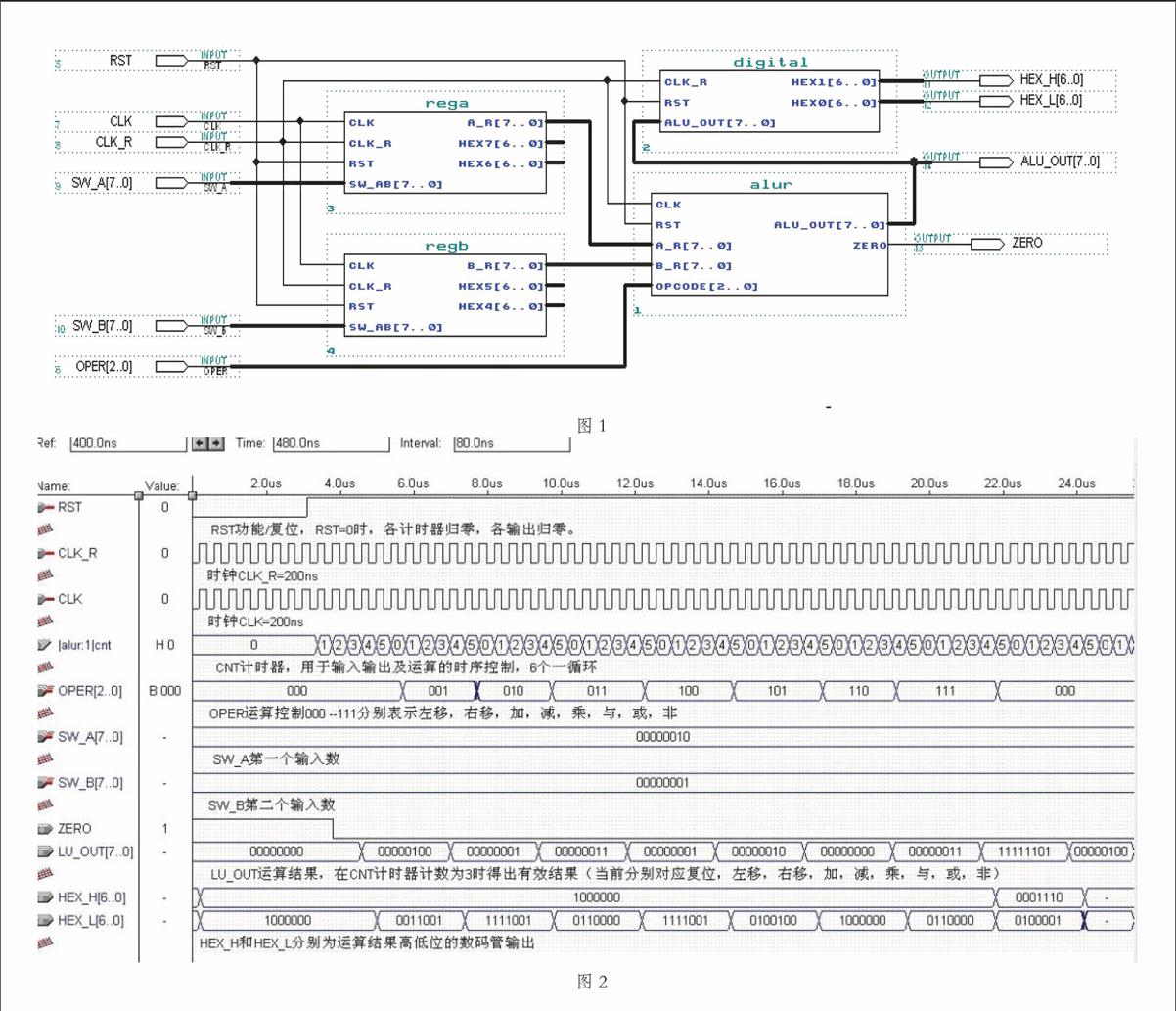

四、仿真實現

RST功能、復位,RST=0時,各計時器歸零,各輸出歸零。

時鐘CLK_R=200ns

時鐘CLK=200ns

CNT計時器,用于輸入輸出及運算的時序控制,6個一循環。

OPER運算控制000-111分別表示左移,右移,加,減,乘,與,或,非

SW_A第一個輸入數

SW_B第二個輸入數

LU_OUT運算結果,在CNT計時器計數為3時得出有效結果(當前分別對應復位,左移,右移,加,減,乘,與,或,非)。

HEX_H和HEX_L分別為運算結果高低位的數碼管輸出。

五、總結

本設計使用MAXPLUSII軟件進行仿真,通過仿真結果分析可以看出實現設計要求的功能,此運算器設計充分利用FPGA和VHDL語言的特點實現了ALU功能。隨著FPGA技術的發展,VHDL語言在硬件電路設計中,越來越顯示出其優勢,我們還可根據實際情況制定一個具有靈活性、可靠性和可擴展的,大于八位的ALU。

參考文獻:

[1]孔哲,王偉基于FPGA的32位ALU的設計與實現[J]信息技術,2013(12)

[2]張慶玲,楊勇FPGA原理與實踐[M]北京航空航天大學出版,2006