基于FPGA的CRC32校驗查找表算法的設計

時亞麗(中國電子科技集團公司第三十八研究所,合肥 230088)

基于FPGA的CRC32校驗查找表算法的設計

時亞麗

(中國電子科技集團公司第三十八研究所,合肥230088)

循環冗余碼校驗CRC廣泛應用于數字通信和數據存儲的數據檢錯。CRC校驗分為串行方式校驗、并行方式校驗。串行方式校驗采用串行移位寄存器,每1個clk計算1bit,處理速度慢。并行方式采用查找表算法,處理速度快。本文介紹了CRC32校驗算法的FPGA實現方法,并通過Modelsim仿真,驗證了算法的可行性和正確性。

循環冗余校驗碼;CRC32;FPGA

0 引言

循環冗余校驗碼CRC是一種實現簡單、校驗能力強、在串行通信領域廣泛采用的校驗編碼[1]。CRC校驗的基本思想是利用線性編碼理論,在發送端,對要傳送的k位二進制碼序列,以一定的規則產生一個校驗用的監督碼(即CRC碼)r位,附在信息后邊,構成了一個新的二進制碼序列數共(k+r)位,然后發送出去[2]。在接收端,則根據信息碼和CRC碼之間所遵循的規則進行校驗,以確定傳送中是否出錯。

1 CRC32生成查找表和CRC32數據校驗

CRC32校驗查找表算法采用正規查詢表查詢,該查詢表是將“直接查詢表”的索引值和表值直接鏡像,正規查找表多項式POLY是0x04C11DB7。生成查找表的流程是首先對索引值0到0xFF數值鏡像。以索引值1為例,鏡像值為0x80,已對該8bit鏡像值0x80左移24位變成32位CRC32值。對該值一次左移1位,移出的值若為1,則對移后的CRC32值與POLY進行異或操作得到新的CRC32值,否則不做運算。進行8次左移運算,最后的CRC32值在做鏡像后的值即為索引值1的CRC32查找表值,按照該算法進行256次操作,可得到256 個CRC32查找表值。

得到查找表后,則對數據進行CRC校驗,其校驗步驟是將待校驗數據與32位寄存器的低8位做XOR運算得到一個指向查詢表的索引值,將所將索引所指的表值與寄存器的高24位做XOR運算,得到的值更新到32位寄存器中,同時該值也為校驗過的值,如數據沒有全部處理完,則跳到開始進行運算。

2 FPGA硬件實現

FPGA實現CRC32校驗時,一種方法是校驗之前將CRC32生成的查找表值直接存入ROM中,按照索引值去取表內值。第二種方法是在校驗前根據算法生成CRC32的查找表值,依次存入RAM中,生成查找表之后再按照索引值去取表內值。本文是按照第二種方式進行校驗。這種方式的優點是靈活、易于操作。FPGA實現的流程圖如圖1所示,待校驗數據Din與CRC32低8位異或的值產生查找表的索引值,由于查找表是RAM存儲器,為了數據輸出穩定,輸出寄存一拍,從RAM出來的值會有兩拍延遲。Din數據寄存一拍,CRC32數據輸出寄存一拍,共有4拍數據延遲,所以CRC32會比串行校驗提高8倍時鐘周期。

圖1 FPGA實現CRC32校驗的流程圖

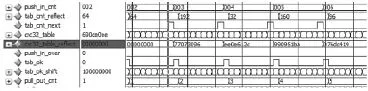

生成查找表值代碼段如下,其中tab_cnt_next一個周期的高電平將tab_cnt_refl ect鏡像值更新到crc32_table,ulPolynomial是校驗多項式值32'h04C11DB7,循環256次,并將256個crc32_table值鏡像之后存入RAM中。

if(tab_cnt_next==1'b1)

crc32_table <={tab_cnt_refl ect,24'h0};

else if(crc32_table[31]==1'b1)

crc32_table <={crc32_table[30:0],1'b0}^ulPolynomial;

else crc32_table <={crc32_table[30:0],1'b0};

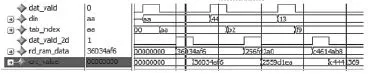

對Din數據進行校驗的主要代碼如下,dat_valid是一個周期的高電平,crc_value初始值為0,tab_index是RAM的讀地址,兩拍后從RAM讀的值rd_ram_data和crc_value高24位異或更新到新的crc_ value值。

if(dat_valid==1'b1)

tab_index <=crc_value[7:0]^din;

else if(dat_valid_2d==1'b1)

crc_value <=rd_ram_data ^crc_value[31:8];

3 CRC32的仿真驗證

CRC32生成查找表要循環256次完成查找表所有值的遍歷,其用Modelsim仿真如圖2所示,crc32_table的鏡像值crc32_table_ refl ect即為查找表的值,圖2中顯示的32’h0、32’h 77073096、32’hEE0E612C、32’h 990951BA即為CRC32正規查詢表值0到3的值。選取待校驗值0xAA,0x44,0x13其CRC32校驗值crc_value如圖3所示,最后一個值0xc4441369即為校驗值,經驗證正確。

圖2 CRC32生成查找表的Modelsim仿真圖

圖3 CRC32校驗的Modelsim仿真圖

4 結束語

本文介紹了CRC32校驗算法的FPGA實現方法,詳細介紹了CRC32查找表的生成、CRC32的數據校驗,并列出了FPGA實現的verilog代碼和仿真時序圖。經過驗證可以證明此方法的可行性,并提高了CRC32校驗的速率。

[1]葉懋,劉宇紅,劉橋.CRC碼的FPGA實現[J].重慶工學院學報(自然科學版),2007(03).

[2]莫元勁,黃水永.并行CRC在FPGA上的實現[J].電子設計工程,2011(15).

10.16640/j.cnki.37-1222/t.2016.10.188

時亞麗(1988-),女,安徽合肥人,碩士,助理工程師。