基于FPGA的多功能數(shù)據(jù)采集系統(tǒng)設(shè)計

劉歡,朱建鴻

(江南大學(xué) 輕工過程先進(jìn)控制教育部重點實驗室,江蘇 無錫 214122)

基于FPGA的多功能數(shù)據(jù)采集系統(tǒng)設(shè)計

劉歡,朱建鴻

(江南大學(xué) 輕工過程先進(jìn)控制教育部重點實驗室,江蘇 無錫 214122)

介紹了一種高速實時數(shù)據(jù)采集系統(tǒng)的設(shè)計,該系統(tǒng)以FPGA作為邏輯控制的核心,以USB作為與上位機數(shù)據(jù)傳輸?shù)慕涌冢瑑?nèi)置一路AD轉(zhuǎn)換,最高采樣速率40 MHz,預(yù)留40針I(yè)DE接口,可以擴展各種不同的傳感器與AD板,數(shù)據(jù)傳輸速度超過40 MB/s。給出了系統(tǒng)內(nèi)部結(jié)構(gòu)設(shè)計圖,設(shè)計思路、實施過程、仿真結(jié)果和實驗結(jié)果、固件(Firmware)和基于C#的應(yīng)用程序開發(fā),以期為各種傳感器的調(diào)試與數(shù)據(jù)采集等提供有益的參考。

電子設(shè)計;數(shù)據(jù)采集;傳感器;電壓轉(zhuǎn)換;USB;FPGA

傳統(tǒng)的數(shù)據(jù)采集系統(tǒng)中通常采用單片機或DSP作為控制模塊,控制AD轉(zhuǎn)換、存儲和其它外圍電路的工作,利用串口、并口等接口與上位機進(jìn)行通信。但隨著數(shù)據(jù)采集對速度、簡易性和精確度的要求日益增加,傳統(tǒng)的數(shù)據(jù)采集系統(tǒng)逐漸無法滿足應(yīng)用要求。

PCI接口[1]、SATA接口[2]和USB接口[4]是高速數(shù)據(jù)采集與傳輸領(lǐng)域三大主流選擇,但本文采用了USB2.0接口,因為USB2.0穩(wěn)定性高、通用性好、兼容性強和速度快。基于FPGA的多功能高速實時數(shù)據(jù)采集系統(tǒng)采用了FPGA邏輯主控和USB2.0傳輸?shù)乃悸贰PGA芯片具有體積小、頻率高、延時小,且能夠使用Verilog HDL語言來編程的優(yōu)點。本系統(tǒng)結(jié)合了兩者的優(yōu)點,具有速度快、容易拓展的特點。

1 系統(tǒng)總體結(jié)構(gòu)

本文設(shè)計的基于FPGA的多功能數(shù)據(jù)采集系統(tǒng)采用FPGA芯片作為系統(tǒng)的控制核心,通過USB2.0端口與上位機通信,實現(xiàn)多功能、實時的高速數(shù)據(jù)采集。本采集系統(tǒng)劃分為采集驅(qū)動電路、FPGA采集控制電路和USB傳輸控制電路等部分。如圖1所示。

圖1 數(shù)據(jù)采集系統(tǒng)整體框圖

本系統(tǒng)內(nèi)置1路模擬信號輸入,含12bit的AD轉(zhuǎn)換器,最高采樣率為 40 MHz,適合用于 CCD (Charge Coupled Device,電荷耦合器件)等圖像傳感器的數(shù)據(jù)采集。本數(shù)據(jù)采集系統(tǒng)支持外置擴展采樣接口 (IDE接口),此接口由CPLD驅(qū)動,起到多路電壓轉(zhuǎn)換的功效,能兼容5 V或3.3 V的系統(tǒng)或傳感器。該系統(tǒng)的工作過程為:主機應(yīng)用程序向USB控制器發(fā)出采樣控制包,在控制包中設(shè)置采集頻率、傳感器時序驅(qū)動等,進(jìn)而USB控制器觸發(fā)FPGA驅(qū)動傳感器并采樣,F(xiàn)PGA根據(jù)控制包的要求驅(qū)動AD進(jìn)行數(shù)模轉(zhuǎn)換,邊轉(zhuǎn)換邊將數(shù)據(jù)緩存到SDRAM,數(shù)據(jù)達(dá)到一定域值后,被打包傳送至USB控制器,再由USB控制器將數(shù)據(jù)高速傳送至上位機處理。

2 主要芯片選型

本數(shù)據(jù)采集系統(tǒng)采用的主要芯片包括FPGA芯片、CPLD芯片、AD轉(zhuǎn)換芯片和USB傳輸芯片。

依據(jù)本系統(tǒng)設(shè)計的需要選用Altera公司的Cyclone IV系列EP4CE15F17C8芯片。該芯片內(nèi)部集成邏輯單元15 408個,用戶I/O口165個,PLL(鎖相環(huán))4個,系統(tǒng)時鐘頻率可高于200 MHz,能滿足設(shè)計的要求。

根據(jù)電壓要求,本系統(tǒng)采用Altera公司的MAX II系列EMP240T100C5芯片[5]。該芯片具有80個通用 I/O口,支持1.8 V、2.5 V、3.3 V和5 V等多種電壓輸入輸出,能滿足設(shè)計需求。

根據(jù)采集系統(tǒng)的采樣率、分辨率等要求,本系統(tǒng)選用Analog Devices公司的AD9924模數(shù)轉(zhuǎn)換器件。該器件是12位低功耗高速并行模數(shù)轉(zhuǎn)換器件,最高采樣率為40 MHz。

Cypress公司的EZ-USB FX2系列芯片是一款集成了USB2.0協(xié)議的微處理器。本文采用了EZ-USB FX2LP系列低功耗芯片中的CY7C68013A-56(下文簡稱為EZ-USB)。

3 系統(tǒng)硬件設(shè)計

3.1多功能數(shù)據(jù)采集電路設(shè)計

傳感器的驅(qū)動電壓與AD芯片的輸出電壓常為5 V或 3.3 V,如SONY ILX554B CCD和TOSHIBA TCD1304DG CCD的傳感器驅(qū)動電壓分別為5 V和3.3 V;AD9220與AD9224模數(shù)轉(zhuǎn)換芯片的輸出電壓分別為5 V和3.3 V。這些信號都要與主控芯片相連。為了信號能夠被準(zhǔn)確捕捉,需要進(jìn)行電壓轉(zhuǎn)換,以往常使用專用的電壓轉(zhuǎn)換芯片,如SN74LVC4245,可以實現(xiàn)8路3.3 V與5 V的相互轉(zhuǎn)換,但這類芯片體積大,轉(zhuǎn)換通道少,在通道需求大、PCB空間小的情況下對電路設(shè)計者非常不利。

本系統(tǒng)選用CPLD(EPM240T100C5)通過軟件硬件結(jié)合控制實現(xiàn)多功能數(shù)據(jù)采集,如圖2所示,其中U1為CPLD部分I/O口,S1為四路硬件開關(guān),R1-R4為上拉電阻,P1為40針通用IDE接口。CPLD部分I/O口與IDE接口相連,I/O口與FPGA相連(圖中未畫出),通過編程實現(xiàn)各個I/O口之間的同步,然后通過QUATAUS II對CPLD I/O口輸入輸出模式進(jìn)行設(shè)定,并配合硬件開關(guān)控制上位電阻的閉合來實現(xiàn)I/O口的電壓轉(zhuǎn)換,實現(xiàn)4個8位I/O口分別以3.3 V和5 V獨立輸入輸出,還有一個8位I/O口(其中一位已被內(nèi)置AD輸入占用)直接與FPGA相連,可以進(jìn)行3.3 V的輸入輸出。具體實現(xiàn)過程分為4種情況(4個I/O口同理,以PA口為例):

圖2 多功能數(shù)據(jù)采集的連接

①PA口3.3V輸出,此時設(shè)置對應(yīng)的CPLD I/O口為普通輸出模式,斷開S1第一位,再通過程序?qū)崿F(xiàn)該I/O口與FPGA對應(yīng)的I/O口時序同步。

②PA口5V輸出,此時設(shè)置對應(yīng)的CPLD I/O口為開漏輸出模式,閉合S1第一位(加上拉電阻),再通過程序?qū)崿F(xiàn)該I/O口與FPGA對應(yīng)的I/O口時序同步。

③PA口3.3 V輸入,此時設(shè)置對應(yīng)的CPLD I/O口為普通輸入模式,斷開S1第一位,再通過程序?qū)崿F(xiàn)FPGA對應(yīng)的I/O口與該I/O口時序同步。

④PA口5 V輸入,此時設(shè)置同③,EPM240T100C5產(chǎn)品手冊表明,當(dāng)VCCIO=3.3 V時,能兼容5 V TTL輸入信號,AD數(shù)模轉(zhuǎn)換芯片輸出信號一般均為TTL信號,能兼容。

3.2FPGA與SDRAM及USB芯片連接電路設(shè)計

本系統(tǒng)采用SDRAM(同步動態(tài)隨機存儲器)代替?zhèn)鹘y(tǒng)的FIFO進(jìn)行數(shù)據(jù)緩存,此為兩級數(shù)據(jù)緩沖的第一級,兩片SDRAM輪流操作,進(jìn)行通常所說的乒乓操作[8]。SDRAM型號為H57V2562GTR-75C,單片容量為32 M(普通FIFO芯片的容量一般為32~512K),價格較貴,但從容量的角度來考慮,SDRAM存在明顯優(yōu)勢。SDRAM由FPGA控制讀寫,用來暫存AD電路所產(chǎn)生的數(shù)據(jù)。

EZ-USB有多種數(shù)據(jù)傳輸模式,如GPIF模式、SLAVE FIFO模式等,甚至端口模式都可以進(jìn)行數(shù)據(jù)傳輸。其中傳輸速度最快的是SLAVE FIFO模式,可以達(dá)到40 MB/S。

當(dāng)EZ-USB工作于SLAVE FIFO模式時,外圍電路可以像對待普通FIFO一樣對EZ-USB內(nèi)部FIFO進(jìn)行讀寫[7],此為兩級數(shù)據(jù)緩沖的第二級。本系統(tǒng)采用FPGA作為主控制器,USB控制器采用SLAVE FIFO模式,F(xiàn)PGA通過控制EZUSB內(nèi)部FIFO及SDRAM進(jìn)行與上位機之間的數(shù)據(jù)傳輸。

FPGA與SDRAM及USB芯片信號連接圖如圖3所示。其中,在與SDRAM連接中,A[0..12]為13位地址位,DQ[0..15]為16位輸入輸出數(shù)據(jù)位,INCLK_SD為FPGA PLL鎖相環(huán)二倍頻產(chǎn)生的100MHz時鐘信號,是SDRAM的主時鐘信號,其它為控制信號;在與EZ-USB的連接中,data[0..15]為16位數(shù)據(jù)位,其它為控制信號或狀態(tài)位。

圖3 FPGA與SDRAM及USB芯片信號連接圖

4 系統(tǒng)軟件設(shè)計

系統(tǒng)軟件設(shè)計主要包括FPGA邏輯控制程序設(shè)計、CPLD程序設(shè)計、USB固件程序設(shè)計和上位機應(yīng)用程序設(shè)計。

4.1FPGA邏輯控制設(shè)計

FPGA邏輯控制程序的設(shè)計是整個數(shù)據(jù)采集系統(tǒng)的關(guān)鍵,整體分成三大模塊:PLL鎖相環(huán)模塊、分頻采樣控制模塊和NIOS II主控模塊。本設(shè)計中使用QUARTUS II提供的IP核進(jìn)行編程,降低了開發(fā)的難度并縮短了開發(fā)周期。FPGA邏輯控制模塊化設(shè)計原理圖如圖4所示,上文已提及的外設(shè)連接也在圖中顯現(xiàn)。

圖4 FPGA模塊化設(shè)計原理圖

4.1.1PLL鎖相環(huán)模塊

NIOS II內(nèi)核和SDRAM的時鐘頻率高于FPGA的主時鐘50 MHz,因此,本系統(tǒng)采用PLL鎖相環(huán)的倍頻功能來提升時鐘頻率到100 MHz,從而驅(qū)動NIOS II內(nèi)核和SDRAM。PLL鎖相環(huán)模塊的建立既可以通過Verilog HDL直接編寫,還可以通過QUARTUS II提供的IP內(nèi)核來設(shè)置。本文采用后者,具有方便、便捷的優(yōu)點。如圖4中PLL模塊所示。

4.1.2分頻采樣控制模塊

FPGA主時鐘由50 MHz有源晶振提供,由于A/D采樣的頻率要根據(jù)實際頻率需求設(shè)定500 KHz~40 MHz,因此需要構(gòu)建分頻采樣控制自定義模塊,該模塊對主時鐘進(jìn)行若干分頻得到相應(yīng)的驅(qū)動同步信號。同時,該模塊還要控制數(shù)據(jù)采樣、AD轉(zhuǎn)換以及數(shù)據(jù)同步存儲。如圖4中driver_times模塊所示,其中CCD_ROG、CCD_CLK分別是傳感器驅(qū)動信號,AD_CLK是ADC芯片的主時鐘信號并作為NIOS II內(nèi)核的輸入信號為數(shù)據(jù)存儲提供同步信號。

4.1.3NIOS II主控模塊

NIOS II主控模塊主要分為 USB傳輸控制部分和SDRAM緩存控制部分,它們在數(shù)據(jù)和功能上有連通性,所以把它們集成在一個內(nèi)核模塊中,如圖4中KERNEL模塊所示。NIOS II同時也是一個IP內(nèi)核[9],它的作用相當(dāng)于一個32 位RISC嵌入式處理器。嵌入式開發(fā)所采用的高級語言C語言相對于FPGA的Verilog HDL或是VHDL等硬件描述語言具有開發(fā)難度低,邏輯明確等優(yōu)點。采用嵌入式內(nèi)核之后并沒有損失FPGA的并行執(zhí)行能力,一個工程中可以建立多個內(nèi)核,依然有并行執(zhí)行程序的能力,相當(dāng)于多個內(nèi)核同時工作,F(xiàn)PGA加ARM組合形式,使得代碼執(zhí)行效率更高。

1)SDRAM緩存控制

如圖4所示,在KERNEL軟核中已經(jīng)建立了兩個SDRAM控制器,SDRAM控制器一旦構(gòu)建好,接下來對SDRAM的處理就像對內(nèi)部RAM地址一樣進(jìn)行賦值和讀取。32MB的SDRAM中除了NIOS II系統(tǒng)的運行占用了少量空間(8KB),其余均可用于數(shù)據(jù)存儲。用C語言中的指針操作可以輕松的完成SDRAM的讀寫工作,下面給出實現(xiàn)ADC轉(zhuǎn)換出的數(shù)據(jù)存儲到SDRAM0的關(guān)鍵代碼:

unsigned short*ram0=(unsigned short*)(SDRAM_BASE+ 0x10000);//SDRAM地址

void save_data_0()

{

memset(ram0,0,16000000);//內(nèi)存初始化

while(Coll_State)

{

if(AD_CLK)

*(ram0++)=ADC_ONE_DATA;

}

}

數(shù)據(jù)總線為16位,所以每存儲一個數(shù)據(jù),指針向后移動一次(16位),由系統(tǒng)內(nèi)部自動處理完成,數(shù)據(jù)的地址不需要人工干預(yù)。從SDRAM0中讀出數(shù)據(jù)也是如此,下面給出了從SDRAM0讀出數(shù)據(jù)送至EZ-USB數(shù)據(jù)IO口的關(guān)鍵代碼:

void read_data_0()

{

while(!flagb)

{

if(!ifclk)

CY->DATA=*(--ram0);

}

}

其中CY->DATA是用結(jié)構(gòu)體定義的IO口,ifclk為EZUSB的IO口時鐘。

SDRAM1的工作過程與SDRAM0相同,兩塊SDRAM交替工作,在向一塊SDRAM存入數(shù)據(jù)的同時,從另一塊SDRAM讀出數(shù)據(jù),以保證數(shù)據(jù)的高速穩(wěn)定傳輸。

2)USB傳輸控制

本系統(tǒng)采用KERNEL軟核通過判斷端點FIFO的空、滿標(biāo)志位 (FLAGB、FLAGC)來對EZ-USB端點2、4、6、8進(jìn)行讀、寫控制,并采用異步FIFO讀寫控制模式,控制程序流程圖如圖5所示。

4.2CPLD程序設(shè)計

本設(shè)計中,CPLD主要用于電壓轉(zhuǎn)換,其實現(xiàn)原理是通過CPLD的邏輯單元把FPGA對傳感器的驅(qū)動信號做一個同步輸入輸出(從一個I/O口接收,送至另一個I/O輸出),再通過外部硬件電路的配置,使其驅(qū)動電壓升高或降低。其中,CPLD I/O口的模塊(推挽、開漏)通過QUARTUS II工程進(jìn)行定義。

圖5 FPGA異步FIFO讀寫控制流程圖

4.3USB固件程序設(shè)計

USB固件是運行在 EZ-USB芯片中的代碼。SLAVE FIFO模式中,固件的功能配置了SLAVE FIFO相關(guān)的寄存器以及控制EZ-USB何時工作在SLAVE FIFO模式下,一旦固件將相關(guān)的寄存器配置完畢,F(xiàn)PGA即可按照SLAVE FIFO的傳輸時序控制EZ-USB與主機進(jìn)行高速通信,而在通信過程中不需要EZ-USB芯片中8051單片機的干預(yù),從而保證足夠的數(shù)據(jù)傳輸速率。固件程序采用Cypress公司提供的固件框架,添加自己的配置代碼[6]。添加的部分如下:

Void TD_Init(void)

{...

IFCONFIG=0x03;//設(shè)置外部時鐘源、slave fifo模式

EP2CFG=0xA2;//2端點OUT、批量傳輸、512字節(jié)雙緩沖

EP4CFG=EP6CFG=EP8CFG=0xE2;//4,6,8端點IN、批量傳輸、512字節(jié)雙緩沖

AUTOPTRSETUP|=0x01//使用自動指針

....}

在上面程序中,定義了2端點為上位機命令字下傳通道,4、6、8端點為采集數(shù)據(jù)上傳通道,均設(shè)置為批量傳輸、512字節(jié)雙緩沖。

4.4上位機應(yīng)用程序設(shè)計

上位機應(yīng)用程序的作用是提供一個人機交互的顯示界面,進(jìn)行實時數(shù)據(jù)交換,反映系統(tǒng)的運行狀態(tài)并存儲下位機的采集數(shù)據(jù)。該系統(tǒng)采用Visual Studio 2013進(jìn)行上位機C#應(yīng)用程序的設(shè)計,程序中采用Cypress公司提供的CYAPI控制函數(shù)類配合適當(dāng)?shù)尿?qū)動程序完成整個上下位機的通訊過程。

5 系統(tǒng)測試

本文對系統(tǒng)做了3個方面的測試,分別是驅(qū)動時序仿真、NIOS II主控邏輯仿真和USB傳輸速度測試。

5.1驅(qū)動時序仿真

以SONY ILX554B CCD為例,對傳感器驅(qū)動時序的產(chǎn)生進(jìn)行了仿真,時序圖如圖6所示。

圖6 驅(qū)動時序仿真

5.2NIOS II主控邏輯仿真

由于ModSim只能對FPGA本體進(jìn)行時序仿真,無法對SDRAM、EPCS這些存儲類外設(shè)進(jìn)行仿真,故將存儲器換成OnChip Memory,只進(jìn)行功能性的仿真。仿真圖如圖7所示。其中,數(shù)據(jù)來源于TestBench(激勵)文件中產(chǎn)生的隨機數(shù),由于AD為12位,故輸入隨機數(shù)為12位,以16位的形式存儲,再由16根數(shù)據(jù)線傳送至EZ-USB。如圖7所示,前一段為數(shù)據(jù)采集,后一段為數(shù)據(jù)傳送,用指針操作,數(shù)據(jù)是逆向讀出。

圖7 NIOS II主控邏輯仿真

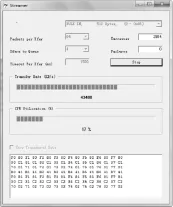

5.3USB傳輸速度測試

該測試采用Cypress官方提供的測速工具-Streamer,如圖8所示,電路板實測USB傳輸速度超過40 MB/S,能夠滿足高速采集速度需求。

圖8 USB速度測試

6 結(jié)束語

系統(tǒng)開發(fā)過程中涉及硬、軟件混合設(shè)計,Verilog HDL與C語言的混合編程以及NIOS II內(nèi)核仿真等綜合技能和全面的軟、硬件知識。本文實現(xiàn)了一種支持多種傳感器的多功能采集系統(tǒng),該系統(tǒng)支持大容量緩存和高速USB傳輸。經(jīng)長時間測試,系統(tǒng)工作穩(wěn)定,性能可靠,說明了設(shè)計的合理性,比較適合各種傳感器的調(diào)試與數(shù)據(jù)采集等。

[1]程敏,翁寧泉,劉慶,等.基于PCI-1002的高速數(shù)據(jù)采集[J].大氣與環(huán)境光學(xué)學(xué)報,2014,9(4):310-315.

[2]張志煒,呂幼新.基于SATA硬盤和FPGA的高速數(shù)據(jù)采集存儲系統(tǒng)[J].電子設(shè)計工程,2011,19(21):166-169.

[3]李露,段新文.基于FPGA的高速數(shù)據(jù)采集卡的設(shè)計[J].現(xiàn)代電子技術(shù),2012,35(18):146-148.

[4]王選擇,曾志祥,范宜艷,等.基于FPGA與USB2.0的溫度數(shù)據(jù)采集與控制[J].儀表技術(shù)與傳感器,2014(9):44-47.

[5]宗發(fā)保,郭昌華,杜偉寧.基于EPM240和MSP430的等精度頻率計[J].吉林大學(xué)學(xué)報:信息科學(xué)版,2012,30(5):492-496.

[6]張思杰,趙泰,汪振興,等.基于FPGA的USB接口數(shù)據(jù)采集系統(tǒng)設(shè)計[J].電子技術(shù)應(yīng)用,2011,37(5):98-100.

[7]劉志華,郭付才,彭新偉,等.基于CY7C68013A的FPGA配置和通信接口設(shè)計[J].電子技術(shù)應(yīng)用,2013,39(2):18-21.

[8]張傳勝.基于FPGA/SOPC架構(gòu)的面陣CCD圖像采集系統(tǒng)的設(shè)計[J].液晶與顯示,2011,26(5):636-639.

[9]薛飛,寧鐸,黃建兵.基于SOPC圖像采集系統(tǒng)的設(shè)計[J].儀表技術(shù)與傳感器,2012(12):49-51.

[10]代月松,裴東興,徐菲.USB在數(shù)據(jù)采集系統(tǒng)中的應(yīng)用[J].電子測試,2012(8):64-67.

Design of multifunction data acquisition system based on FPGA

LIU Huan,ZHU Jian-hong

(Key Laboratory of Advanced Process Control for Light Industry,Ministry of Education,Jiangnan University,Wuxi 214122,China)

The design of a high-speed real-time data acquisition system with the FPGA as a core logic control is introduced. The system has the following characteristics:using USB2.0 as data transfer interface to the host computer,building in an AD conversion,the maximum sampling rate 40 MHz,40-pin IDE reserved for interface,expansion of a variety of sensors and AD board,and data transmission speed being over 40 MB/S.The internal structure design of the system,design ideas, implementation,simulation and experimental results,and the firmware and application based on C#are given for a variety of sensors to provide a useful reference for debugging and data acquisition.

electronic design;data acquisition;sensor;voltage conversion;USB;FPGA

TN919.6

A

1674-6236(2016)13-0167-05

2015-07-15稿件編號:201507112

劉 歡(1991—),男,湖北天門人,碩士研究生。研究方向:檢測與傳感。