低功耗帶隙基準電壓源電路設計

蔣本福

(吉林大學 珠海學院,廣東 珠海 519000)

低功耗帶隙基準電壓源電路設計

蔣本福

(吉林大學 珠海學院,廣東 珠海 519000)

文章提出一種三層self-cascode管子工作在亞閾值區的低功耗帶隙基準電壓源電路。該電路具有電路結構簡單、功耗低、溫度系數小、線性度小和面積小等特點。采用CSMC 0.18 μm的標準CMOS工藝,華大九天Aether軟件驗證平臺進行仿真。仿真結果表明,在tt工藝角下電路的啟動時間為6.64 μs,穩定輸出的基準電壓Vref為 567 mV;當溫度在-40℃~125℃范圍內時,tt工藝角下基準電壓Vref的溫度系數TC為18.8 ppm/℃;電源電壓在1.2 V~1.8 V范圍內時,tt工藝角下基準電壓Vref的線性度為2 620 ppm/V;在10 Hz~1 kHz帶寬范圍內,tt工藝角下基準電壓Vref的電源抑制比(PSRR)為51 dB;版圖核心面積為0.001 95 mm2。

Aether軟件;功耗; 溫度系數;線性度;面積

0 引言

在模擬IC和混合IC中,帶隙基準電壓是不可缺少的電路模塊。傳統的低壓、低功耗帶隙基準電路是基于垂直雙極晶體管,在文獻[1-2]中分別提出了多種設計方法。然而,這些方法都需要幾百兆歐姆的電阻實現低功耗運行,占用較大芯片面積,浪費資源。參考文獻[3]也提出了由幾個工作在亞閾值區的MOS管組成的電路,雖然保證了低功耗,但是也出現了溫度補償不夠等問題。為了實現低溫漂帶隙基準電壓電路,高階溫度補償技術[5]必須得到廣泛應用,以減小帶隙電壓的溫度系數。因此本文提出在低功耗的帶隙基準基礎上增加高階溫度補償電路來實現低溫漂基準電壓電路。

1 電路結構分析

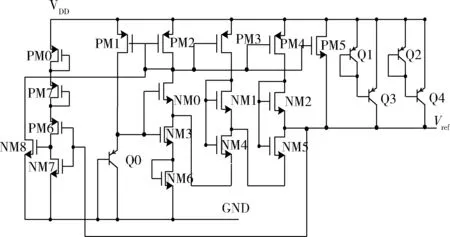

電路原理圖如圖1所示,主要由啟動電路[4]、電流產生電路[5]和self-cascode[4-5]自偏置電路三部分組成。其中NM0~NM6這7個NMOS管均工作在亞閾值區,電流鏡PM1~PM5這5個PMOS管均工作在飽和區。啟動電路由PM0、PM6、PM7、NM7和NM8組成,當電路開始工作時,它將提供一個啟動電流,使電路進入正常工作狀態。電路正常輸出電壓后,由Vref提供一個反饋使NM7進入線性區,從而令NM8、PM6截止,使啟動電路關斷,以減小功耗。電流產生電路由Q0、PM1、PM2、NM3和NM6組成,其中NM3、NM6具有相同的W/L,使得VGSN3=VGSN6=VE/2,對Q0形成一個鉗位的作用。通過調整NM3、NM6的W/L,可產生一個穩定的nA級電流。Self-cascode自偏置電路由NM0~NM3,NM1~NM4,NM2~NM5組成,利用這種結構可產生一個PTAT電壓VPTAT[5]。因為VGSN6[1]具有負的溫度特性,所以由VPTAT和VGSN6可產生一個與溫度無關的基準電壓Vref。

(1)

(2)

其中VDSN為NMOS的漏源電壓,VGSN為NMOS的柵源電壓,VE為BJT的發射極基極電壓,S為MOS管的寬長比比值,ΦT為熱電壓,n為亞閾值系數。

由于BJT的發射極基極電壓VE具有高階的溫度系數,因此采用圖1 Q1-Q3和Q2-Q4 部分構造指數型補償電路[5]。其中流經Q3、Q4 的集電極電流是一個與溫度成高階溫度關系的量,把這一電流引入帶隙基準源的輸出端可以對帶隙基準源進行高階的溫度補償。

圖1 電路原理圖

2 電路仿真結果

仿真采用CSMC 0.18 μm的標準CMOS工藝,華大九天Aether軟件驗證平臺,各種仿真與分析如下。

2.1 不同工藝角下的啟動電路仿真與分析

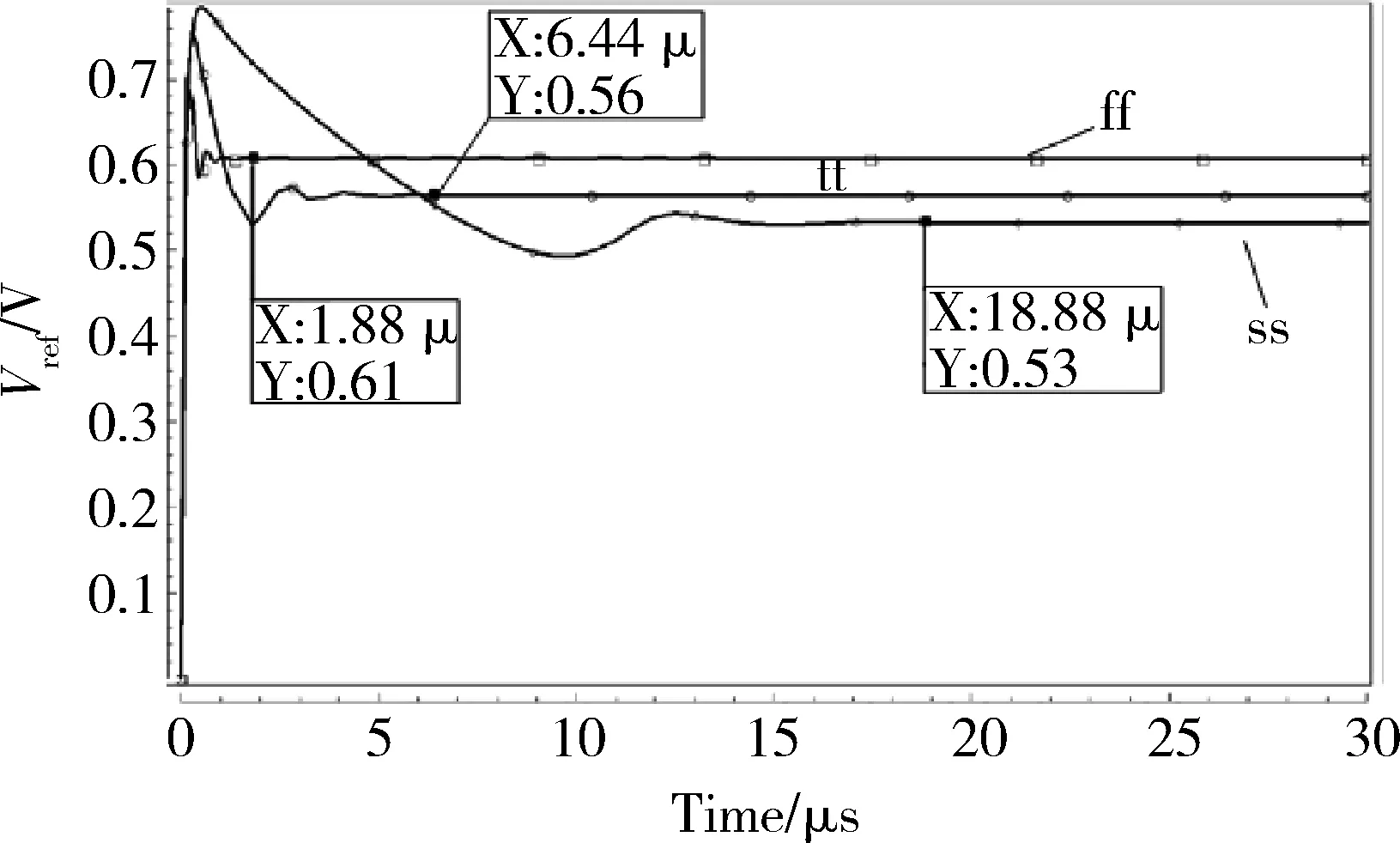

瞬態仿真,可得到基準電壓Vref穩定的建立時間,如圖2所示。

圖2 基準電壓Vref穩定的建立時間波形(ff tt ss)

由圖2可知,電路在不同工藝角下的啟動時間相差不大。

2.2 不同工藝角下的電路功耗仿真與分析

如圖3所示,各工藝角下電路的總電流分別為:ff 1.45 μA,tt 319.45 nA,ss 67.28 nA。

圖3 瞬態仿真:電路上電穩定后電路的總電流(ff tt ss)

由于在不同的工藝角下,MOS管具有不同的閾值電壓,BJT具有不同的導通電壓,使得在ff工藝角下部分工作在亞閾值區的管子進入飽和區,從而增大了基準電流,其中在ss工藝角下所有的電流鏡管子均進入亞閾值區。

因此,在不同工藝角下電路的總電流出現不同的變化,相應地也會對溫度系數產生一定的影響。

2.3 不同工藝角下的電路溫度特性曲線仿真與分析

2.3.1 基準電壓Vref溫度特性曲線仿真與分析

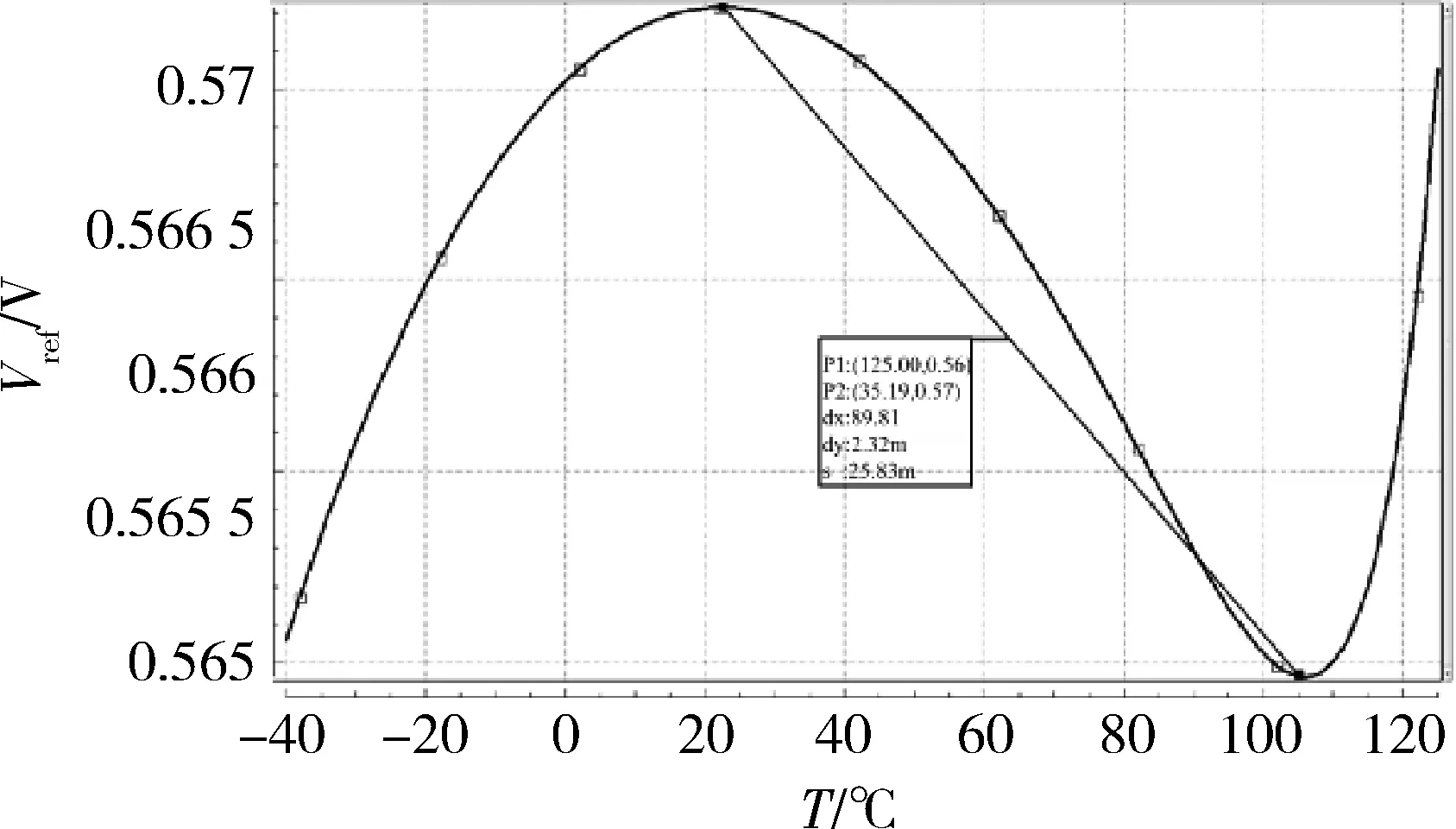

基準電壓Vref的溫度特性曲線如圖4所示,具體仿真結果與分析如下:

(1)溫度在-40℃~125℃范圍內時,tt工藝角下基準電壓Vref的溫度系數為18.8 ppm/℃;

(2)溫度在20℃~50℃范圍內時,tt工藝角下基準電壓Vref的溫度系數為4.0 ppm/℃。

圖4 基準電壓Vref溫度特性曲線 (tt)

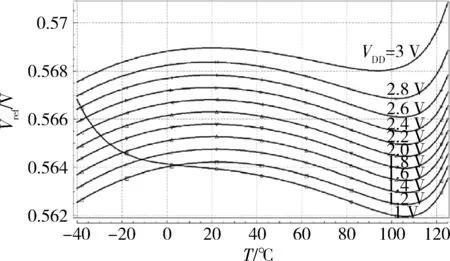

2.3.2 在不同的電源電壓下基準電壓Vref溫度特性曲線

如圖5所示,電源電壓在1 V~3 V范圍內,參數掃描具體仿真結果與分析如下:當電源電壓為1.2 V~2.8 V時,在-40℃~125℃溫度范圍內,tt工藝角下基準電壓Vref的溫度系數TC在18~21 ppm/℃之間。

圖5 在不同的電源電壓下,基準電壓Vref溫度特性曲線

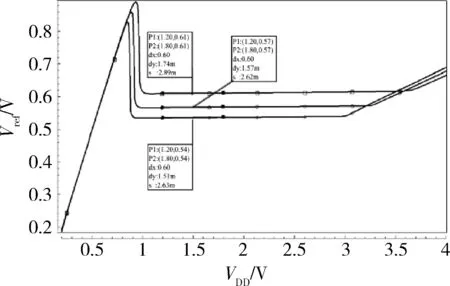

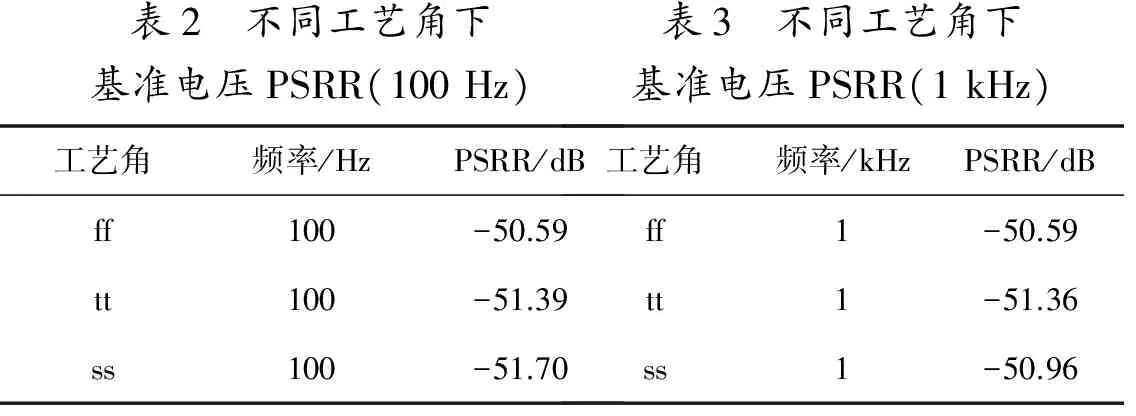

2.4 不同工藝角下的基準電壓的線性度仿真與分析

圖6所示為在0.2 V~4 V電源電壓內,3個工藝角的基準電壓Vref隨電源電壓變化曲線。

圖6 基準電壓Vref隨電源電壓變化曲線 (ff tt ss)

具體仿真結果與分析如表1所示。

表1 電路工作電源電壓范圍和基準電壓線性度

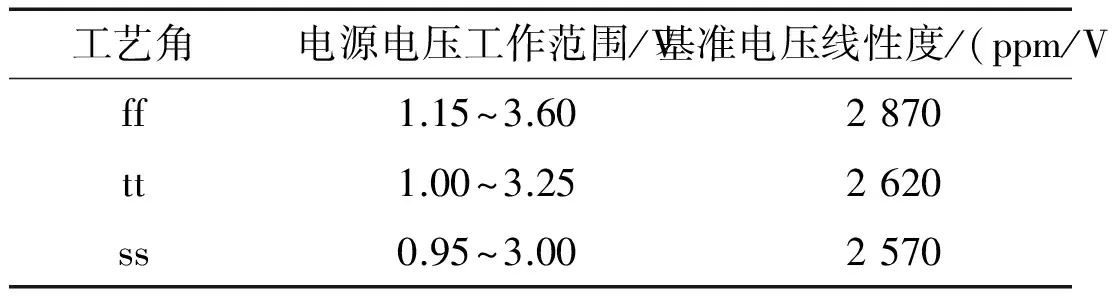

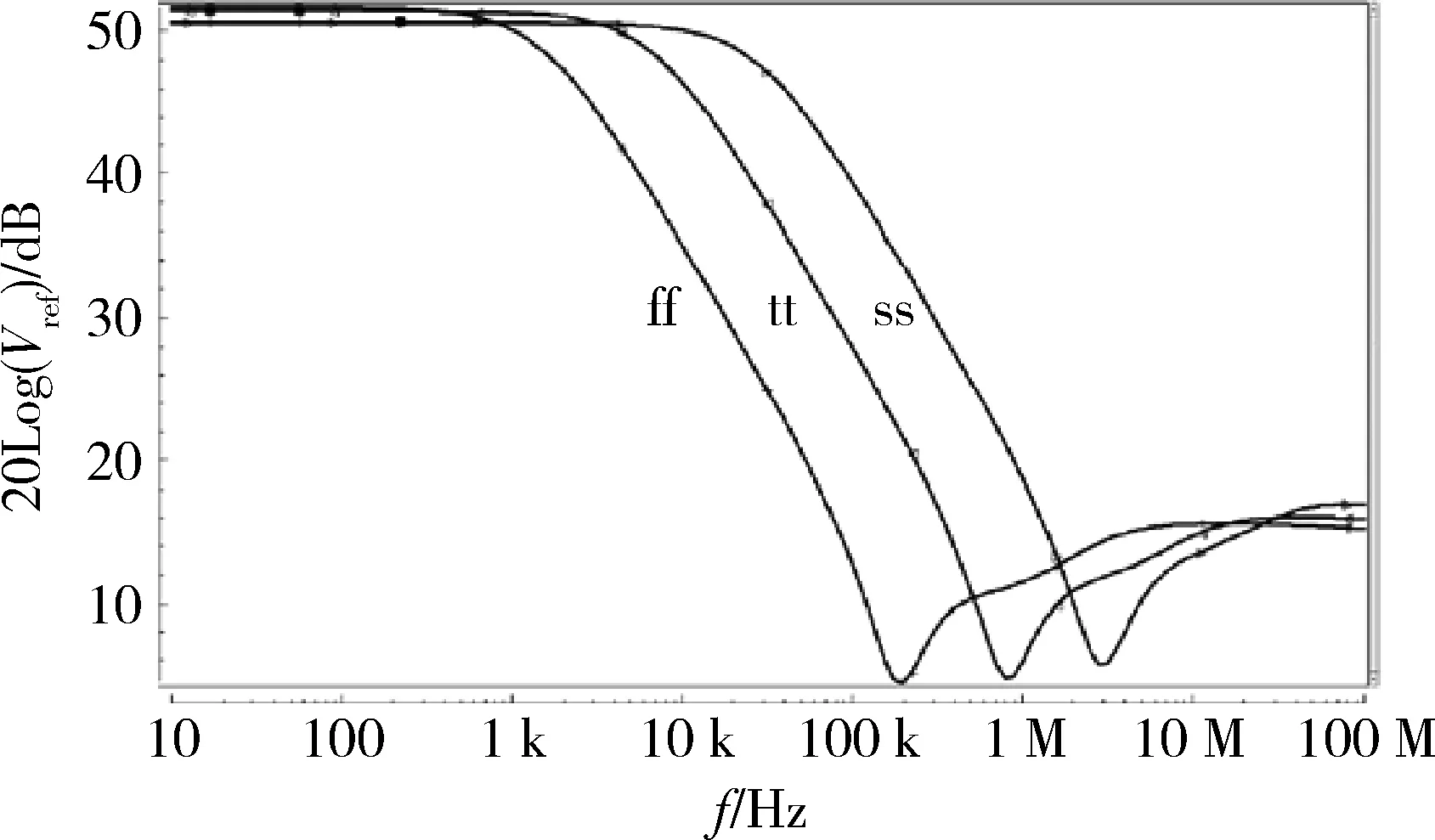

2.5 不同工藝角下的電路電源抑制比仿真與分析

如圖7所示,頻率在低頻范圍內,3個工藝角下基準電壓Vref的PSRR均大于50 dB。

圖7 基準電壓Vref的PSRR變化曲線 (ff tt ss)

具體仿真結果與分析如表2、表3所示。

表2 不同工藝角下基準電壓PSRR(100Hz)工藝角頻率/HzPSRR/dBff100-50.59tt100-51.39ss100-51.70表3 不同工藝角下基準電壓PSRR(1kHz)工藝角頻率/kHzPSRR/dBff1-50.59tt1-51.36ss1-50.96

由表2、表3可知,在10 Hz~1 kHz范圍內,基準電壓Vref在3個工藝角下的PSRR均在-51 dB左右。

由圖7可知,當頻率為10 kHz時,在ff和tt工藝角下基準電壓Vref仍具有-50 dB和-49 dB的PSRR。

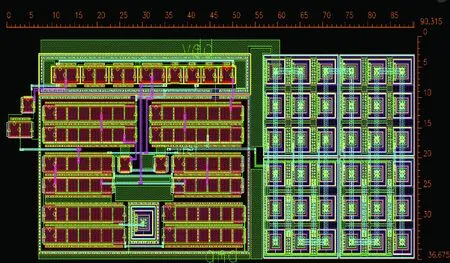

3 版圖設計

版圖的整體設計如圖8所示。

圖8 電路整體版圖設計

4 結論

本文設計了一款基于溫度補償的CMOS低壓、低功耗的帶隙基準電壓源。利用MOS管工作在亞閾值區域過驅動電壓低、飽和電流小的特性,能夠實現在輸入較低的電源電壓范圍內,功耗降低到nW級帶隙基準電路設計。同時,在輸出級增加溫度補償電路,提高電路的溫度補償能力。本電路還有電路結構簡單、功耗低、線性度好、溫度系數小、PSRR較好、芯片面積小等特點。

[1] UENO K, HIROSE T, ASAI T, et al.A 300 nw, 15 ppm/℃,20 ppm/v cmos voltage reference circuit consisting of subthreshold mosfets[J]. Solid-StateCircuits, IEEE Journal of, 2009,44(7):2047-2054.

[2] Li Yongquan, Jiang Mei. Ultra-low power CMOS multiple voltage reference with 3.9 ppm/℃ temperatutre coefficient[C]. ICCE-IW,2015.

[3] 陳新弼,張慶中,陳勇.微電子器件[M].北京:電子工業出版社,2011.

[4] SAINT C, SAINT J.集成電路掩膜設計[M]. 周潤德,金申美,譯.北京:清華大學出版社,2006.

[5] Alan Hastings.模擬電路版圖的藝術(第二版)[M].張為,等譯.北京:電子工業出版社, 2011.

Design of low power bandgap reference voltage source circuit

Jiang Benfu

(Zhuhai College, Jilin University, Zhuhai 519000, China)

This paper presents a low power bandgap reference voltage source circuit with three layers of self-cascode tubes operating in the sub threshold region. The circuit has the characteristics of simple structure, low power consumption, small temperature coefficient, small linearity and small area. Using the CSMC 0.18 μm standard CMOS process, Hua Da Jiu Tian Aether software verification platform to simulate, and the simulation results show that, in the corner of the TT process,the starting time of the circuit is 6.64 μs and the stabilizing output reference voltageVrefis 567 mV. When the temperature is in the range of -40℃ to 125℃,the reference voltageVreftemperature coefficient (TC) is 18.8 ppm /℃ at TT process; when the supply voltage is in the range of 1.2 V to 1.8 V,the reference voltageVreflinearity is 2 620 ppm/V at TT process ; when the bandwidth is in the range of 10 Hz to 1 kHz, the reference voltageVrefpower inhibition ratio (PSRR) is 51 dB at TT process; core area of territory for cross-section is 0.001 95 mm2.

Aether software; power consumption; temperature coefficient; linearity; area

TN432

A

10.19358/j.issn.1674- 7720.2017.03.012

蔣本福.低功耗帶隙基準電壓源電路設計[J].微型機與應用,2017,36(3):39-41.

2016-10-05)

蔣本福(1988-),男,碩士研究生,主要研究方向:模擬射頻集成電路設計。