基于FPGA的數(shù)字系統(tǒng)設(shè)計方法

王玉喜

哈爾濱智路科技開發(fā)有限公司

基于FPGA的數(shù)字系統(tǒng)設(shè)計方法

王玉喜

哈爾濱智路科技開發(fā)有限公司

FPGA(FiledProgrammableGateArray)是20世紀(jì)80年代中期出現(xiàn)的一種新概念—用戶現(xiàn)場可編程門陣列集成電路。PGA具有更多的門電路,體積小,成本低,并且方便隨時修改設(shè)計直至滿足實驗要求等優(yōu)點,目前FPGA也被廣泛應(yīng)用于通信、自動控制、信息處理等諸多領(lǐng)域,因此進一步加強對其的研究非常有必要。基于此本文分析了FPGA的數(shù)字系統(tǒng)設(shè)計方法。

FPGA;數(shù)字系統(tǒng);設(shè)計方法

1、現(xiàn)代數(shù)字系統(tǒng)的設(shè)計方法

隨著可編程器件的出現(xiàn)和計算機技術(shù)的發(fā)展,使EDA技術(shù)得到了廣泛應(yīng)用,設(shè)計方法也因此發(fā)生了根本性的變化。由傳統(tǒng)的“自底向上”的設(shè)計方法轉(zhuǎn)變?yōu)橐环N新的“自頂向下”的設(shè)計方法,其設(shè)計流程如下:第一步,進行行為設(shè)計,確定電子系統(tǒng)或ASIC芯片的功能、性能及允許的芯片面積和成本等。第二步,進行結(jié)構(gòu)設(shè)計,根據(jù)電子系統(tǒng)或芯片的特點,將其分解為接口清晰、相互關(guān)系明確、盡可能簡單的子系統(tǒng),得到一個總體結(jié)構(gòu)。第三步,把結(jié)構(gòu)轉(zhuǎn)化為邏輯圖,即進行邏輯設(shè)計。在這一步中,希望盡可能采用規(guī)則的邏輯結(jié)構(gòu)或采用已經(jīng)經(jīng)過驗證的邏輯單元或模塊。第四步,進行電路設(shè)計,將邏輯圖轉(zhuǎn)化為電路圖。最后一步是進行ASIC的版圖設(shè)計,即將電路轉(zhuǎn)換成版圖,或者用可編程ASIC實現(xiàn)。

2、FPGA的特點及設(shè)計軟件

FPGA通稱為可編程邏輯器件,它們都是在PLA,PAL 和GAL等邏輯器件的基礎(chǔ)上發(fā)展起來的,主要有Altera公司和Xilinx公司生產(chǎn)的系列產(chǎn)品。許多生產(chǎn)可編程器件的公司為了推廣它們產(chǎn)品都有自已的開發(fā)軟件,其中應(yīng)用較廣的有Altera 公司的MAX+pluaII 軟件,它有以下主要優(yōu)點: (1)開放的接口;(2)與結(jié)構(gòu)無關(guān)的設(shè)計開發(fā)環(huán)境,具有強大的邏輯綜合與優(yōu)化功能;(3)支持各種HDL輸入選項,支持VHDL硬件描述語言;(4)全集成化的輸入開發(fā)環(huán)境;(5)豐富的設(shè)計庫資源;(6)有豐富的在線幫助功能。因此特別適合初學(xué)者使用,可作為數(shù)字電路系統(tǒng)的設(shè)計和開發(fā)軟件。在指導(dǎo)學(xué)生進行課程設(shè)計時,應(yīng)先學(xué)習(xí)MAX+pluaII軟件和VHDL語言的編程方法,掌握CPLD/FPGA實驗開發(fā)系統(tǒng)的使用。

3、基于FPGA的數(shù)字系統(tǒng)設(shè)計方法

FPGA(Field-ProgrammableGateArray),即現(xiàn)場可編程門陣列,它是隨著人們對技術(shù)的要求提高而發(fā)展的產(chǎn)物。這里使用FPGA來實現(xiàn)針對脈沖邊沿觸發(fā)型的單光子探測器符合計數(shù)器的設(shè)計。

針對脈沖邊沿觸發(fā)型的單光子探測器進行符合計數(shù)器的設(shè)計,為保證符合計數(shù)有意義,必須保證探測器是同時被觸發(fā)的,即探測器對同一路觸發(fā)脈沖邊沿的響應(yīng)保持較高的一致性。探測器輸出的脈沖經(jīng)過電路處理,為固定脈寬的脈沖。

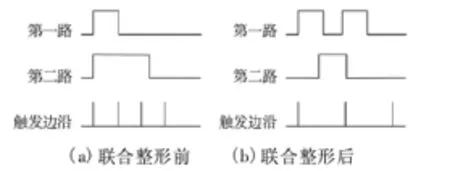

采用邊沿檢測法對信號進行采樣,這也是FPGA最常用的檢測方式。由于輸入的脈沖信號對FPGA采樣時鐘來說是異步信號,并且兩路信號從探測器輸出到輸入到FPGA內(nèi)這期間引入的路徑延時不一定具有嚴(yán)格的一致性,因此必須對輸入的兩路脈沖進行聯(lián)合整形處理,即將它們跨越采樣時鐘邊沿兩側(cè)但實際上屬于同時到達的信號整形為同時到達信號,如圖1:

圖1

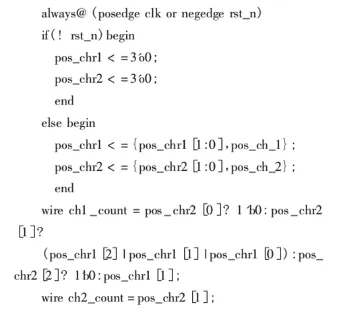

通過VerilogHDL語言進行功能程序編寫,對兩路信號進行聯(lián)合整形的FPGA代碼如下:

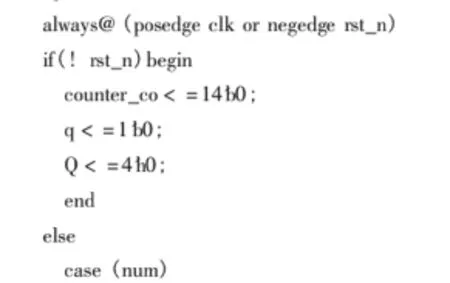

對兩路信號完成整形后再對它們進行符合計數(shù)測量就不會再出現(xiàn)差錯。由于只有觸發(fā)時刻脈沖邊沿觸發(fā)型的單光子探測器才可能有信號的輸出,因此對輸出信號進行延時符合時要以觸發(fā)時鐘的周期為單位。在FPGA中對固定延時的控制可以通過計數(shù)器的方式實現(xiàn),根據(jù)采樣時鐘和探測器觸發(fā)時鐘的周期關(guān)系,用延遲較小的那路信號啟動計數(shù)器,在計數(shù)器達到指定計數(shù)時判斷另外一路是否有信號到達。對采樣時鐘頻率50M,探測器觸發(fā)脈沖為5M時候的VerilogHDL代碼如下:

cnt==20'hfffff為計數(shù)數(shù)據(jù)傳出和清零重新計數(shù)的時刻,上述代碼中考慮了該時鐘周期內(nèi)可能出現(xiàn)符合計數(shù)可能的情況。

通過QuartusⅡ調(diào)用ModelSim-Altera進行仿真,在0延遲下計算2000個符合脈沖(其中1000個上升沿錯位),以及二路信號延遲一個觸發(fā)時鐘周期(T=200ns)計算1000個符合脈沖的仿真。

按鍵key用來控制延時的設(shè)置,延時狀態(tài)用led來指示,001表示0延遲,010表示二路信號延遲一個觸發(fā)時鐘周期,led的狀態(tài)控制和實現(xiàn)延時符合計數(shù)的狀態(tài)機是相對應(yīng)的。

4、FPGA發(fā)展

4.1 與信號處理器進行結(jié)合

在實際開發(fā)過程中,有不少對數(shù)字信號進行處理的方法。例如,使用DSP或者各種微型處理器等。而現(xiàn)在,F(xiàn)PGA同樣可以被作為運算核心進行數(shù)字信號處理的系統(tǒng)的開發(fā)。特別是FPGA具有運算速度快這一優(yōu)勢,使FPGA能夠適用于對處理速度要求越來越高的信號處理系統(tǒng)。

4.2 IP核庫的使用

Altera與Xilinx等公司均為自己的FPGA產(chǎn)品開發(fā)了相應(yīng)的IP核庫,IP核大體可分為兩類:一種是開發(fā)廠商將硬件及其配套接口作為IP硬核嵌入到FPGA當(dāng)中。另一種是通過Verilog/VHDL等語言編寫的具有各種功能的IP軟核,開發(fā)者可以在程序中直接調(diào)用這些IP模塊,并對模塊的部分參數(shù)進行設(shè)置,以完成一些重復(fù)且復(fù)雜的功能,大大減少了開發(fā)者的工作量以及大幅降低了系統(tǒng)開發(fā)設(shè)計難度。

4.3 SOPC技術(shù)的發(fā)展

SOPC技術(shù)是一種基于FPGA的SOC解決方案,實現(xiàn)SOPC的方法主要有以下三種:一是將IP硬核嵌入FPGA的SOPC系統(tǒng);二是將IP軟核嵌入FPGA的SOPC系統(tǒng);三是基于HardCopy技術(shù)的SOPC系統(tǒng)。

總之,F(xiàn)PGA具有很多優(yōu)勢,因此也是得多了進一步應(yīng)用。本文分析了FPGA的數(shù)字系統(tǒng)設(shè)計,以期提供一些借鑒。

[1]葉忠彬.基于FPGA的數(shù)字頻率合成系統(tǒng)的設(shè)計與實現(xiàn)[D].電子科技大學(xué),2011.

[2]梁彬.基于FPGA的PCM數(shù)字解碼系統(tǒng)的設(shè)計[D].電子科技大學(xué),2003.

[3]王永維.一種基于FPGA的數(shù)字秒表設(shè)計方法[J].電子元器件應(yīng)用,2012,01:10-13.