速度-張力型三電機(jī)協(xié)調(diào)同步控制平臺研制

李 景,李 慧,,劉星橋

(1.淮陰工學(xué)院,淮安223001;2.江蘇大學(xué),鎮(zhèn)江212013)

0 引 言

隨著現(xiàn)代工業(yè)化的發(fā)展,多電機(jī)同步協(xié)調(diào)控制的應(yīng)用越來越廣泛,例如在紡織、造紙、印染等行業(yè)[1]。伴隨著智能信息技術(shù)的發(fā)展,對多電機(jī)同步協(xié)調(diào)控制系統(tǒng)的實時性提出了更高的要求,傳統(tǒng)的多電機(jī)系統(tǒng)多采用總線輪詢式控制,控制周期長,控制實時性差,已經(jīng)不能滿足三電機(jī)、乃至多電機(jī)同步系統(tǒng)的需求。文獻(xiàn)[2-4]提出了在傳統(tǒng)PLC總線控制平臺下三電機(jī)系統(tǒng)的同步協(xié)調(diào)控制,分別對系統(tǒng)的動態(tài)性能、穩(wěn)態(tài)性能以及解耦性能進(jìn)行了實驗和分析,系統(tǒng)控制穩(wěn)定,但存在一定的超調(diào)量,跟蹤存在一定的穩(wěn)態(tài)誤差;本控制平臺即對其進(jìn)行重新改造,以多微處理器為控制核心,以CPLD的硬件同步特性為控制特色,提高系統(tǒng)的調(diào)節(jié)時間,降低系統(tǒng)的超調(diào)量,進(jìn)一步提高系統(tǒng)的跟蹤精度和解耦性能,從而提高整個控制系統(tǒng)的控制性能。本文將以速度-張力型三電機(jī)同步協(xié)調(diào)控制系統(tǒng)為例,提出了基于多處理器的速度-張力型三電機(jī)同步測控系統(tǒng)方案,采用CPLD多RS485總線并發(fā)同步控制模式,在同等通信波特率下能夠?qū)⒖刂茖崟r性提高3倍以上,為速度-張力型三電機(jī)協(xié)調(diào)同步控制平臺研制提供了新的方案。

本文首先介紹了系統(tǒng)的總體設(shè)計框架,討論了各個子模塊的設(shè)計,分模塊進(jìn)行設(shè)計,對于CPLD部分,采用自上而下的模塊化設(shè)計方案[5-9];接著對基于狀態(tài)機(jī)的全數(shù)字純硬件濾波器的濾波性能進(jìn)行了測試,同時對本控制平臺的通信速度和傳統(tǒng)的PLC總線控制平臺進(jìn)行了比較測試,在該硬件實驗控制平臺下采用一階模糊自抗擾控制策略對平臺的方波跟蹤性能進(jìn)行測試,與傳統(tǒng)的PLC總線控制平臺的控制效果進(jìn)行比較分析;最后通過解耦實驗,PC機(jī)的服務(wù)器部分進(jìn)行了綜合測試。

1 平臺總體設(shè)計

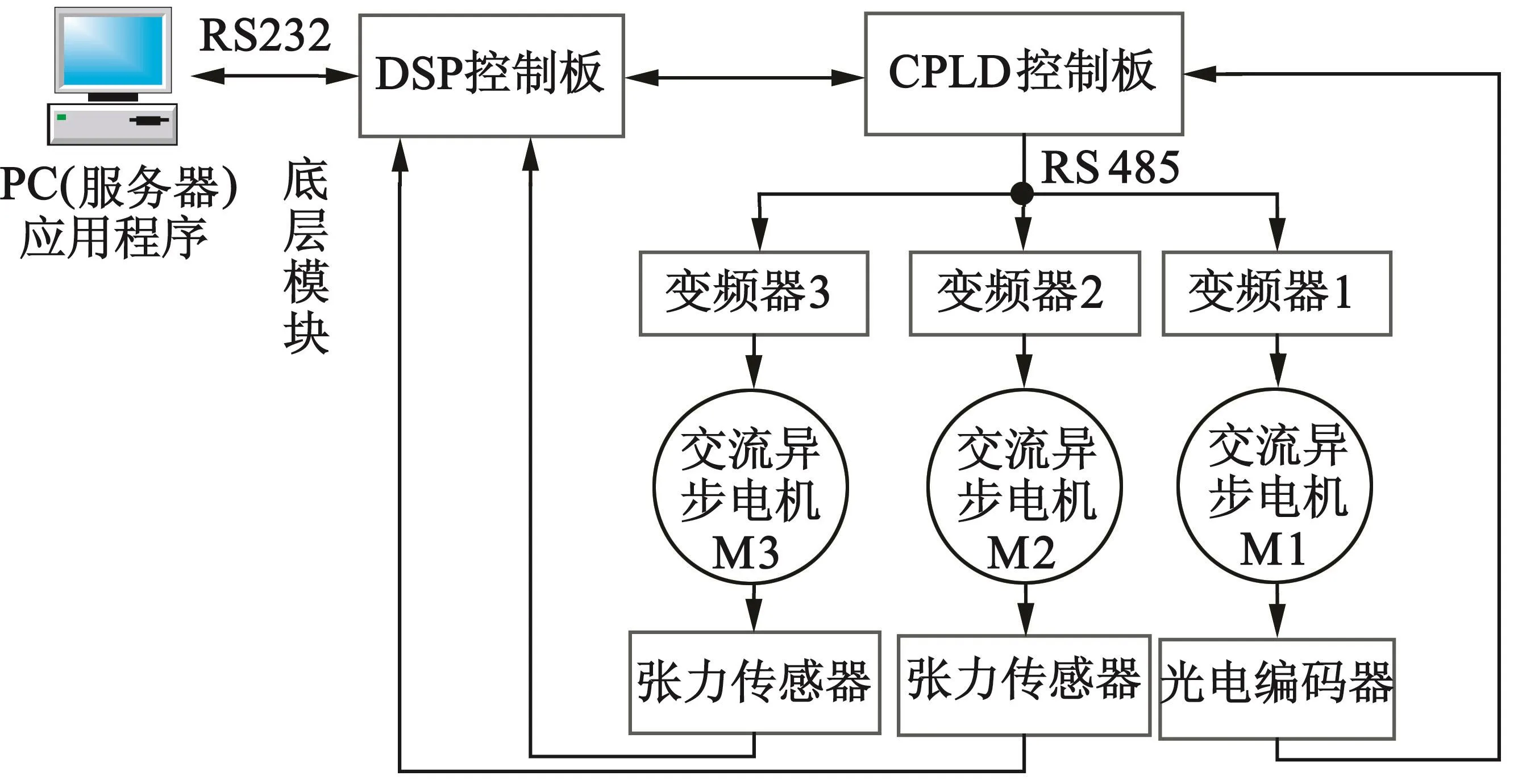

系統(tǒng)由CPLD控制模塊、DSP控制模塊、本地服務(wù)器等幾大模塊組成。系統(tǒng)結(jié)構(gòu)圖如圖1所示,由CPLD通過增量式圓光柵編碼器實時采集主電機(jī)速度,由張力傳感器結(jié)合變送器采集并處理兩組張力數(shù)據(jù)送DSP處理,DSP和CPLD通過數(shù)據(jù)線直接相連,DSP和計算機(jī)服務(wù)器之間采用RS232串行連接,CPLD利用狀態(tài)機(jī)組建RS485網(wǎng)絡(luò)通過SP3485控制3路變頻器對3臺異步電機(jī)同時進(jìn)行控制。

圖1 系統(tǒng)總體結(jié)構(gòu)圖

2 各子模塊設(shè)計

2.1 CPLD控制模塊設(shè)計

CPLD控制模塊主要采用層次化設(shè)計方案[5],系統(tǒng)分為3個層面,即頂層、中間層和底層模塊設(shè)計部分。

2.1.1 CPLD頂層模塊設(shè)計

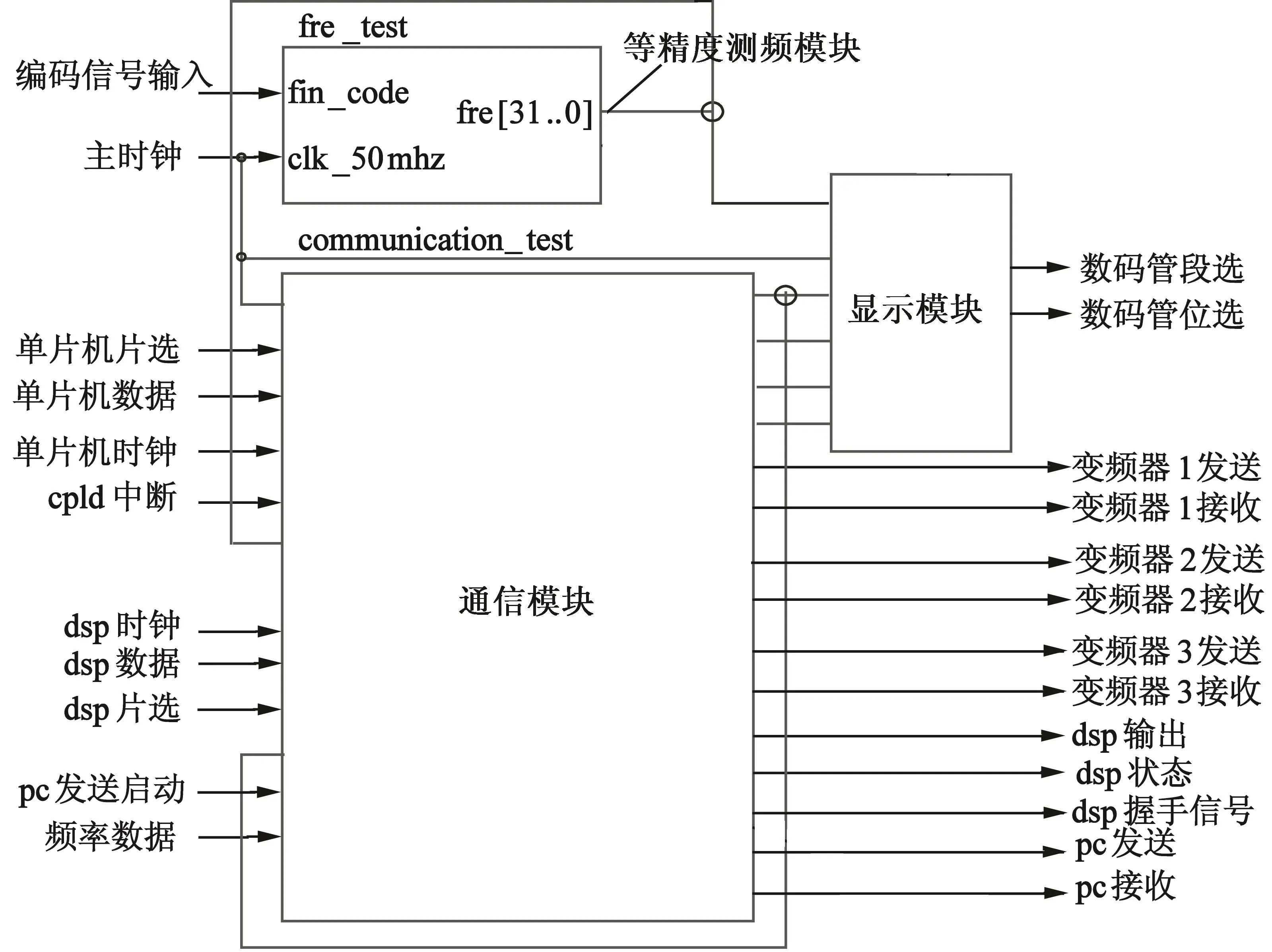

在頂層設(shè)計中主要包括測頻模塊、顯示模塊以及通信模塊等中間層模塊。頂層模塊圖如圖2所示。

圖2 CPLD部分系統(tǒng)模塊圖

2.1.2 CPLD中間層模塊設(shè)計

對應(yīng)頂層文件中的每一個模塊進(jìn)行展開,都是一個獨立的設(shè)計單元,可以獨立仿真調(diào)試,這里稱為中間層模塊。根據(jù)圖2可知,系統(tǒng)包含測頻、顯示以及通信3大中間層模塊。

(1)通信模塊

通信模塊可以分為同單片機(jī)SPI通信模塊(mcu_cpld)、同PC機(jī)RS232通信模塊(pc_cpld)、與DSP數(shù)據(jù)通信控制模塊(dsp_cpld)、以及多RS485變頻器通信模塊(mmv_cpld)等模塊,具體模塊圖如圖3所示。

圖3 通信模塊圖

其中mcu_cpld模塊是CPLD同單片機(jī)SPI通信模塊,模塊中的mcu_cs,mcu_data,mcu_clk分別是SPI通信的片選信號、數(shù)據(jù)線以及時鐘線;mcu_mode[1..0]是譯碼功能選擇端,zl_set[31..0]是張力設(shè)置的數(shù)據(jù),sudu_set[31..0]是主電機(jī)速度設(shè)置數(shù)據(jù),zl_data[31..0]是張力傳感器實時采集的數(shù)據(jù)。

dsp_cpld模塊是CPLD同DSP通信模塊,該模塊主要包含兩部分,一部分是CPLD向DSP發(fā)送數(shù)據(jù)模塊,DSP采用中斷進(jìn)行介紹;另一部分是DSP向CPLD發(fā)送數(shù)據(jù)模塊,此時CPLD負(fù)責(zé)接收,采用SPI通信模式。模塊中的cpld_int是DSP同CPLD的握手信號,cpld_in[31..0]是待輸入的測頻信號,dsp_clk,dsp_data,dsp_cs分別是同DSP通信SPI的時鐘線、數(shù)據(jù)線以及片選信號;模塊輸出信號data_out[7..0]是送往DSP的8位并行信號,數(shù)據(jù)是分批送給DSP,Data_states[3..0]是狀態(tài)線,用來區(qū)分送往DSP的數(shù)據(jù)的性質(zhì),y_test是測試信號。

mmv_cpld模塊是同變頻器之間多RS485總線控制模塊,模塊中的 mmv_txd1,mmv_rst1,mmv_txd2,mmv_rst2,mmv_txd3,mmv_rst3分別是送給變頻器的速度、張力1、張力2的控制信號。

pc_cpld是同PC機(jī)通信的模塊,pc_key是PC機(jī)發(fā)送數(shù)據(jù)的啟動觸發(fā)信號,fre[31..0]是速度的測頻數(shù)據(jù),pc_txd,pc_rxd分別是同PC機(jī)通信的發(fā)送和接收控制信號。

(2)顯示模塊

顯示模塊可以分為驅(qū)動信號分頻模塊、數(shù)碼管顯示模塊。設(shè)計方法較常規(guī),此處不再多述。

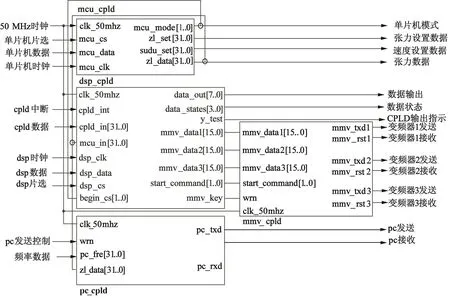

(3)測頻模塊

測頻模塊可以分為全數(shù)字濾波以及等精度測頻等兩大模塊,具體模塊圖如圖4所示。

圖4 測頻模塊圖

圖4 中,fin_code是來自增量式圓光柵編碼器的單相脈沖信號,clk是系統(tǒng)的基準(zhǔn)時鐘信號(50MHz),輸出fre[31..0]是經(jīng)過低通濾波以及等精度測頻模塊處理之后得到的合成信號,分別送DSP,PC機(jī)以及數(shù)碼管顯示,圖3中最前面的是基于狀態(tài)機(jī)的全數(shù)字低通濾波子模塊,中間的是等精度測頻控制模塊,最后的是數(shù)據(jù)線合成模塊。

2.1.3 CPLD底層模塊設(shè)計

CPLD控制部分的最低層模塊設(shè)計,這也是程序設(shè)計的基礎(chǔ),這里對本CPLD控制系統(tǒng)的主要底層模塊進(jìn)行設(shè)計,主要包含全數(shù)字濾波模塊、等精度測頻子控制模塊、同單片機(jī)SPI通信模塊、與DSP數(shù)據(jù)通信控制模塊(分為發(fā)送和接收兩個子模塊)、以及多RS485變頻器通信模塊等幾個子模塊。

(1)基于狀態(tài)機(jī)的全數(shù)字低通濾波器設(shè)計與仿真現(xiàn)場的編碼器和電機(jī)軸是硬件連接關(guān)系,在電機(jī)運轉(zhuǎn)時會產(chǎn)生機(jī)械振動,致使編碼器的信號輸出端會隨機(jī)產(chǎn)生很多的高頻毛刺,在計數(shù)時容易使測速模塊產(chǎn)生誤動作,從而影響測速精度。因此,在信號進(jìn)入測速模塊之前必須要進(jìn)行濾波處理,硬件濾波雖然實現(xiàn)容易,但是濾波不精確,容易濾除有用信號,而軟件濾波通常以犧牲速度為代價,而對CPLD而言,采用的并行處理結(jié)構(gòu),對運行速度不構(gòu)成影響,只需要犧牲一部分資源,因此在資源允許的情況下采用數(shù)字式濾波效果好,性能穩(wěn)定,不需要附加電路。因此,本文自主設(shè)計了基于狀態(tài)機(jī)的全數(shù)字低通濾波器。

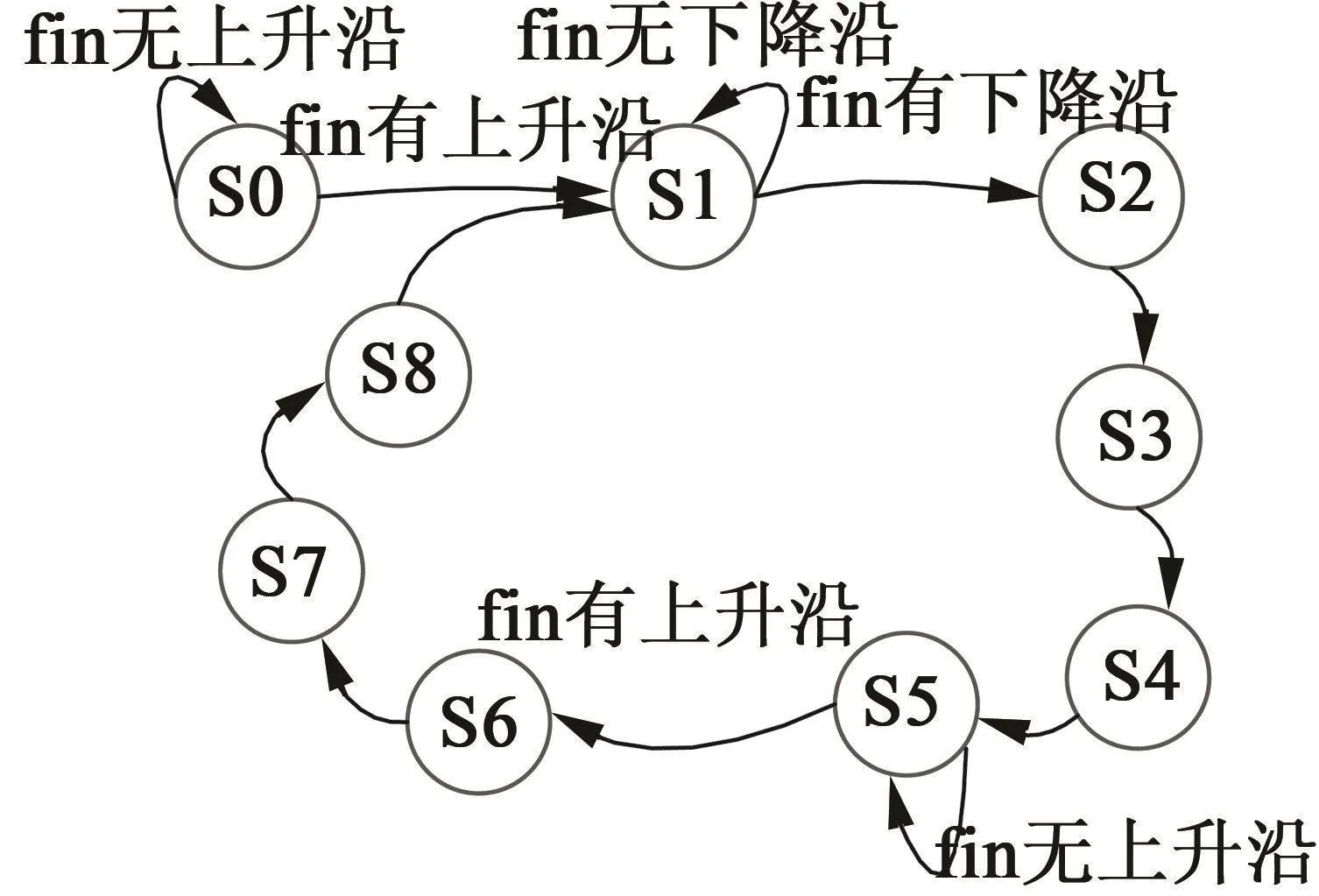

由于考慮實驗中編碼器輸出信號不高于30 kHz,因此選擇截止頻率為30 kHz,對應(yīng)30 kHz等占空比信號的脈寬近似在15 μs。經(jīng)過大量的觀察和分析可知:本系統(tǒng)編碼器輸出的干擾信號主要有正干擾和負(fù)干擾兩種,干擾信號的頻率在30 kHz~50 MHz之間,因此可以認(rèn)為脈寬低于15 μs的信號都認(rèn)為是干擾信號,測速時不予計數(shù)處理。具體設(shè)計思路如狀態(tài)圖5所示。

圖5 全數(shù)字低通濾波模塊狀態(tài)ASM圖

圖5 中,S0代表初始狀態(tài),接收外部輸入待濾波信號fin,計時值清零,停止計時;S1狀態(tài)時啟動計時器計時;S2狀態(tài)產(chǎn)生時間裝載控制信號并停止計時;S3狀態(tài)檢測計時時間是否小于15 μs,如果小于15 μs,認(rèn)為是干擾信號,否則輸出高電平;S4狀態(tài)將計時值清零;S5狀態(tài)啟動新一輪計時,清時間裝載信號;S6狀態(tài)停止計時,產(chǎn)生新的時間裝載控制信號;S7狀態(tài)檢測計時時間是否小于15 μs,如果小于15 μs,認(rèn)定為干擾信號,否則輸出低電平;S8狀態(tài)清除計數(shù)值。

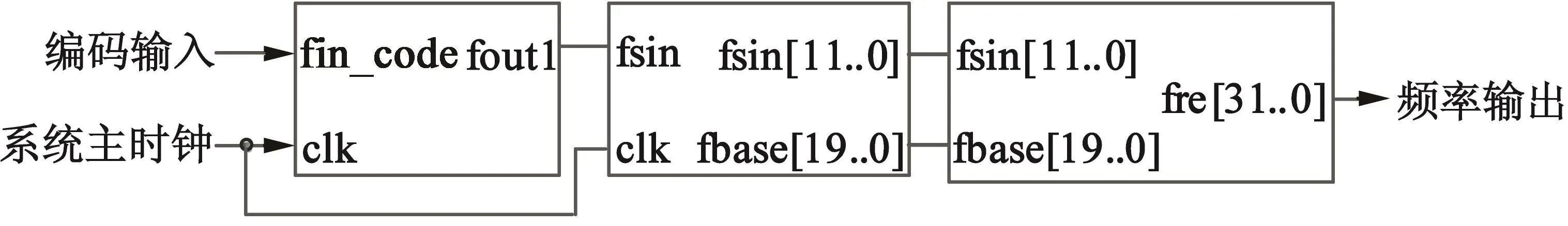

(2)等精度測頻子控制模塊設(shè)計

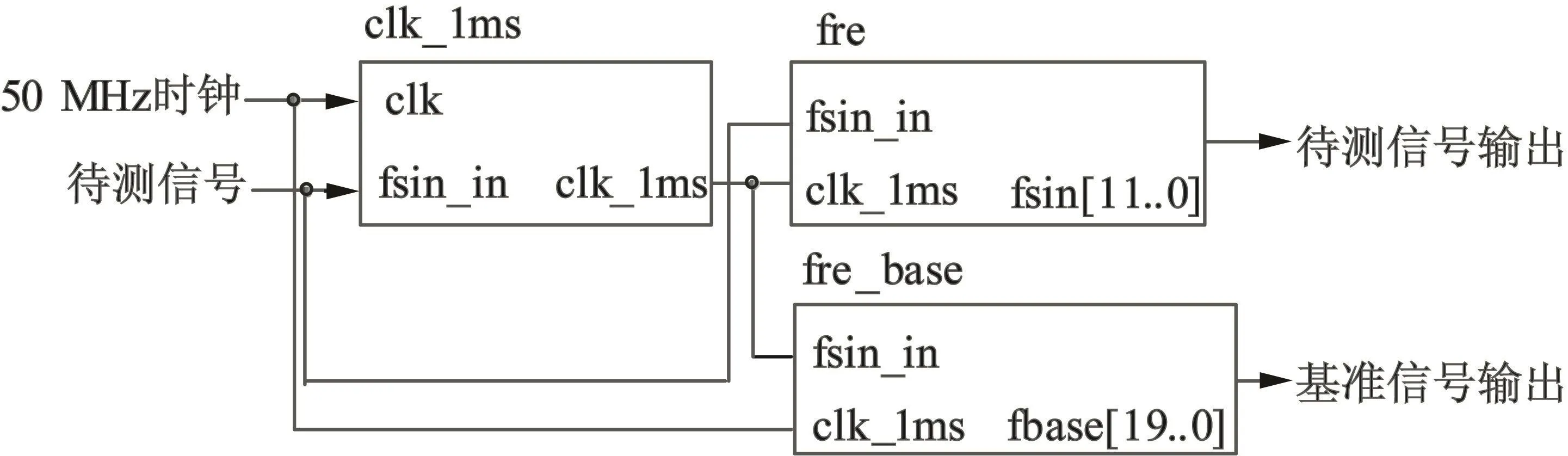

系統(tǒng)測速模塊采用等精度測頻,測量精度由預(yù)置門和被測信號兩方面共同控制,測量的精度只與基準(zhǔn)信號的頻率和穩(wěn)壓度有關(guān),而與被測信號的頻率無關(guān)。系統(tǒng)基準(zhǔn)信號采用CPLD主時鐘50 MHz信號,因此可以保證在整個測量頻段內(nèi)測量精度不變,這就保證了主電機(jī)在不同速度段內(nèi)能夠保持相同的測速精度。

系統(tǒng)測速周期選擇1 ms,由CPLD產(chǎn)生與被測信號同步的閘門信號,控制基準(zhǔn)信號與被測信號同時進(jìn)行計數(shù),并將兩路計數(shù)值送DSP進(jìn)行計算,得到被測信號頻率值。

如果忽略基準(zhǔn)信號的頻率準(zhǔn)確度誤差,系統(tǒng)的測頻相對誤差只與對基準(zhǔn)信號計數(shù)產(chǎn)生的±1誤差有關(guān),而與被測信號頻率無關(guān)。被測信號是編碼器輸出的信號,經(jīng)過低通濾波處理之后的頻率在30 kHz以內(nèi)(對應(yīng)速度1 000 r/min左右)。等精度測頻模塊的層次化設(shè)計模塊圖如圖6所示。

圖6 等精度測頻模塊圖

圖6 中,clk_1ms模塊用來產(chǎn)生1 ms同步閾門信號,fre和fre_base分別是對待測信號和基準(zhǔn)信號的測頻模塊。整個等精度測頻模塊采用圖形文本混合設(shè)計方案,在頂層文件的設(shè)計中為增強程序的可讀性,以簡潔明了為主,主要采用圖形化設(shè)計方案,底層文件的設(shè)計中多采用文本程序化設(shè)計,修改和注釋方便。

(3)與DSP通信發(fā)送控制模塊設(shè)計

CPLD主要通過設(shè)計狀態(tài)機(jī)完成與DSP模塊進(jìn)行發(fā)送數(shù)據(jù)的通信,發(fā)送4個字節(jié)的測頻數(shù)據(jù),4個字節(jié)的單片機(jī)數(shù)據(jù),一共8個字節(jié)的數(shù)據(jù),結(jié)合狀態(tài)字節(jié)采用分次傳送的方法,經(jīng)過8個時鐘脈沖將數(shù)據(jù)傳送給DSP,DSP主要采用中斷接收后再組合的方法來進(jìn)行設(shè)計。

(4)與單片機(jī)SPI通信控制模塊設(shè)計

CPLD與單片機(jī)之間主要采用三線式(SPI模式)通信,數(shù)據(jù)線、時鐘線、控制線作為輸入,從單片機(jī)讀入40位(5個字節(jié))的數(shù)據(jù),其中第一個字節(jié)為狀態(tài)字節(jié),用來判斷具體的鍵盤命令以及檢測到的張力數(shù)據(jù),后面的4個字節(jié)為數(shù)據(jù)字節(jié)。從節(jié)省CPLD端口資源角度考慮,此處采用SPI串行通信模式,主要是采用構(gòu)造狀態(tài)機(jī)的方法來實現(xiàn)控制。

(5)多RS485總線并行控制模塊設(shè)計

系統(tǒng)采用西門子MMV變頻器,采用USS協(xié)議,首先在變頻器面板上將控制方式設(shè)置為遠(yuǎn)程控制方式,具體設(shè)置如下:

a)通過P009設(shè)置為1,使能所有參數(shù)的讀寫訪問。

b)通過P091設(shè)置3臺變頻器的串口連接從站地址0~31,因為3臺變頻器采用獨立控制方式,因此該從站地址可以相同也可以不同,為了區(qū)分方便,可以分別設(shè)置為1,2,3。

c)通過P092設(shè)置串口波特率3~7,默認(rèn)為6(波特率9 600 bit/s)。

d)通過P093設(shè)置串口通訊超時時間。

e)通過P094設(shè)置串行額定系統(tǒng)設(shè)定值。

f)通過P095設(shè)置USS的兼容性,選擇默認(rèn)即可。

g)通過P910將控制方式設(shè)置為遠(yuǎn)程控制方式,然后退出變頻器參數(shù)修改。

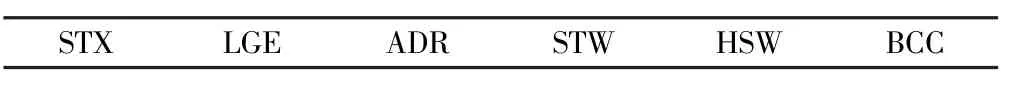

USS協(xié)議分長報文與短報文兩種方式,報文一共8個字節(jié),長報文一共14個字節(jié),此處采用短報文的方式,具體格式如表1所示。

表1 USS協(xié)議短報文格式

表1中,STX為起始字符,固定為16進(jìn)制的02H;LGE為報文長度(去除起始字節(jié)和BCC);此處為0CH;ADR為串行子站地址;STW控制變頻器運行;HSW用于設(shè)定變頻器的頻率值;BCC是前面所有字節(jié)的異或之后的值,用于校驗。

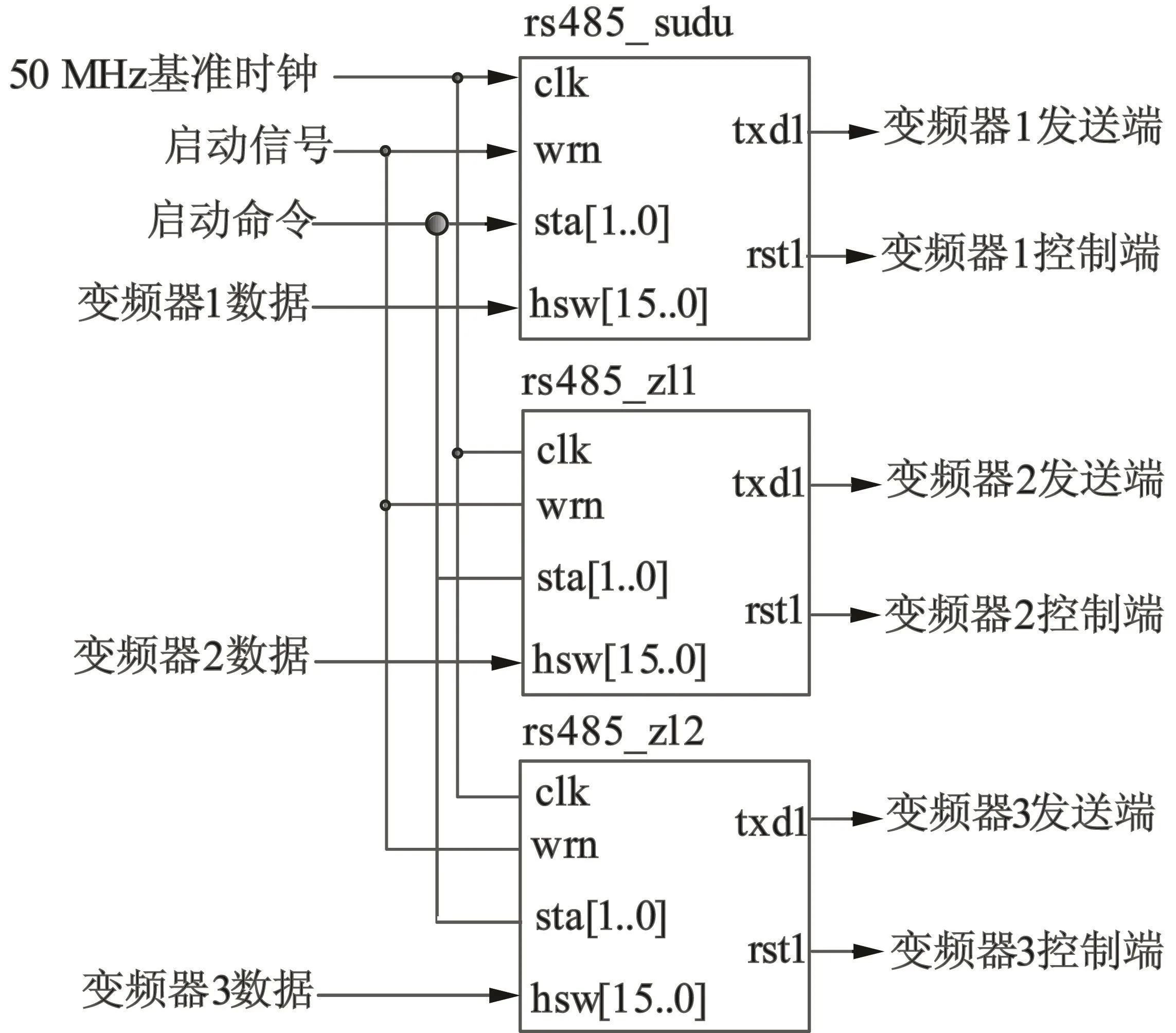

CPLD將3臺變頻器的控制命令和頻率值準(zhǔn)備好,在同步控制信號作用下,同時以RS485方式發(fā)送給3臺變頻器,控制3臺變頻器同時按照不同方式進(jìn)行工作。模塊設(shè)計采用模塊化設(shè)計方案,模塊設(shè)計圖如圖7所示。

圖7 多RS485并發(fā)通信控制模塊設(shè)計圖

圖7 中,rs485_sudu,rs485_zl1,rs485_zl2分別是控制3臺變頻器RS485串行通信的控制模塊,3個模塊在同一個時鐘信號wrn邊沿下工作,在wrn的邊沿處觸發(fā)傳送一組命令或者數(shù)據(jù),同步啟動3個模塊工作,這樣3路通信保存嚴(yán)格同步,大大節(jié)省了和變頻器通信的時間,提高了控制效果,整個設(shè)計采用狀態(tài)機(jī)協(xié)調(diào)實現(xiàn),底層設(shè)計采用文本語言描述方式。

2.2 DSP控制模塊設(shè)計

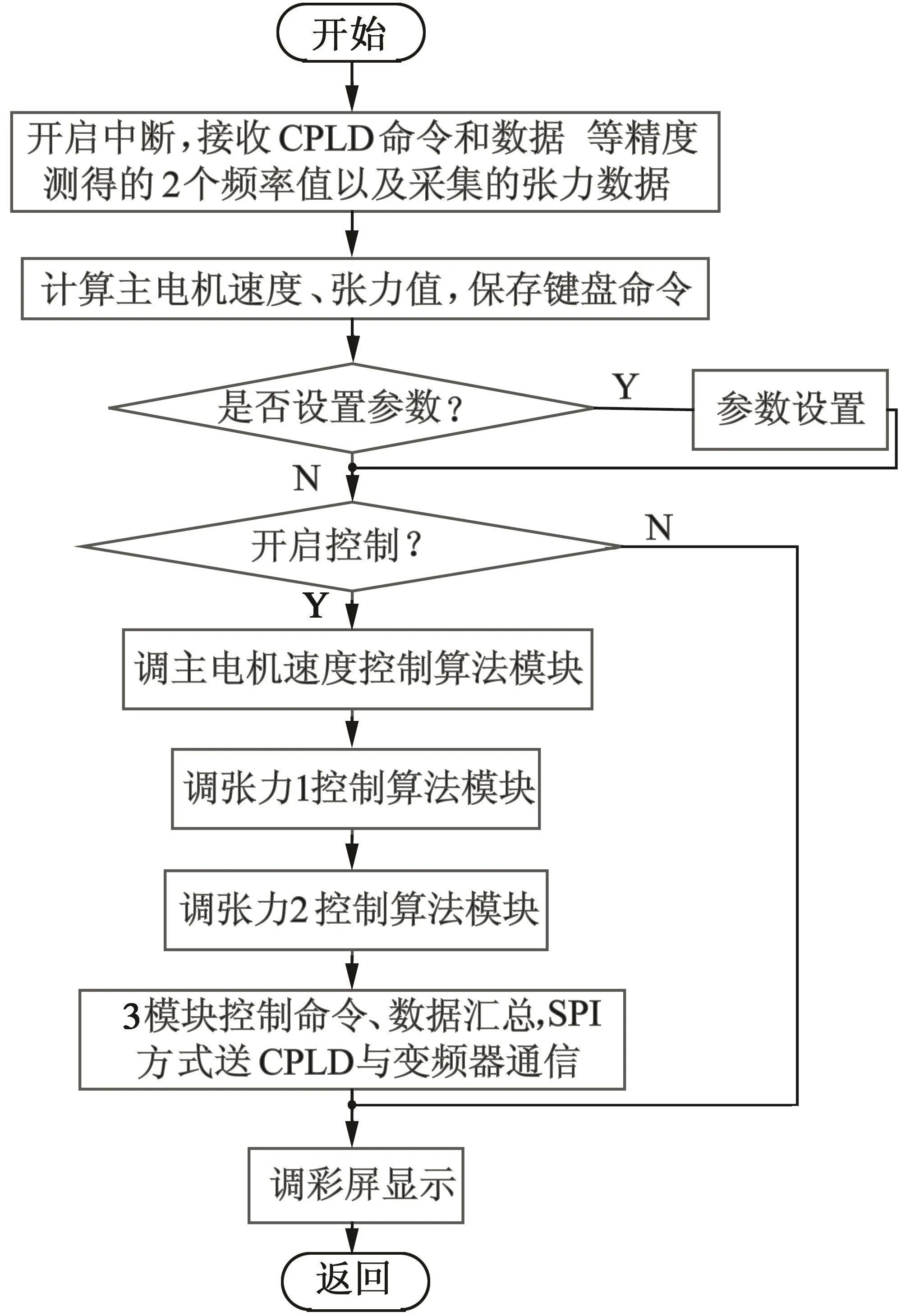

由于DSP芯片本身結(jié)構(gòu)特點,DSP控制在數(shù)據(jù)處理方面具備比通用CPU更大的優(yōu)勢,此處DSP控制模塊主要負(fù)責(zé)算法設(shè)計、彩屏控制以及與CPLD的通信等功能。此處采用一階模糊免疫自抗擾控制算法,模糊免疫自抗擾控制是將現(xiàn)代模糊免疫算法與自抗擾控制算法相結(jié)合的一種控制方法,具有抗干擾能力強、魯棒性好、響應(yīng)速度快等多項優(yōu)勢。主流程如圖8所示。

圖8 DSP主流程圖

從圖8可以看出,在DSP通過中斷接收來自CPLD的鍵盤設(shè)置命令以及實時頻率值和張力數(shù)據(jù),通過計算后檢測控制命令,然后調(diào)用3個對應(yīng)的算法模塊,匯總后送CPLD進(jìn)行同步驅(qū)動RS485總線控制3臺變頻器同時工作,最后調(diào)用彩屏驅(qū)動進(jìn)行彩屏曲線顯示。

2.2.1 模糊免疫自抗擾控制模塊算法設(shè)計

自抗擾控制技術(shù)[10]是中科院韓京清教授提出的一種抗擊擾動行之有效的方法。本文將自抗擾控制技術(shù)與模糊免疫控制技術(shù)[11]相結(jié)合,實現(xiàn)三電機(jī)同步系統(tǒng)控制,根據(jù)模糊免疫自抗擾控制算法,采用查表的方式實現(xiàn)模糊增益控制。系統(tǒng)算法采用C語言完成設(shè)計,算法主要包含以下幾大部分:

(1)自抗擾內(nèi)部狀態(tài)量初始化模塊初始化模塊主要實現(xiàn)內(nèi)部狀態(tài)的初始化,主要對如下參數(shù)進(jìn)行初始化,以主電機(jī)速度控制模塊為例,初始化部分程序設(shè)計如下:

delt_u(0)=0.0;//控制量的變化量

z11(0)=0.0;//自抗擾狀態(tài)量z1

z12(0)=0.0;//自抗擾狀態(tài)量z2

u10(0)=0.0;//控制量

kp_1(0)=kp;//初始增益

(2)主電機(jī)速度模塊模糊免疫自抗擾控制算法設(shè)計

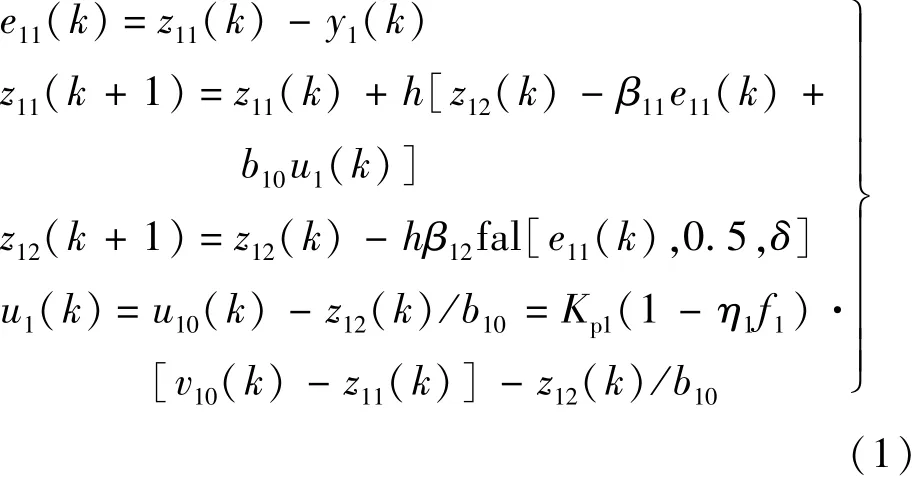

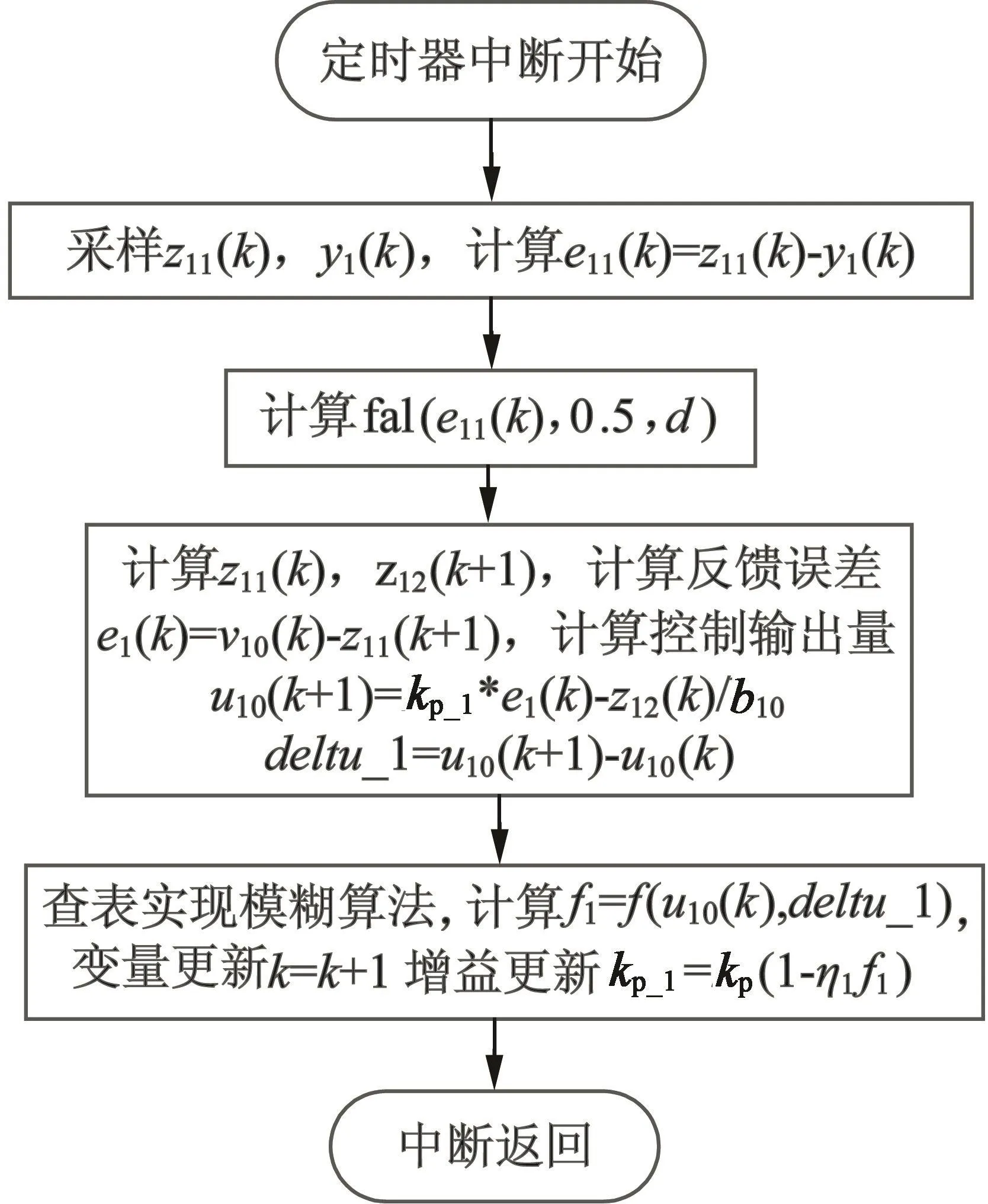

模糊免疫自抗擾控制算法主要根據(jù)輸入量以及輸入的變化量,根據(jù)免疫規(guī)則實現(xiàn),對自抗擾控制參數(shù)進(jìn)行優(yōu)化,在DSP的定時器中完成算法,定時器定時10 ms。設(shè)主電機(jī)速度控制模塊的速度反饋值為y1(k)=ωr1,免疫因子為η1,主電機(jī)速度給定信號為v10(k),主電機(jī)速度子模塊的模糊免疫自抗擾控制方程可以表示:

式中:非線性函數(shù)f1通過查表實現(xiàn),首先根據(jù)免疫特性確定模糊規(guī)則,將模糊規(guī)則結(jié)合實際調(diào)試經(jīng)驗轉(zhuǎn)換為對應(yīng)的數(shù)據(jù)表格,輸入量為u10和deltu_1,輸出量為f1。

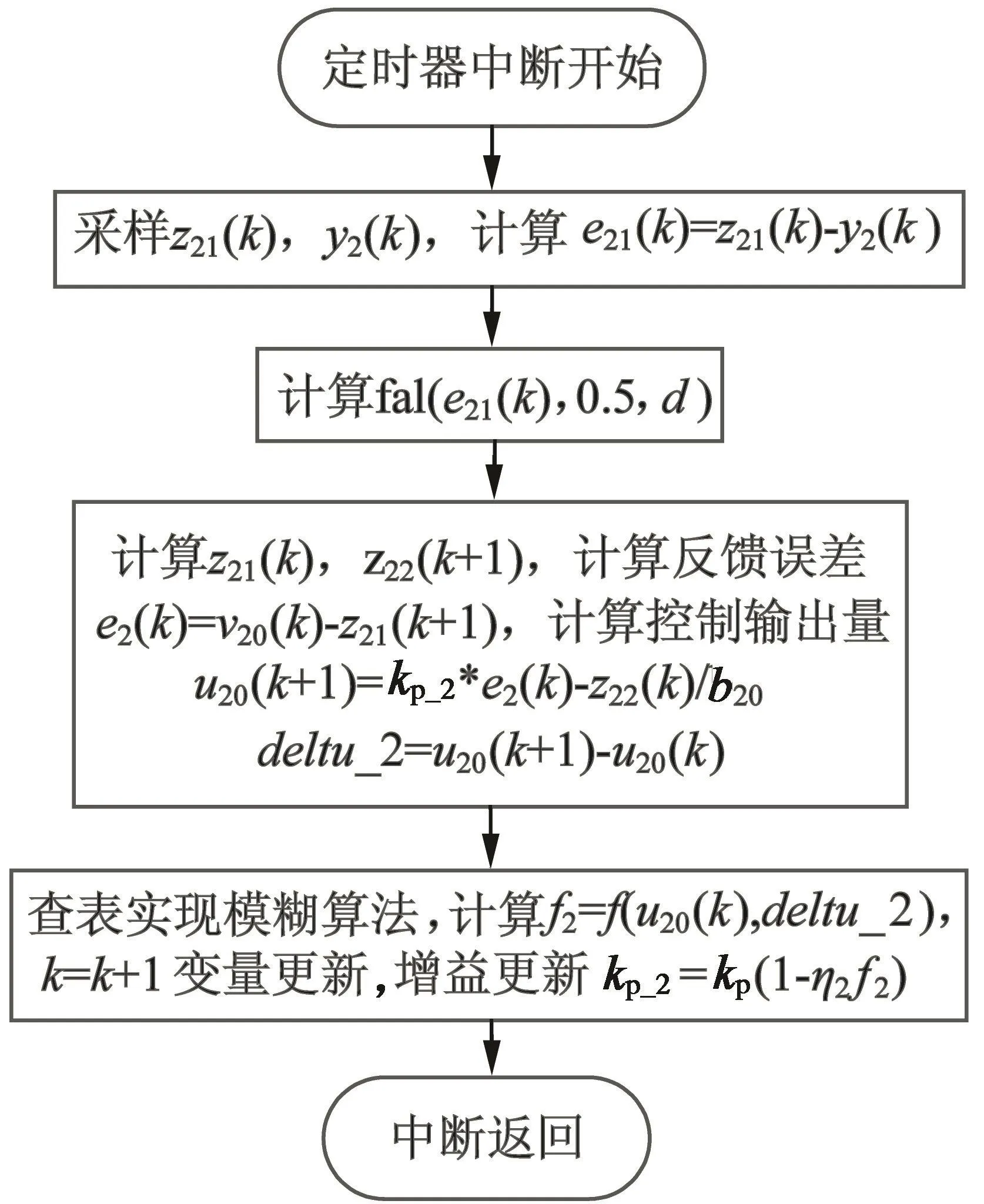

具體實現(xiàn)如流程圖9所示。

圖9 主電機(jī)速度模糊免疫自抗擾控制算法流程圖

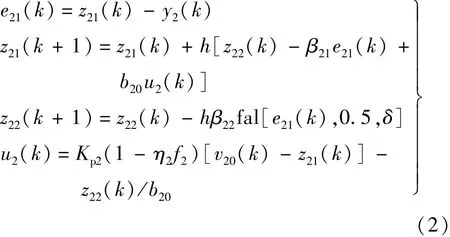

(3)張力1模塊控制算法設(shè)計

張力1模塊主要是對張力1的控制,采用模糊免疫自抗擾控制算法,設(shè)張力1控制模塊的張力檢測值為y2(k)=F12,免疫因子為η2,張力1給定信號為v20(k),張力1子模塊的模糊免疫自抗擾控制方程可以表示:

根據(jù)式(2)結(jié)合模糊規(guī)則表,得到張力1模塊的模糊免疫自抗擾控制流程圖,如圖10所示。

圖10 張力1模塊模糊免疫自抗擾控制算法流程圖

(4)張力2模塊控制算法設(shè)計

張力2模塊主要是對張力2的控制,采用模糊免疫自抗擾控制算法。設(shè)張力2控制模塊的張力檢測值為y3(k)=F23,免疫因子為η3,張力2給定信號為v30(k),張力2子模塊的模糊免疫自抗擾控制方程可以表示:

根據(jù)式(3)結(jié)合模糊規(guī)則表,得到張力2模塊的模糊免疫自抗擾控制流程。

2.3 單片機(jī)控制模塊設(shè)計

單片機(jī)主要實現(xiàn)鍵盤命令的采集、張力的采集、狀態(tài)燈的顯示以及同CPLD之間的通信,為CPLD控制模塊節(jié)約資源,減輕CPLD負(fù)擔(dān),提高系統(tǒng)的性價比,設(shè)計比較簡單傳統(tǒng),此處不再多介紹。

3 服務(wù)器部分程序設(shè)計

PC機(jī)服務(wù)器部分主要采用Delphi高級語言以及RS232串行通信來完成設(shè)計。服務(wù)器同下位機(jī)CPLD之間進(jìn)行RS232串行通信,利用Mscomm控件來完成設(shè)計,服務(wù)器將從下位機(jī)獲取的數(shù)據(jù)存入SQL數(shù)據(jù)庫,同時在線顯示。在服務(wù)器程序中還完成接收外來客戶端的控制命令以及向下位機(jī)發(fā)送控制命令。考慮本文以底層硬件平臺設(shè)計為主,因此服務(wù)器端具體的設(shè)計在此不再多述。

4 實驗與分析

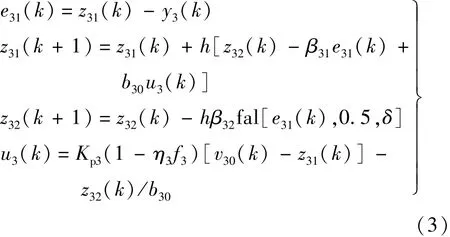

實驗采用3臺三相交流異步電機(jī)作為控制對象,電機(jī)額定轉(zhuǎn)速為1 494 r/min,變頻器為西門子變頻器,處理器選用DSP2812微處理器,CPLD選用MAXII芯片EPM1270TC5,速度傳感器采用增量式2048刻線圓光柵編碼器,張力傳感器采用SL-100傳感器。硬件平臺如圖11所示。以模糊免疫自抗擾控制策略為例,測試手機(jī)客戶端在線波形的質(zhì)量。

圖11 實驗系統(tǒng)硬件平臺

4.1 通信快速性能分析

傳統(tǒng)的實驗平臺利用PLC+PROFIBUS總線控制3臺變頻器,采用輪詢方式,一臺變頻器驅(qū)動一臺電機(jī)完成一次通信需要傳輸16字節(jié)數(shù)據(jù),波特率9 600 bit/s,西門子串行通信數(shù)據(jù)格式為1位起始位,8位數(shù)據(jù)位,1位奇偶校驗位加上1位停止位,一共11位數(shù)據(jù),即傳輸1個字節(jié)數(shù)據(jù)要傳11位,對于3臺變頻器輪詢方式完成一次完整的數(shù)據(jù)傳輸需要傳輸48字節(jié)數(shù)據(jù),需要48/(9 600/11)=0.055 s,即55 ms左右,因此在PLC中通常選用OB100即設(shè)置100 ms作為一個控制周期。而采用改進(jìn)后的本控制平臺,采用基于USS協(xié)議的多RS485總線并發(fā)同步控制模式,將長報文的14字節(jié)改成了短報文控制方式(即8個字節(jié)),一次一臺變頻器控制一臺電機(jī)需要傳輸8字節(jié),波特率設(shè)置不變,也設(shè)置為9 600 bit/s,由于3臺變頻器是同時同步控制3臺電機(jī),因此完成一次完整的通信只需要傳輸8/(9 600/11)=0.009 16 s,即9.16 ms。控制周期可以設(shè)置為10 ms。從這可以看出,在同等波特率設(shè)置下,本控制平臺實時性相比傳統(tǒng)控制平臺提高了近10倍,這也是本控制平臺的一大特色所在。

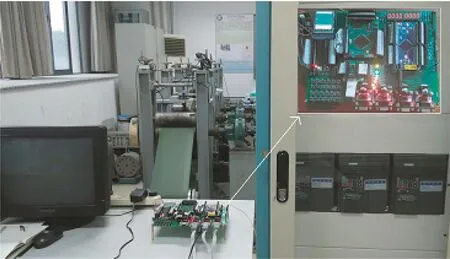

4.2 基于狀態(tài)機(jī)的全數(shù)字低通濾波性能測試

將主電機(jī)速度設(shè)定為300 r/min進(jìn)行低通濾波性能測試。經(jīng)過計算,測速編碼器B相(選取兩相中的其中一相)對應(yīng)輸出信號10 kHz左右,濾波前后信號的對比圖以及放大對比曲線如圖12所示。

圖12 全數(shù)字濾波效果圖

從圖12可以看出,經(jīng)過本全數(shù)字低通濾波進(jìn)行處理之后,能夠基本將所有的高頻毛刺信號(高于30 kHz的信號)濾除干凈。由于狀態(tài)機(jī)的處理與判別需要時間,使得濾波后的信號比原始信號在相位上要滯后接近90°,但是由于本系統(tǒng)采用的是等精度測頻,閘門信號與被測信號同步,因此,對系統(tǒng)的測頻測速基本不構(gòu)成影響。綜上可知,基于狀態(tài)機(jī)的全數(shù)字低通濾波器設(shè)計方案能夠成功地實現(xiàn)了全數(shù)字濾波的功能,完全滿足測速的需要。

4.3 主電機(jī)方波跟蹤性能比較測試

采用一階模糊免疫自抗擾控制算法對兩種控制平臺進(jìn)行方波跟蹤性能測試。傳統(tǒng)的PLC控制平臺控制周期T=100 ms,根據(jù)文獻(xiàn)[11],ESO的數(shù)值仿真研究表明,參數(shù)βi1,βi2由系統(tǒng)的采樣步長決定,其中:βi1=1/h,βi2=1/(5×h2)。 取 h=0.1 s,因此βi1,βi2分別選取為10,20。對應(yīng)本控制平臺,采樣控制周期提高了十倍,T′=10 ms,因此,βi1_1,βi2_1分別選取為100,2 000。

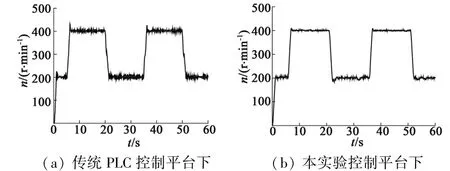

速度參考給定信號為一200~400 r/min的標(biāo)準(zhǔn)方波信號,測試時間為60 s,主電機(jī)分別在傳統(tǒng)的PLC控制平臺和基于多微處理器的控制平臺兩種控制平臺下跟蹤該信號,跟蹤曲線如圖13所示。

圖13 方波跟蹤性能測試曲線

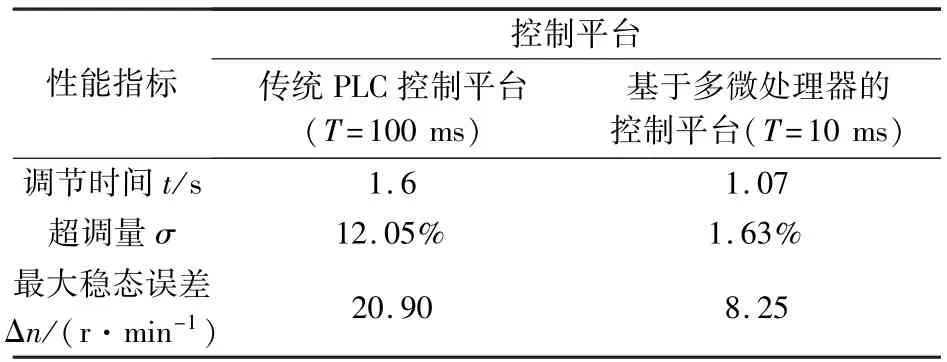

根據(jù)圖13對方波跟蹤的性能參數(shù)進(jìn)行列表,如表2所示。

表2 兩種不同控制平臺下的方波跟蹤性能結(jié)果

從表2可知,采用本控制平臺(基于多微處理器的實驗平臺)可以大大提高控制系統(tǒng)的控制性能。在動態(tài)性能方面,系統(tǒng)調(diào)節(jié)時間比原有的PLC控制平臺快了0.53 s,系統(tǒng)起動超調(diào)量大大得到抑制,本實驗平臺下的系統(tǒng)超調(diào)量是傳統(tǒng)PLC控制超調(diào)量的13.53%,相比傳統(tǒng)的PLC控制平臺想的系統(tǒng)超調(diào)量減小近7倍。在系統(tǒng)的穩(wěn)態(tài)性能方面,跟蹤最大誤差相比傳統(tǒng)的PLC控制平臺減少了60.53%。

5 結(jié) 語

通過本測控系統(tǒng)的多次性能測試,系統(tǒng)利用CPLD的并行特性以及引入DSP芯片在一定程度上提高了系統(tǒng)的實時性以及數(shù)據(jù)處理能力,為快速多總線復(fù)雜算法控制提供了新的設(shè)計思路,為三電機(jī)乃至多電機(jī)同步測控系統(tǒng)平臺的研制提供了新的參考方案,具有較強的實用性以及推廣價值。