快刀伺服控制器設計中的信號完整性問題研究

劉廣民,張連新,張 敏,戴曉靜,黃小津

(中國工程物理研究院 機械制造工藝研究所,四川 綿陽621900)

快刀伺服控制器設計中的信號完整性問題研究

劉廣民,張連新,張 敏,戴曉靜,黃小津

(中國工程物理研究院 機械制造工藝研究所,四川 綿陽621900)

在快刀伺服(FTS,Fast Tool Servo)控制器設計過程中,其中的核心技術單元包括電壓反饋、位移反饋以及高頻模擬電壓信號控制全部基于具有高速數據總線的ADC或DAC實現,如果信號完整性問題處理不好就會對控制器的性能造成不良影響。為了使快刀伺服控制器具備良好的信號完整性,本文基于Hyperlynx仿真軟件,對快刀伺服控制器中的核心器件(FPGA、模數轉換器ADS1602以及數模轉換器DAC9881)和關鍵信號路徑的信號完整性問題進行了詳細的分析和仿真研究,得到了量化的信號完整性改善方法和措施,為實際的控制器電路設計提供了有價值的理論依據和指導。

快刀伺服控制器;信號完整性;Hyperlynx;FPGA;ADS1602

在具有復雜表面或微結構的光學零件加工領域,快刀伺服系統(FTS)相對于現代的一些加工技術和方法:比如電子束直寫技術、激光束直寫技術以及蝕刻技術和LIGA等,在加工精度及一致性、加工效率和經濟性方面都有一定的優勢,已經成為研究的熱點[1-2]。另外FTS輔助金剛石車削技術也已經廣泛應用于多個加工領域[3]。

基于上述背景,我們對快刀伺服系統中的關鍵技術開展了系列研究工作,包括控制技術、驅動技術、柔性鉸鏈技術等。其中快刀伺服控制技術是快刀系統智能算法實現、精度以及頻響保證的關鍵技術之一,而作為控制系統的基石,硬件電路性能直接關系到快刀控制器設計的成敗。隨著電路工作頻率的提高以及印制電路板密度的增加,信號完整性顯得愈發重要,已經成為高速硬件電路設計能否成功的關鍵因素之一[4]。因此對于高速電路占據很大比重的快刀伺服控制器,對其設計中的信號完整性問題必須給予足夠關注。Hyperlynx是典型的SI仿真軟件,對主要 PCB類型文件都提供接口,適用于低頻段(GHz以下)的信號完整性和電磁兼容仿真[5]。文中將基于Hyperlynx軟件對快刀伺服控制系統硬件的信號完整性問題進行探討和分析,為實際工程設計提供理論依據和指導意見。

1 快刀伺服控制系統架構設計

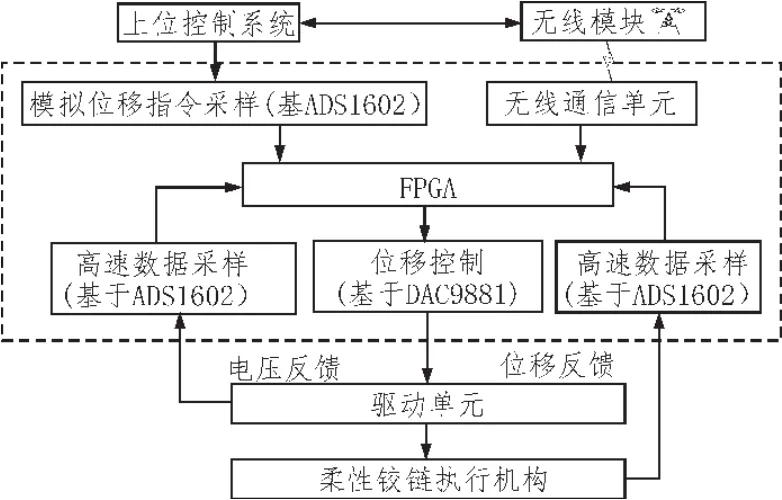

快刀伺服關鍵技術研究技術指標如下:最大位移50 μm;重復定位精度5 nm;20 μm情況下頻響150 Hz。基于此,本文提出了如圖1所示的快刀伺服控制系統設計架構。虛線框部分將是本文信號完整性的重點分析研究對象。FPGA作為核心處理器,負責接收、解析來自上位的控制和位移指令,處理電壓和位移反饋數據并進行壓電陶瓷位移實時控制。位移指令接收設計了模擬信號方式和無線通信兩種方式。可滿足實時性與遠程控制的不同需求場合。

圖1 快刀伺服控制系統架構

根據課題標的,ADC采樣精度需要達到1/10 000,另外基于壓電陶瓷驅動的快刀伺服系統最高頻響一般在2 000 Hz左右[5],根據耐奎斯特抽樣定理[7],保證頻譜不失真的ADC采樣頻率需大于4 KHz。同時為了提高閉環精度,需要對全量程細分,當量程20 μm、頻響150 Hz、重復定位精度5 nm時,ADC采樣頻率至少為0.6 MHz。基于上述需求,ADC選用TI公司的ADS1602,精度16位,最高采樣頻率2.5 MHz。數據接口為SPI總線,最高數據傳輸速率40 MHz。DAC器件選擇了TI公司的DAC9881,分辨率為18位,建立時間只有5 μs。數據接口為最高頻率50 MHz的SPI總線。FPGA選用了Altera公司CycloneIV系列的EP4CE15F17I7。

2 關鍵信號完整性分析

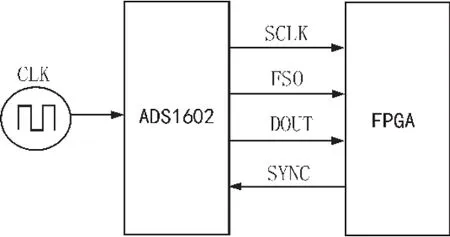

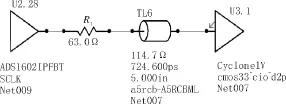

如果數字邏輯電路的頻率達到或者超過45~50 MHz,而且工作在這個頻率之上的電路已經占到了整個電子系統的一部分(如1/3),就需要考慮信號完整性問題[8]。ADS1602和DAC9881的SPI的總線速率都已經接近和達到了這個頻率范圍。文中將ADS1602與FPGA的SPI總線作為研究對象進行信號完整性分析,再將總結出的分析方法和結論應用于DAC9881的信號完整性討論。圖2是ADS1602與FPGA的 SPI總線接口,其中CLK為采樣時鐘,來源為有源高精度晶振;SCLK是SPI總線同步時鐘;FSO為幁同步信號;DOUT為轉換數據輸出;SYNC為同步信號。

圖2 ADS1602與FPGA的SPI總線接口

文中選擇SCLK和DOUT作為對象分析和討論反射、延遲以及串擾這幾個關鍵信號完整性問題,其它的依此類推。器件的IBIS模型由器件廠商官方網站獲取。

2.1 反 射

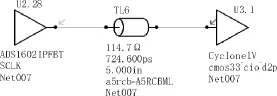

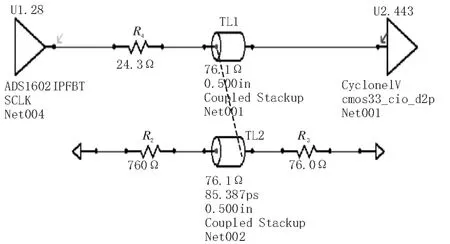

ADS1602的SCLK信號完整性分析模型如圖3所示。

圖3 SCLK信號完整性分析模型

當傳輸線的長度L(單位為in)與信號上升時間RT(單位為ns)比值小于1時[9],反射信號就會淹沒在信號邊沿中而不會出現反射造成的振鈴等問題。根據ADS1602的IBIS模型,其上升沿和下降沿斜率最快分別為:

其中,ramp_r為上升沿斜率,ramp_f為下降沿斜率。

ADS1602設計為3.3 V數字接口,其最快上升時間與下降時間分別是3 ns和3.9 ns。因此當互連線長度不超過3in時就不會出現信號完整性問題。而實際設計中很多情況下是滿足不了互連線長度要求的,需要通過阻抗匹配來解決信號完整性問題。

反射系數公式如式3所示[10],只要保證源端或負載端的阻抗ZL與傳輸線阻抗Z0相等,則反射系數ρ為零,反射就不會發生。

阻抗匹配的端接技術主要有以下幾種[11]:

1)片上源端自端接;2)源端串行端接;3)負載端并行電阻端接;4)負載端并行阻容端接。其中方案1最優,節省空間、成本低并節省功耗,但是這一方案依賴于芯片本身;方案2主要缺點是占用板子有效面積;方案3會增加額外的功耗;方案4解決了方案3的功耗問題,但是由于電容的使用增加了信號延遲。

解決好阻抗匹配問題的先決條件是知曉驅動源與信號線的阻抗[12],在Hyperlynx軟件的優化端接選項(optimize termination…)中可以看到ADS1602的輸出引腳驅動阻抗為51.7 ohm,該值已經接近大多數情況下的傳輸線阻抗值,因此為了節省板上空間,可以嘗試通過傳輸線的參數以及疊層設計使傳輸線的阻抗接近51.7 ohm來達到阻抗匹配的目的。

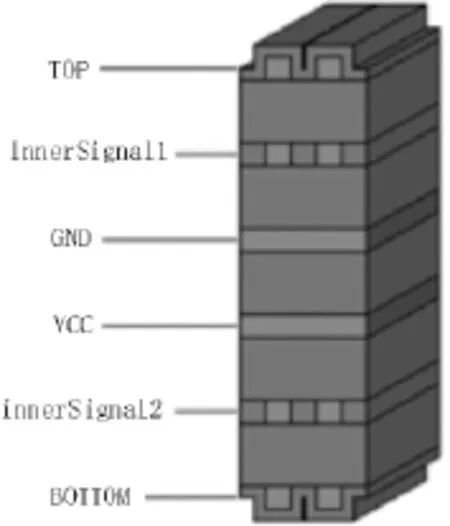

文中電路板的疊層設計如圖4所示,電路板層為6層,絕緣材料為FR4,相對介電常數在4.0至4.9之間,這里取4.3。

圖4 印制電路板疊層設計方案

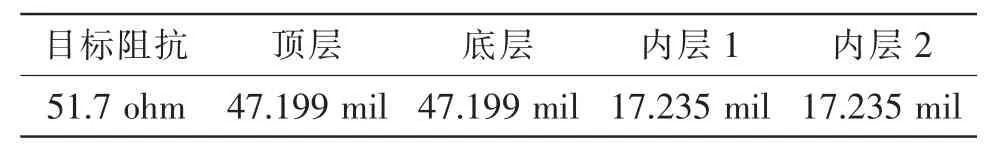

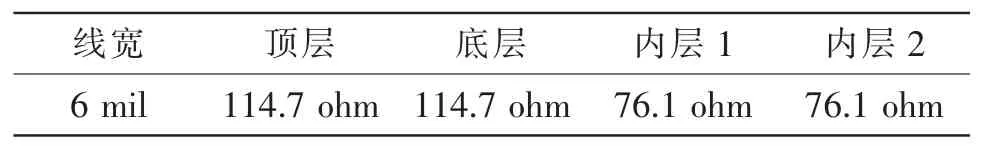

表1給出了目標阻抗值為51.7 ohm時各信號層的導線寬度計算值,頂層和底層導線寬度為47.199 mil,內部信號層為17.235 mil,導線過寬會導致電路面積并且影響布通率,因此通過傳輸線設計直接阻抗匹配的方案不可取。文中采取源端串行端接方案。當導線寬度設計為6 mil時各層互連線的阻抗值如表2所示。

表1 目標阻抗為51.7 ohm時不同布線層的信號線寬

表2 線寬6 mils情況下不同布線層的信號阻抗

采取源端串行端接方案時,需要保證驅動輸出阻抗與匹配阻抗的和等于傳輸線阻抗[13],因此當傳輸線布置在頂層和底層以及布置在中間2個信號時,匹配阻抗分別為:

頂層或底層:Z=Z0-ZS=114.7-51.7=63 ohm;

中間信號層:Z=76.1-51.7=24.4 ohm。

實施阻抗匹配后的信號完整性分析模型如圖5所示。

圖5 實施阻抗匹配后的SCLK信號完整性分析模型

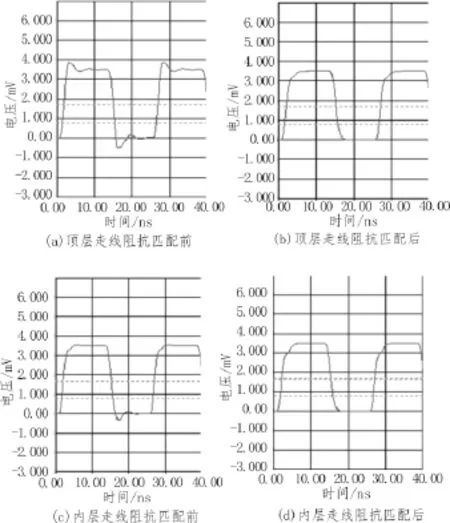

圖6是阻抗匹配實施前后的FPGA接收端仿真波形,傳輸線長度為5in,線寬6 mils,激勵源頻率為40 MHz,IC模型選擇Fast-strong,即選擇可能出現的最壞情況。可以看出,傳輸線無論布置在外層還是內部信號層,實施阻抗匹配后波形的信號完整性均有所改善。

圖6 阻抗匹配前后的波形對比

2.2 傳輸延遲

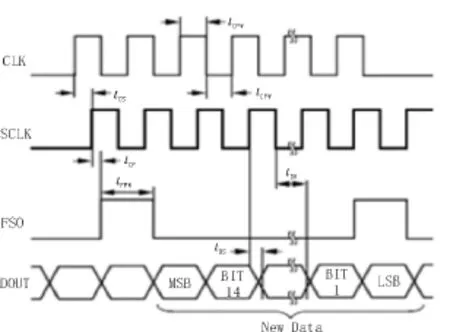

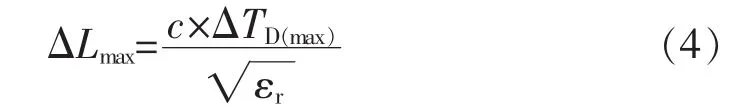

圖7為ADS1602的SPI總線信號之間嚴格的時序關系,其中tCF(SCLK上升沿至TCF上升沿之間的延時)與tDS(SCLK上升沿至有效數據的延時)最為嚴格,均為5 ns,如果考慮FPGA本身的邏輯時序延遲,則傳輸線之間的相對延遲還應該更小,本文預留了3 ns時間余量,可以估計出允許的最大的信號間的信號線長度差值。

圖7 ADS1602工作時序圖

式(4)給出了信號線長度與傳輸延遲之間的關系。其中,ΔLmax為最大允許傳輸線長度差;c為光速;ΔTD(max)為最大允許相對傳輸延遲,這里取 2 ns;εr為相對介電常數,這里取值4.3。根據上述參數可以得出信號線之間的最大長度差不能超過289 mm。

2.3 串 擾

串擾是指信號在傳輸線上傳輸時,產生的電磁場通過互容和互感對其它傳輸線產生耦合噪聲[14]。任何一對網絡之間都存在串擾,尤其相鄰網絡相互影響最大。文中將ADS1602的SCLK和DOUT這兩條相鄰網絡作為攻擊網絡和受害網絡進行分析,找出最佳設計準則。一般情況下,串擾約占信號擺幅的5%,本文中信號擺幅為3.3 V,因此最大串擾應小于165 mV。

串擾仿真原理圖如圖8所示。為了防止反射對串擾噪聲的干擾,攻擊網絡SCLK以及受害網絡DOUT都加入了匹配阻抗,其中受害網絡兩端都加上與導線特性阻抗相等的匹配阻抗。

圖8 串擾仿真模型

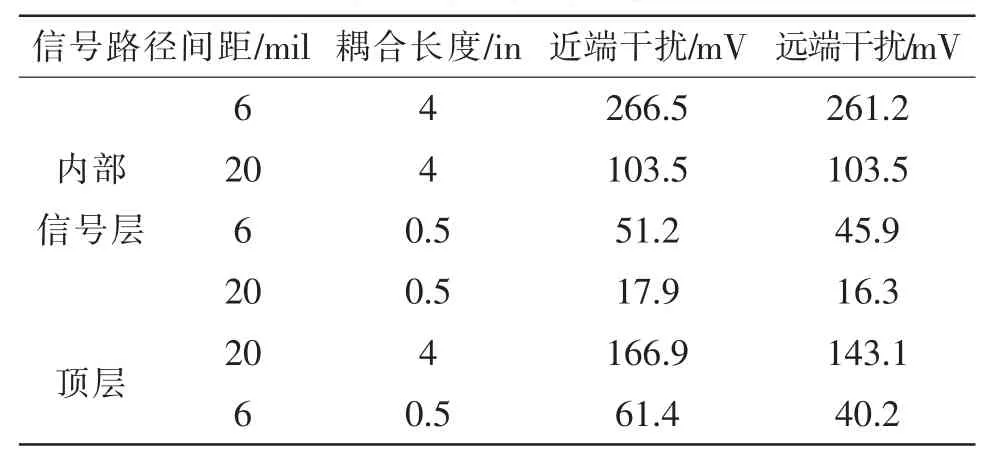

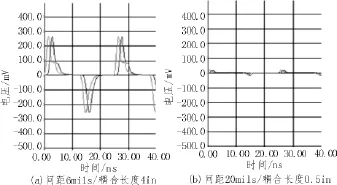

在攻擊網絡信號強度以及邊沿斜率一定的情況下,串擾噪聲主要與信號路徑間距、耦合長度以及信號所在層位置相關。表3給出了不同條件下仿真得到的近端串擾以及遠端串擾電壓幅值,圖9a和圖9b為其中串擾最大與最小的2個圖例。可以看出增大信號路徑間距以及減小信號耦合長度都能減小串擾幅值,并且耦合線在內部信號層時串擾值明顯小于外部信號層,這是因為內部信號層的有效介電常數大而延緩了信號速度的緣故。當然如果能采用帶狀線遠端串擾就不會出現[15]。

表3 串擾仿真結果

圖9 串擾仿真波形圖

根據仿真結果,可以采取以下走線策略:在近芯片端由于封裝限制,必須近距離并行走線,耦合長度不大于0.5 in,在遠芯片位置,信號路徑間距大于等于20 mil。

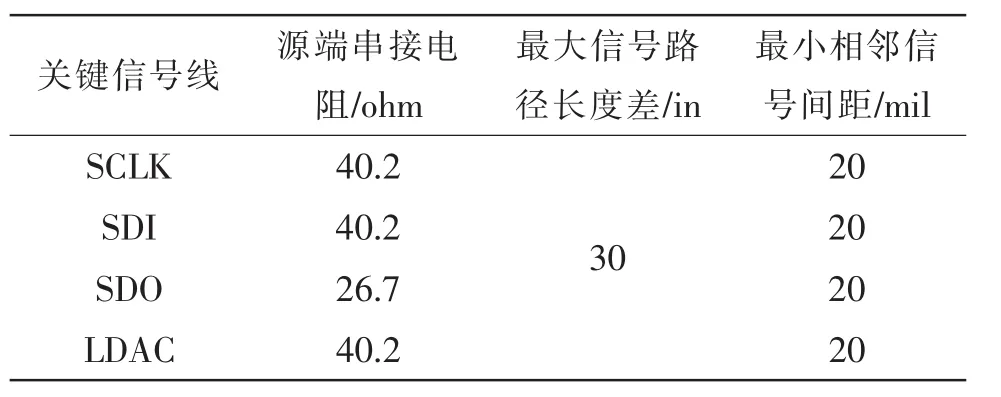

3 DAC9881的信號完整性設計

以與ADS1602同樣的分析方法,并基于TI公司官網提供的IBIS模型,對DAC9881與FPGA的互聯高速SPI總線進行了信號完整性分析,可以得出如表4所示的信號完整性加強策略。

表4 DAC9881的信號完整性加強策略

4 結 論

文中基于Hyperlynx仿真軟件,對快刀伺服控制器設計過程中的信號完整性問題進行了詳細的分析和研究,重點討論了 FPGA與高速 AD轉換器ADS1602以及FPGA與高速DA轉換器DAC9881之間的高速互聯SPI總線的反射,延遲以及串擾問題,為實際電路設計提供了量化的信號完整性增強措施。本文的研究過程和研究結果也能為類似的具有信號完整性問題的電路設計提供參考。

[1]Gui Lin Wang,Yi Fan Dai,Zi Wen Zhengetal. Machining Characteristics of Complex Surfaces Using Fast Tool Servo System [J].Machining Science and Technology,2011,15(3):324-337.

[2]萬飛.快刀伺服加工關鍵技術研究[D].長沙:國防科技大學,2010.

[3]ZhiweiZhu,XiaoqinZhou,Zhiwei Liuetal.Development of a piezoelectrically actuated two-degree-freedom fast tool servo with decoupled motions for micronanomachining [J].Precision Engineering,2014(38):809-820.

[4]竇婭錫.高速DAC與FPGA接口信號完整性的仿真分析[J].電子測量技術,2012,35(8):120-124.

[5]周潤景,景曉松.Mentor高速電路板設計與仿真[M].北京:電子工業出版社,2008.

[6]陳武,李克天,劉洪飛,等.基于壓電陶瓷驅動的快刀伺服系統的研制[J].制造技術與機床,2014(6): 43-47.

[7]林秩盛.信號與線性系統[M].北京:清華大學出版社,2008.

[8]朱文立,陳燕,郭遠東.電子電器產品電磁兼容質量控制與設計[M].北京:電子工業出版社,2015.

[9]Eric Bogatin.信號完整性分析[M].北京:電子工業出版社,2005.

[10]倪蕓.高速并行總線信號完整性分析[J].電子測量技術,2013,36(4):106-110.

[11]張海風.Hyperlynx仿真與PCB設計[M].北京:機械工業出版社,2005.

[12]Weng-Yew Chang,Wei-Shan So.Extraction of Clock Driver Output Impedance for Signal Integrity Design[J].IEEE Transactions on Electromagnetic Compatibility,2011,53(4):1034-1039.

[13]王娟.傳輸線上反射與串擾的仿真分析[J].合肥工業大學學報,2012,35(2):197-200.

[14]付兆靜.基于Hyperlynx的PCB板信號完整性分析[D].哈爾濱:哈爾濱工程大學,2013.

[15]靳皓,劉源,常若葵.基于Hyperlynx對串擾的研究[J].電子設計工程,2015,23(10):114-117.

Research of SI problems in the designing of FTS controler

LIU Guang-min,ZHANG Lian-xin,ZHANG Min,DAI Xiao-jing,HUANG Xiao-jin

(The Institute of Machinery Manufacturing Technology,China Academy of Engineering Physics,Mianyang 621900,China)

In the process of FTS controller design,The key technologies including Voltage feedback and The displacement feedback and High frequency analog voltage signal control,all these are realized based on ADC or DAC with High speed data bus.The controller performance Will be affected by the bad if the problems of signal integrity (SI)can't be solved vellwell.In order to achieve nicer SI performance,the SI problems for the core devices and the key signal path wereanalysed and researched In the simulation methods using software Hyperlynx in this paper.Research results can providedsome valuable references and guidance for The actual circuit design process.

FTS controler;SI;Hyperlynx;FPGA;ADS1602

TN02

A

1674-6236(2017)10-0069-05

2016-07-12稿件編號:201607095

國防基礎科研計劃資助項目(A1520133005);中物院超精密加工技術重點實驗室資助項目(ZZ13001)

劉廣民(1976—),男,四川綿陽人,碩士,工程師。研究方向:特種電源、電機驅動、嵌入式系統。