一種高精度低溫度系數帶隙基準源*

王文建

(浙江商業職業技術學院應用工程學院,杭州310053)

一種高精度低溫度系數帶隙基準源*

王文建*

(浙江商業職業技術學院應用工程學院,杭州310053)

通過相同材料電阻的比值來抵消帶隙基準源的一階溫度系數來達到低溫度系數,同時還設計了修調電路進一步提高基準電壓的精度。采用0.8 μm BiCMOS 9V工藝流片,帶隙基準源面積為0.035 mm2。結果表明:在-40 ℃~125 ℃范圍內,基準電壓的溫度系數為11×10-6/℃;電源電壓在4.5 V~9.0 V范圍內變化時,基準電壓的變化量為0.4 mV,電源調整率為0.09 mV/V。

溫度系數;修調電路;帶隙基準;電源調整率

在鋰電池充電管理集成電路中集成了對充放電過程中所有狀態的監測功能,包括涓流充電監測、恒定電流充電監測、恒定電壓充電監測,自動再充電監測、充電終止監測等,這些監測是需要精度很高溫度系數很低的參考電壓作為比較點,所以帶隙基準電壓的性能直接關系到集成電路的性能。這就對帶隙基準源的性能提出了更高的要求,包括高輸出精度、低溫度系數、低電源電壓調整率、高電源抑制比等[1-12]。

本文設計的帶隙基準源是通過相同材料電阻的比值來抵消帶隙基準源的一階溫度系數,獲得低溫度系數的基準電壓;同時設計了修調電路以進一步提高基準電壓精度,最后流片并給出測試結果。

1 電路實現

帶隙基準源圖如圖1所示,包括啟動電路和基準電壓產生電路。

1.1 啟動電路

如圖1所示,上電后,M1和M2導通,使得M4、M5、M6的柵極為低電平而導通,啟動電路開始工作。當基準電壓產生電路開始工作后,M1導通,M4、M5、M6的柵極拉到高電平,M4、M5、M6管截止,啟動電路停止工作。

圖1 帶隙基準源

1.2 基準電壓產生電路

如圖1所示,啟動電路停止工作后,M4、M5和M6處于截止狀態,此時由M8管提供電流。由于放大器的反饋作用,A和B點電位相同,流過Q1、Q2的電流相同。

Q2的發射極面積是Q1的8倍,所以流過R3的電流為:

(1)

設計中R3取60 kΩ,由此算出支路電流的值約為1.38 μA,與仿真結果一致。

(2)

兩邊對溫度求導有:

(3)

(4)

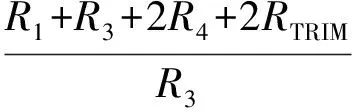

通過調整電阻比值可得到零溫度系數基準電壓。

圖2 修調電阻

1.3 修調電阻RTRIM

如圖2為修調電阻,通過調整修調電阻RTRIM,一方面可以調整溫度系數,另一方面也可以調整基準電壓的輸出精度;其中A、B、C、D為修調點,修調前修調點是通過鋁條連接的,把所并聯的電阻短掉。

根據式(2)得,修調前后的基準電壓值與VBE、電阻比值有關,因此修調前后的基準電壓值由修調前后的電阻比值確定,可以把這個比值作為修調測試的判據。

具體燒斷哪個修調點,根據表1查詢可知得。測試時,記下修調前的基準電壓值V0,然后用目標值1.225 0 V除以V0得到X值,表1中查找接近的X值,由X值確定燒斷哪個修調點。例如,設修調前的基準電壓值為1.210 0 V,則

查詢表1,序號4接近,需要修調A、B。

通過在修調點上加電流來燒斷鋁條。具體過程是:在修調點的一端PAD上加如圖3所示的電路,另一端PAD接地;在VCC端加電壓3 V,控制繼電器S1閉合30 ms。

圖3 修調點燒斷電路

序號修調點基準電壓值/VX12345678910111213141516不修調ABA、BCA、CB、CA、B、CDA、DB、DA、B、DC、DA、C、DB、C、DA、B、C、D1.20191.20511.20791.21101.21411.21691.22011.22291.22591.22911.23181.23501.23781.24091.24381.24691.01921.01651.01421.01161.00901.00671.00401.00170.99930.99670.99450.99190.98970.98720.98490.9824

圖4 芯片版圖

2 芯片版圖

圖4為鋰電池充電管理集成電路版圖,其中帶隙基準源面積為0.035 mm2。集成電路采用0.8 μm BiCMOS 9 V工藝進行制作。

3 測試結果及分析

鋰電池充電管理集成電路采用0.8 μm BiCMOS 9 V工藝進行流片,對帶隙基準源進行了測試。

測試工具:穩壓電源(精度為0.1 V)、示波器(兩種帶寬輸入,不同帶寬探頭具有不同寄生電容)、加熱爐、冷柜、萬用表(電壓精確度為0.1 mV~1 mV,電流精確度為0.1 μA)等。

圖5為基準電壓隨電源電壓VCC變化曲線。電源電壓VCC在4.5 V~9.0 V變化時,基準電壓VREF的變化量約為0.4 mV,電源調整率為0.09 mV/V。

圖5 基準電壓隨電源電壓變化曲線

圖6為基準電壓VREF溫度特性曲線。在6.0 V電源電壓下,在-40 ℃~125 ℃溫度范圍內的溫度系數為11×10-6/℃。

圖6 基準電壓溫度特性曲線

圖7為帶隙基準源的電源抑制特性曲線,在低頻(小于1 kHz)時為-74 dB。

圖7 帶隙基準源電源抑制特性曲線

4 結束語

為了適應鋰電池充電管理集成電路對帶隙基準源精度的要求,設計了一種高精度低溫度系數帶隙基準源。該帶隙基準源是通過相同材料電阻的比值來抵消帶隙基準源的一階溫度系數,獲得低溫度系數的基準電壓;還設計了修調電路進一步提高基準電壓的輸出精度;使得輸出的基準電壓的精度和溫度系數有了很大改善。鋰電池充電管理集成電路采用0.8 μm BiCMOS 9 V工藝進行流片,帶隙基準源所占面積為0.035 mm2。測試結果表明:在6 V電源電壓下,在-40 ℃~125 ℃溫度范圍內的溫度系數為11×10-6/℃;電源電壓在4.5 V~9.0 V范圍內變化時,基準電壓的變化量為0.4 mV,電源調整率為0.09 mV/V;在電源電壓6 V時,帶隙基準源的電源抑制比在低頻(小于1 kHz)時為-74 dB。該設計的帶隙基準源可廣泛應用于電源管理類集成電路中,具有較高的參考價值。

[1] 高獻坤,雷君召,丁赪璐,等. 高電源抑制比、低溫漂帶隙基準電壓源的設計[J]. 河南農業大學學報,2011,45(4):442-444.

[2] 胡佳俊,陳后鵬,蔡道林,等. 高電源抑制比低溫漂帶隙基準源設計[J]. 微電子學,2012,42(1):34-37.

[3] 張萬東,陳宏,王一鵬,等. 高電源抑制比和高階曲率補償帶隙基準源[J]. 微電子學,2011,41(1):57-60.

[4] 楊寧,史儀凱,袁小慶,等. 高精度、低功耗帶隙基準源及其電流源設計[J]. 傳感技術學報,2014,27(1):58-63.

[5] 黎官華,王衛東. 高刷新率高穩定性LED恒流驅動電路的設計[J]. 電子器件,2015,38(3):531-537.

[6] 徐星,袁紅輝,陳世軍,等. 高性能CMOS帶隙基準電壓源及電流源的設計[J]. 半導體技術,2011,36(3):229-233.

[7] 李沁蓮,陳向東,王麗萍,等. 基于襯底運放的2階溫度補償帶隙基準電路[J]. 微電子學,2011,41(3):332-335.

[8] 吳金,聶衛東,常昌遠,等. 基于失配控制的非線性補償帶隙基準電路設計[J]. 東南大學學報(自然科學版),2011,41(5):917-922.

[9] 李睿,馮全源. 一種低功耗高精度帶隙基準的設計[J]. 電子技術應用,2015,41(3):51-54.

[10] 朱彤,黃飛,謝森,等. 一種低溫度系數高驅動能力的帶隙基準電路[J]. 微電子學,2011,41(4):545-549.

[11] 唐寧,李佐,李琦. 一種改進的非線性匹配高階補償基準源的設計[J]. 電子器件,2013,36(6):797-801.

[12] 楊金,代月花,宗桂林,等. 一種高電源抑制比低溫漂系數帶隙基準電路[J]. 微電子學,2014,44(3):297-300.

AHighPrecisionLowTemperatureCoefficientBandgapReference*

WANGWenjian*

(Applied Engineering College,Zhejiang College of Business,Hangzhou 310053,China)

By the same material resistance ratio to offset the bandgap of the first order temperature coefficient a low temperature coefficient is achieved,and the trim circuit is also designed to further improve the accuracy of the reference voltage. Used 0.8 μm BiCMOS 9 V process flow sheet,the bandgap reference area is 0.035 mm2. Test results show that in the temperature range of -40 ℃~125 ℃,the temperature coefficient of the reference voltage is 11×10-6/℃;when the power supply voltage variation is within the range of 4.5 V~9.0 V,the reference voltage variation is 0.4 mV,power adjustment rate 0.09 mV/V.

temperature coefficient;trim circuit;bandgap reference;power adjustment rate

10.3969/j.issn.1005-9490.2017.05.003

項目來源:浙江省科技廳公益技術應用研究計劃項目(2017C31077);浙江省教育廳科研項目(Y201635565)

2016-08-16修改日期2016-10-28

TN432

A

1005-9490(2017)05-1065-03

王文建(1973-),男,碩士,高級工程師,從事電源管理和數模混合集成電路設計和研究,540843839@qq.com。